# ZDV4(5)256M16

4Gb DDR3(L) SDRAM Datasheet

<sup>\*</sup> Information furnished is believed to be accurate and reliable. However, Zetta assumes no responsibility for the consequences of use of such information or for any infringement of patents of other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Zetta. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. Zetta products are not authorized for use as critical components in life support devices or systems without express written approval of Zetta. The Zetta logo is a registered trademark of Zetta Device Technology Limited. All other names are the property of their respective own.

#### **4GBIT DDR3 DRAM**

## **Key Features**

VDD=VDDQ=1.5V(1.425V~1.575V)

VDD=VDDQ=1.35V(1.28V~1.45V), backward compatible to 1.5V applications.

- 8 banks

- 8n-bit prefetch architecture

- Fully differential clock inputs (CK, CK) operation

- Bi-directional differential data strobe (DQS,DQS)

- On chip DLL align DQ, DQS and DQS transition With CK transition

- DM masks write data-in at the both rising and falling edges of the data strobe

- All addresses and control inputs except data, data strobes and data masks latched on the rising edges of the clock

- Programmable CAS latency 5, 6, 7, 8, 9, 10, 11, 12,

13, 14 supported

- Programmable additive latency 0, CL-1, and CL-2 supported

- Programmable CAS Write latency (CWL) = 5, 6, 7, 8, 9, 10

- Programmable burst length 4/8 with both nibble sequential and interleave mode

- BL switch on the fly

- Driver strength selected by MRS

- Dynamic On Die Termination

- Asynchronous RESET pin

- Internal (self) calibration: Internal self calibration through ZQ pin (RZQ: 240 ohm ± 1%)

- TDQS (Termination Data Strobe) supported (x8 only)

- Write leveling

- Self refresh temperature (SRT)

- Automatic self refresh (ASR)

- JEDEC standard package

- 96ball FBGA(x16)

- Lead free & RoHS compliant

- JEDEC compliant

- Operating Temperature (Tcase)

- Commercial -C (0°C  $\leq$  T<sub>C</sub>  $\leq$  85°C)

- Industrial -I (-40°C  $\leq$  T<sub>C</sub>  $\leq$  85°C)

| Smood       | 1600     | 1866     | 2133     | Unit |

|-------------|----------|----------|----------|------|

| Speed       | 11-11-11 | 13-13-13 | 14-14-14 | Onit |

| tCK(min)    | 1.25     | 1.071    | 0.938    | ns   |

| CAS Latency | 11       | 13       | 14       | nCK  |

| tRCD(min)   | 13.75    | 13.91    | 13.09    | ns   |

| tRP(min)    | 13.75    | 13.91    | 13.09    | ns   |

| tRAS(min)   | 35       | 34       | 33       | ns   |

| tRC(min)    | 48.75    | 47.91    | 46.09    | ns   |

#### Note

The functionality described and the timing specifications included in this data sheet are for the DLL Enabled mode of operation.

## **Descriptions**

The 4Gb Double-Data-Rate-3 (DDR3(L)) DRAM is a high-speed CMOS SDRAM. It is internally configured as an octal-bank DRAM.

The 4Gb chip is organized as 32Mbit x16 I/O x 8 banks. These synchronous devices achieve high speed double-data-rate transfer rates of up to 2133 Mb/sec/pin for general applications.

The chip is designed to comply with all key DDR3(L) DRAM key features and all of the control and address inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the cross point of differential clocks (CK rising and CK falling). All I/Os are synchronized with a single ended DQS or differential DQS pair in a source synchronous fashion.

These devices operate with a single  $1.5V \pm 0.075V$  or 1.35V - 0.067V / + 0.1V power supply and are available in BGA packages.

## **Addressing**

| Configuration        | 512Mb x 8                                       | 256Mb x 16 |  |  |

|----------------------|-------------------------------------------------|------------|--|--|

| Number of Bank       | 8                                               | 8          |  |  |

| Bank address         | BA0-BA2                                         | BA0-BA2    |  |  |

| Autoprecharge        | A10/AP                                          | A10/AP     |  |  |

| Row address          | A0-A15                                          | A0-A14     |  |  |

| Column address       | A0-A9                                           | A0-A9      |  |  |

| BC switch on the fly | A12/BC                                          | A12/BC     |  |  |

| Page Size            | 1KB                                             | 2KB        |  |  |

| tREFI                | Tc ≦ 85°C : 7.8μs,<br>85°C < Tc ≦ 105°C : 3.9μs |            |  |  |

| tRFC                 | 260                                             | )ns        |  |  |

#### **Package**

| 4Gb<br>(Org. / Package) |                      | Dimension<br>(mm) | Ball pitch<br>(mm) |

|-------------------------|----------------------|-------------------|--------------------|

| 512Mbx8                 | 512Mbx8 78-ball FBGA |                   | 0.80               |

| 256Mbx16                | 96-ball FBGA         | 9 x 13            | 0.80               |

# **Ordering Information**

|              | Part No.          |                       | Speed            |             |         |

|--------------|-------------------|-----------------------|------------------|-------------|---------|

| Organization |                   | Clock (MHz)           | Data Rate (Mb/s) | CL-TRCD-TRP | Package |

|              | DDR3(L)           | Commercial Grade      | (-C, 0°C ~ 85°C) |             |         |

|              | ZDV4256M16A-14DPH | 1066                  | DDR3L-2133       | 14-14-14    |         |

|              | ZDV4256M16A-13DPH | 933                   | DDR3L-1866       | 13-13-13    |         |

| 05014-40     | ZDV4256M16A-11DPH | 800                   | DDR3L-1600       | 11-11-11    | 00 - 1  |

| 256Mx16      | ZDV5256M16A-14DPH | 1066                  | DDR3-2133        | 14-14-14    | 96-ball |

|              | ZDV5256M16A-13DPH | 933                   | DDR3-1866        | 13-13-13    |         |

|              | ZDV5256M16A-11DPH | 800                   | DDR3-1600        | 11-11-11    |         |

|              | DDR3(L            | ) Industrial Grade (- | I, -40°C ~ 85°C) |             |         |

|              | ZDV4256M16A-14IPH | 1066                  | DDR3L-2133       | 14-14-14    |         |

|              | ZDV4256M16A-13IPH | 933                   | DDR3L-1866       | 13-13-13    |         |

| 256Mx16      | ZDV4256M16A-11IPH | 800                   | DDR3L-1600       | 11-11-11    | 96-ball |

|              | ZDV5256M16A-14IPH | 1066                  | DDR3-2133        | 14-14-14    | 96-ball |

|              | ZDV5256M16A-13IPH | 933                   | DDR3-1866        | 13-13-13    |         |

|              | ZDV5256M16A-11IPH | 800                   | DDR3-1600        | 11-11-11    |         |

# X16 Package Ballout (Top View): 96ball FBGA Package

| Α |  |

|---|--|

| В |  |

| С |  |

| D |  |

| E |  |

| F |  |

| G |  |

| Н |  |

| J |  |

| K |  |

| L |  |

| M |  |

| N |  |

| Р |  |

| R |  |

| Т |  |

| 1      | 2     | 3    | 4 | 5 | 6 | 7      | 8      | 9    |   |   |

|--------|-------|------|---|---|---|--------|--------|------|---|---|

|        |       |      | 1 |   |   |        | T      |      | ī |   |

| VDDQ   | DQU5  | DQU7 |   |   |   | DQU4   | VDDQ   | VSS  |   | Α |

| VSSQ   | VDD   | vss  |   |   |   | DQSU   | DQU6   | VSSQ |   | В |

| VDDQ   | DQU3  | DQU1 |   |   |   | DQSU   | DQU2   | VDDQ |   | С |

| VSSQ   | VDDQ  | DMU  |   |   |   | DQU0   | VSSQ   | VDD  |   | D |

| vss    | VSSQ  | DQL0 |   |   |   | DML    | VSSQ   | VDDQ |   | Е |

| VDDQ   | DQL2  | DQSL |   |   |   | DQL1   | DQL3   | VSSQ |   | F |

| VSSQ   | DQL6  | DQSL |   |   |   | VDD    | vss    | VSSQ |   | G |

| VREFDQ | VDDQ  | DQL4 |   |   |   | DQL7   | DQL5   | VDDQ |   | Н |

| NC     | vss   | RAS  |   |   |   | СК     | vss    | NC   |   | J |

| ODT    | VDD   | CAS  |   |   |   | СК     | VDD    | CKE  |   | K |

| NC     | CS    | WE   |   |   |   | A10/AP | ZQ     | NC   |   | L |

| vss    | BA0   | BA2  |   |   |   | NC     | VREFCA | vss  |   | М |

| VDD    | А3    | A0   |   |   |   | A12/BC | BA1    | VDD  |   | N |

| vss    | A5    | A2   |   |   |   | A1     | A4     | vss  |   | Р |

| VDD    | A7    | A9   |   |   |   | A11    | A6     | VDD  |   | R |

| vss    | RESET | A13  |   |   |   | A14    | A8     | VSS  |   | Т |

| 1      | 2     | 3    | 4 | 5 | 6 | 7      | 8      | 9    |   |   |

Top View: See the balls through the Package

|                                 | 1 2 3                                   | 7 8 9                                                             |  |

|---------------------------------|-----------------------------------------|-------------------------------------------------------------------|--|

| A B C D E F G H J K L M N P R T | 000000000000000000000000000000000000000 | 000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>00 |  |

Populated ballBall not populated

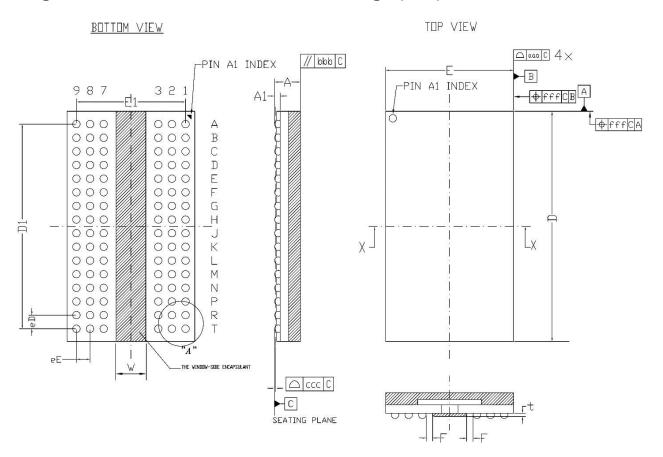

## Packge Dimensions – 96 balls BGA Package (x16)

| DEE  |           | nsion in | mm    |  |  |

|------|-----------|----------|-------|--|--|

| REF. | MIN.      | N□M.     | MAX.  |  |  |

| Α    |           |          | 1.20  |  |  |

| A1   | 0.25      |          | 0.40  |  |  |

| b    | 0.40      | 0.45     | 0.50  |  |  |

| D    | 12.90     | 13.00    | 13.10 |  |  |

| E    | 8,90      | 9.00     | 9.10  |  |  |

| D1   | 12.00 BSC |          |       |  |  |

| E1   | 6.40 BSC  |          |       |  |  |

| еE   | 0.80 BSC  |          |       |  |  |

| еD   | 0,80 BSC  |          |       |  |  |

| aaa  |           |          | 0.15  |  |  |

| bbb  |           |          | 0.20  |  |  |

| CCC  |           |          | 0.12  |  |  |

| ddd  |           |          | 0.15  |  |  |

| 666  | 0.08      |          |       |  |  |

| F    | 0.1       |          |       |  |  |

| t    |           |          | 0.20  |  |  |

| W    |           |          | 2.00  |  |  |

## **Pin Functions**

| Symbol         | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK         | Input | Clock: CK and CK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Ort, Ort       |       | and negative edge of $\overline{CK}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CKE            | Input | Clock Enable: CKE high activates, and CKE low deactivates, internal clock signals and device input buffers and output drivers. Taking CKE low provides Precharge Power-Down and Self-Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is synchronous for power down entry and exit and for Self-Refresh entry. CKE is asynchronous for Self-Refresh exit. After VREF has become stable during the power on and initialization sequence, it must be maintained for proper operation of the CKE receiver. For proper self-refresh entry and exit, VREF must maintain to this input. CKE must be maintained high throughout read and write accesses. Input buffers, |

|                |       | excluding CK, CK, ODT and CKE are disabled during Power Down. Input buffers, excluding CKE, are disabled during Self-Refresh.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CS             | Input | Chip Select: All commands are masked when $\overline{CS}$ is registered high. provides for external rank selection on systems with multiple memory ranks. $\overline{CS}$ is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | Innut |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RAS, CAS, WE   | Input | RAS , CAS , WE (along with CS) define the command being Input Data Mask : DM is an input mask signal for write data. Input data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DM, (DMU, DML) | Input | is masked when DM is sampled HIGH coincident with that input data during a Write access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BA0 ~ BA2      | Input | Bank Address Inputs: BA0, BA1, and BA2 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines which mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A10 / AP       | Input | Auto-Precharge: A10 is sampled during Read/Write commands to determine whether Autoprecharge should be performed to the accessed bank after the Read/Write operation. (HIGH: Autoprecharge; LOW: no Autoprecharge). A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by bank addresses.                                                                                                                                                                                                                                                                  |

|                |       | Address Inputs: Provide the row address for Activate commands and the column address for Read/Write commands to select one location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A0 ~ A15       | Input | out of the memory array in the respective bank. (A10/AP and A12, BC have additional function as below.) The address inputs also provide the op-code during Mode Register Set commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A12, BC        | Input | Burst Chop: A12, BC is sampled during Read and Write commands to determine if burst chop (on the fly) will be performed. (HIGH - no burst chop; LOW - burst chopped).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                |       | On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR3 SDRAM. When enabled, ODT is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ODT            | Input | applied to each DQ, DQS, DQS and DM, TDQS, NU, TDQS (when TDQS is enabled via Mode Register A11=1 in MR1) signal for x8 configurations. The ODT pin will be ignored if Mode-registers, MR1and MR2, are programmed to disable RTT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Symbol                                          | Туре         | Function                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                                           |              | Active Low Asynchronous Reset: Reset is active when RESET is LOW, and inactive when RESET is HIGH. RESET must be HIGH during normal operation. RESET is a CMOS rail to rail signal with DC high and low at 80% and 20% of VDD, i.e. 1.20V for DC high and 0.30V                                                                                                                                |

| DQ                                              | Input/Output | Data Inputs/Output: Bi-directional data bus.                                                                                                                                                                                                                                                                                                                                                   |

| DQL, DQU, DQS, (DQS) DQSL, (DQSL), DQSU, (DQSU) | I            | Data Strobe: output with read data, input with write data. Edge aligned with read data, centered with write data. The data strobes DQS, DQSL, DQSU are paired with differential signals DQS, DQSL, DQSU, respectively, to provide differential pair signaling to the system during both reads and writes. DDR3 SDRAM supports differential data strobe only and does not support single-ended. |

| TDQS,(TDQS)                                     | Output       | TDQS and TDQS is applicable for ×8 configuration only. When enabled via mode register A11 = 1 in MR1, DRAM will enable the same termination resistance function on TDQS, TDQS as is applied to DQS, DQS. When disabled via mode register A11 = 0 in MR1, DM/TDQS will provide the data mask function and TDQS is not used.                                                                     |

| NC                                              | -            | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                      |

| VDDQ                                            | Supply       | DQ Power Supply: 1.35V -0.067V/+0.1V or 1.5V ± 0.075V                                                                                                                                                                                                                                                                                                                                          |

| VDD                                             | Supply       | Power Supply: 1.35V -0.067V/+0.1V or 1.5V ± 0.075V                                                                                                                                                                                                                                                                                                                                             |

| VSSQ                                            | Supply       | DQ Ground                                                                                                                                                                                                                                                                                                                                                                                      |

| VSS                                             | Supply       | Ground                                                                                                                                                                                                                                                                                                                                                                                         |

| VREFCA                                          | Supply       | Reference voltage for CA                                                                                                                                                                                                                                                                                                                                                                       |

| VREFDQ                                          | Supply       | Reference voltage for DQ                                                                                                                                                                                                                                                                                                                                                                       |

| ZQ                                              | Supply       | Reference pin for ZQ calibration.                                                                                                                                                                                                                                                                                                                                                              |

Note: Input only pins (BA0-BA2, A0-A14,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$ ,  $\overline{CS}$ , CKE, ODT, and  $\overline{RESET}$ ) do not supply termination.

## **Absolute Maximum Ratings**

## **Absolute Maximum DC Ratings**

| Symbol    | Parameters                                  | Rating     | Unit | Note |

|-----------|---------------------------------------------|------------|------|------|

| VDD       | Voltage on VDD pin relative to VSS          | -0.4 ~ 1.8 | V    | 1,3  |

| VDDQ      | Voltage on VDDQ pin relative to VSS         | -0.4 ~ 1.8 | V    | 1,3  |

| VIN, VOUT | Voltage on input/output pin relative to VSS | -0.4 ~ 1.8 | V    | 1    |

| TSTG      | Storage Temperature                         | -55 ~ 100  | °C   | 1,2  |

#### Notes:

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Storage Temperature is the case surface temperature on the center/top side of the DRAM.

- 3. VDD and VDDQ must be within 300mV of each other at all times; and Vref must be not greater than 0.6VDDQ, when VDD and VDDQ are less than 500mV; Vref may be equal to or less than 300mV.

### Refresh parameters by device density

| Parameter                              | Symbol | 1Gb | 4Gb | 4Gb | 8Gb | Unit |

|----------------------------------------|--------|-----|-----|-----|-----|------|

| REF command to ACT or REF command time | tRFC   | 110 | 160 | 260 | 350 | ns   |

## **Temperature Range**

| Symbol          | Parameters                         | Rating           | Unit | Note |

|-----------------|------------------------------------|------------------|------|------|

| Commercial (C)  | Normal Operating Temperature Range | 0 ≤ Toper ≤ 85   | °C   | 1    |

| Commercial (-C) | Extended Temperature Range         | 85 < Toper ≤ 95  | °C   | 1,2  |

| Industrial ( I) | Normal Operating Temperature Range | -40 ≤ Toper ≤ 85 | °C   | 1    |

| Industrial (-I) | Extended Temperature Range         | 85 < Toper ≤ 95  | °C   | 1,2  |

#### Notes:

- 1. Operating Temperature Toper is the case surface temperature on the center/top side of the DRAM.

- 2. Some applications require operation of the DRAM in the Extended Temperature Range between 85°C and 95°C case temperature. Full specifications are guaranteed in this range, but the following additional apply:

- a) Refresh commands must be doubled in frequency, therefore, reducing the Refresh interval tREFI to 3.9us.

- b) If Self-Refresh operation is required in the Extended Temperature Range, then it is mandatory to either use the Manual Self-Refresh mode with Extended Temperature Range capability (MR2 A6=0 and MR2 A7=1) or enable the optional Auto Self-Refresh mode (MR2 A6=1 and MR2 A7=0).

## **AC & DC Operating Conditions**

## **Recommended DC Operating Conditions**

| 0                 | D                              |       | Rating |      |       |      | N       |  |

|-------------------|--------------------------------|-------|--------|------|-------|------|---------|--|

| Symbol Parameters |                                | Min.  | Тур.   | Max. | Unit  | Note |         |  |

|                   | VDD Supply Voltage             | DDR3  | 1.425  | 1.5  | 1.575 | V    | 1,2     |  |

| VDD               |                                | DDR3L | 1.283  | 1.35 | 1.45  |      | 3,4,5,6 |  |

| \/DD0             | VDDQ Supply Voltage for Output | DDR3  | 1.425  | 1.5  | 1.575 | V    | 1,2     |  |

| VDDQ              |                                | DDR3L | 1.283  | 1.35 | 1.45  |      | 3,4,5,6 |  |

#### Notes:

- 1. Under all conditions VDDQ must be less than or equal to VDD.

- 2. VDDQ tracks with VDD. AC parameters are measured with VDD and VDDQ tied together

- 3. Maximum DC value may not be great than 1.425V. The DC value is the linear average of VDD/ VDDQ(t) over a very long period of time (e.g., 1 sec).

- 4. If maximum limit is exceeded, input levels shall be governed by DDR3 specifications.

- 5. Under these supply voltages, the device operates to this DDR3L specification.

- 6. Once initialized for DDR3 operation, DDR3L operation may only be used if the device is in reset while VDD and VDDQ are changed for DDR3L operation.

- 7. VDD= VDDQ= 1.35V (1.283–1.45V) Backward compatible to VDD= VDDQ= 1.5V ±0.075V Supports DDR3L devices to be backward com-partible in 1.5V applications.

# IDD Specifications and Measurement Conditions IDD Specifications (DDR3L)

| Symbol              | Parameter                                                   | Width | DDR3L-1600<br>11-11-11 | DDR3L-1866<br>13-13-13 | DDR3L-2133<br>14-14-14 | Units |

|---------------------|-------------------------------------------------------------|-------|------------------------|------------------------|------------------------|-------|

| 11 )1 )()           | Operating Current 0 One Bank Activate -> Precharge          | x8    | 100                    | 120                    | 130                    | mA    |

|                     |                                                             | x16   | 110                    | 130                    | 150                    | mA    |

|                     | Operating Current 1                                         | x8    | 110                    | 125                    | 135                    | mA    |

| IDD1                | One Bank Activate -> Read -> Precharge                      | x16   | 120                    | 135                    | 155                    | mA    |

| IDD2P0              | Precharge Power-Down Current<br>Slow Exit - MR0 bit A12 = 0 | x8    | 20                     | 20                     | 20                     | mA    |

| IDDZPU              |                                                             | x16   | 22                     | 22                     | 22                     | mA    |

| IDD2D4              | Precharge Power-Down Current                                | x8    | 43                     | 45                     | 47                     | mA    |

| IDD2P1              | Fast Exit - MR0 bit A12 = 1                                 | x16   | 45                     | 47                     | 49                     | mA    |

| IDD3O               | Brookerge Quiet Standby Current                             | x8    | 58                     | 63                     | 68                     | mA    |

| IDD2Q               | Precharge Quiet Standby Current                             | x16   | 60                     | 65                     | 70                     | mA    |

| IDD2N               | Dunahanna Chandhu Cumant                                    | x8    | 61                     | 66                     | 71                     | mA    |

| IDDZN               | Precharge Standby Current                                   | x16   | 63                     | 68                     | 73                     | mA    |

| IDD 0::-            | Precharge Standby ODT Current                               | x8    | 83                     | 90                     | 96                     | mA    |

| IDD2NT              |                                                             | x16   | 85                     | 92                     | 96                     | mA    |

| IDD3N               | Active Standby Current                                      | x8    | 88                     | 96                     | 100                    | mA    |

| IDDSN               |                                                             | x16   | 90                     | 100                    | 105                    | mA    |

| IDD3P               | Active Power-Down Current<br>Always Fast Exit               | x8    | 68                     | 77                     | 82                     | mA    |

| IDD3F               |                                                             | x16   | 70                     | 80                     | 85                     | mA    |

| IDD4R               | Operating Current Burst Read                                | x8    | 180                    | 210                    | 230                    | mA    |

| IDD4N               |                                                             | x16   | 190                    | 220                    | 240                    | mA    |

| IDD4W               | Operating Current Burst Write                               | x8    | 200                    | 240                    | 265                    | mA    |

| 100411              |                                                             | x16   | 210                    | 250                    | 280                    | mA    |

| IDD5B               | Burst Refresh Current                                       | x8    | 170                    | 185                    | 200                    | mA    |

| 10036               |                                                             | x16   | 180                    | 195                    | 210                    | mA    |

| IDD6 <sup>1</sup>   | Self-Refresh Current<br>Normal                              | x8    | 25                     | 25                     | 25                     | mA    |

| וטטט                |                                                             | x16   | 25                     | 25                     | 25                     | mA    |

| IDD6ET <sup>2</sup> | Self-Refresh Current<br>Extended                            | x8    | 28                     | 28                     | 28                     | mA    |

|                     |                                                             | x16   | 28                     | 28                     | 28                     | mA    |

| IDD7                | All Bank Interleave Read Current                            | x8    | 220                    | 255                    | 275                    | mA    |

| וטטו                |                                                             | x16   | 240                    | 270                    | 290                    | mA    |

| IDD8                | RESET Low Current                                           | x8    | 21                     | 21                     | 22                     | mA    |

| אטטו                | NESET LOW GUITERIL                                          | x16   | 23                     | 23                     | 24                     | mA    |

#### Notes

<sup>1.</sup> Tc = 85°C; SRT and ASR are disabled.

<sup>2.</sup> Enabling ASR could increase IDDx by up to an additional 2mA.

<sup>3.</sup> Restricted to TC (MAX) = 85°C.

<sup>4.</sup> Tc = 85°C; ASR and ODT are disabled; SRT is enabled.

# IDD Specifications and Measurement Conditions IDD Specifications (DDR3)

| Symbol         | Parameter                                 | Width | DDR3-1600<br>11-11-11 | DDR3-1866<br>13-13-13 | DDR3-2133<br>14-14-14 | Unit |

|----------------|-------------------------------------------|-------|-----------------------|-----------------------|-----------------------|------|

| IDD0           | Operating Current 0                       | x8    | 100                   | 120                   | 130                   | mA   |

| טטטו           | One Bank Activate -> Precharge            | x16   | 110                   | 130                   | 150                   | mA   |

|                | Operating Current 1                       | x8    | 110                   | 125                   | 135                   | mA   |

| IDD1           | One Bank Activate -> Read -<br>>Precharge | x16   | 120                   | 135                   | 155                   | mA   |

| IDD2P0         | Precharge Power-Down Current              | x8    | 20                    | 20                    | 20                    | mA   |

| IDDZI 0        | Slow Exit - MR0 bit A12 = 0               | x16   | 22                    | 22                    | 22                    | mA   |

| IDD2P1         | Precharge Power-Down Current              | x8    | 43                    | 45                    | 47                    | mA   |

| IDD2F I        | Fast Exit - MR0 bit A12 = 1               | x16   | 45                    | 47                    | 49                    | mA   |

| IDD2Q          | Donald Character of Community             | x8    | 58                    | 63                    | 68                    | mA   |

| IDDZQ          | Precharge Quiet Standby Current           | x16   | 60                    | 65                    | 70                    | mA   |

| IDDON          | Precharge Standby Current                 | x8    | 61                    | 66                    | 71                    | mA   |

| IDD2N          |                                           | x16   | 63                    | 68                    | 73                    | mA   |

| IDDONIT        | D                                         | x8    | 83                    | 90                    | 96                    | mA   |

| IDD2NT         | Precharge Standby ODT Current             | x16   | 85                    | 92                    | 98                    | mA   |

| IDDON          | Active Standby Current                    | x8    | 88                    | 96                    | 100                   | mA   |

| IDD3N          |                                           | x16   | 90                    | 100                   | 105                   | mA   |

| IDDAD          | Active Power-Down Current                 | x8    | 68                    | 77                    | 82                    | mA   |

| IDD3P          | Always Fast Exit                          | x16   | 70                    | 80                    | 85                    | mA   |

| IDD 4D         | Operating Current Burst Read              | x8    | 180                   | 210                   | 230                   | mA   |

| IDD4R          |                                           | x16   | 190                   | 220                   | 240                   | mA   |

| IDD4W          | Operating Current Burst Write             | x8    | 200                   | 240                   | 265                   | mA   |

|                |                                           | x16   | 210                   | 250                   | 280                   | mA   |

| IDD5B B        | Burst Refresh Current                     | x8    | 170                   | 185                   | 200                   | mA   |

|                |                                           | x16   | 180                   | 195                   | 210                   | mA   |

| 113136 '       | Self-Refresh Current<br>Normal            | x8    | 25                    | 25                    | 25                    | mA   |

|                |                                           | x16   | 25                    | 25                    | 25                    | mA   |

| 11 )1 )6 + 1 + | Self-Refresh Current<br>Extended          | x8    | 28                    | 28                    | 28                    | mA   |

|                |                                           | x16   | 28                    | 28                    | 28                    | mA   |

| 1007           |                                           | x8    | 220                   | 255                   | 275                   | mA   |

| IDD7           | All Bank Interleave Read Current          | x16   | 240                   | 270                   | 290                   | mA   |

| IDDA           | DECET Law Comment                         | x8    | 21                    | 21                    | 22                    | mA   |

| IDD8           | RESET Low Current                         | x16   | 23                    | 23                    | 24                    | mA   |

#### Notes

- 1. Tc = 85°C; SRT and ASR are disabled.

- 2. Enabling ASR could increase IDDx by up to an additional 2mA.

- 3. Restricted to TC (MAX) = 85°C.

- 4. Tc = 85°C; ASR and ODT are disabled; SRT is enabled.

# **Revision History**

| Revision | Date       | Page  | Notes              |

|----------|------------|-------|--------------------|

| 0.1      | Nov., 2020 | -     | Preliminary        |

| 1.0      | Dec., 2020 | 12~13 | IDDx value updated |

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for DRAM category:

Click to view products by Zetta manufacturer:

Other Similar products are found below:

M366S0924FTS-C7A00 AS4C16M32MD1-5BCN HM514100AZ-80 K4S560432C-TC75 K4S641632H-UC60 SH2567MU325816HEV

AS4C16M32MD1-5BIN AS4C64M8D1-5TCN ATCA-7360-MEM-4G MN41C4256A-07 MT48LC8M16A2F4-6A IT:L

S27KL0641DABHI020 DEMT46H128M16LFCK6ITA S27KL0641DABHB020 IS43LD16640C-25BLI AS4C64M16D1A-6TCN

AS4C256M8D2-25BIN AS4C64M8D1-5BCN S27KS0641DPBHV020 AS4C128M16MD2-25BCN AS4C8M16D1-5BCN

AS4C64M32MD2-25BCN AS4C128M16MD2A-25BIN AS4C128M32MD2-18BCN AS4C32M32MD2-25BCN IS43LR16800G-6BL

W9712G6KB25I TR AS4C64M16D3B-12BINTR W97AH6KBVX2I MT44K16M36RB-125E:A TR MT44K16M36RB-107E:A TR

AS4C128M8D2A-25BIN AS4C128M8D2A-25BCN AS4C32M16SB-7TINTR AS4C256M16D3C-93BCN AS4C128M16D3LC-12BIN

AS4C128M16D3LC-12BCN AS4C64M32MD1A-5BIN MT40A512M8SA-062E:F TR IS45S32800J-7TLA2 AS4C256M16D3LC-12BCN

AS4C16M16SB-6TIN AS4C16M16SB-7TCN AS4C2M32SA-6TINTR AS4C16M16SB-6BIN AS4C16M16SB-6TINTR

IS66WVO32M8DALL-200BLI-TR IS66WVO32M8DBLL-133BLI-TR IS43LD32320C-18BLI IS46TR16K01S2AL-125KBLA2