## TPS65720, TPS657201, TPS657202, TPS65721

ZHCSI58C - OCTOBER 2009-REVISED MAY 2018

# TPS6572x 电源管理 IC (PMIC),具有电池充电器、一个降压转换器和一个LDO

## 1 特性

- 具备电源路径管理功能的电池充电器

- 28V 额定电源路径具有:

- 100mA 输入电流限制

- 500mA 输入电流限制

- 300mA 充电电流

- 适用于 TPS65720 的 200mA 降压转换器

- 适用于 TPS65721、TPS657201、TPS657202 的 400mA 降压转换器

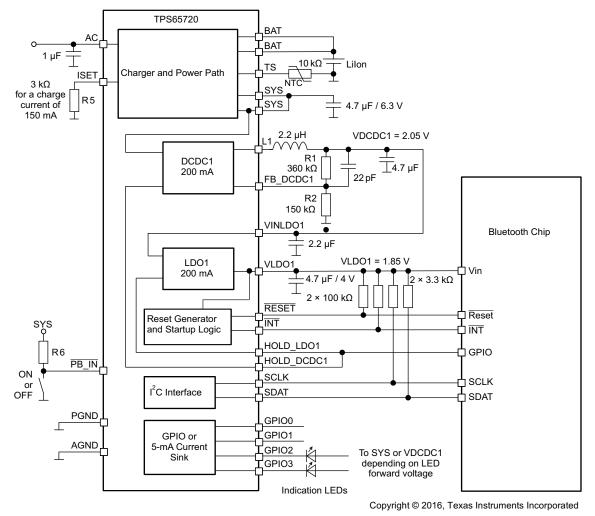

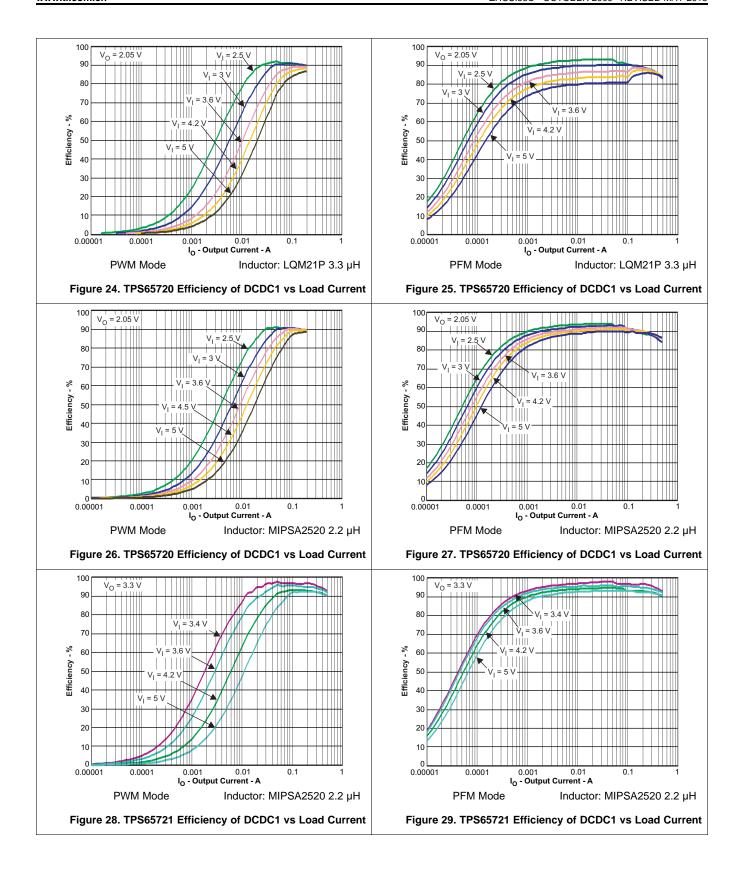

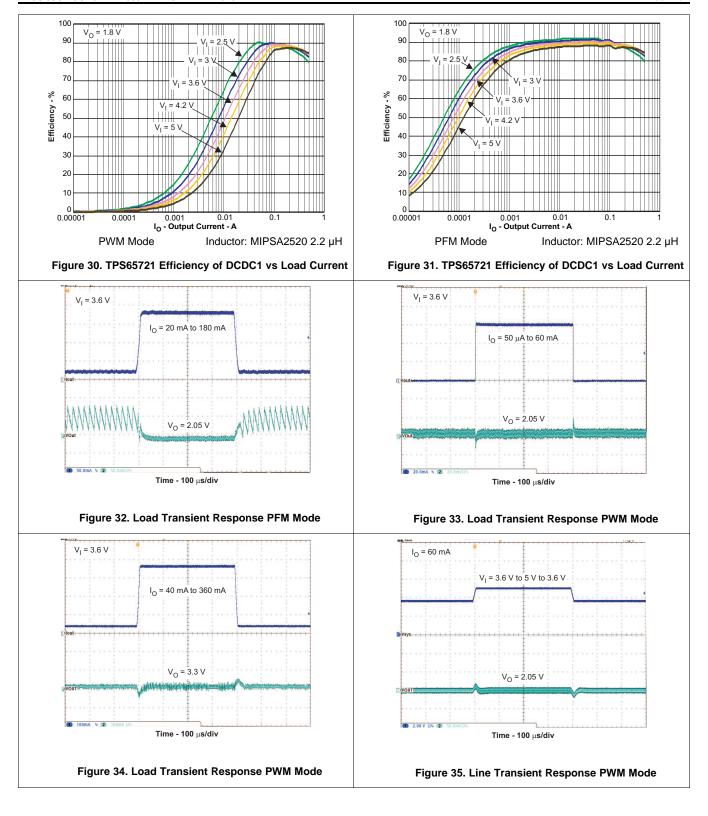

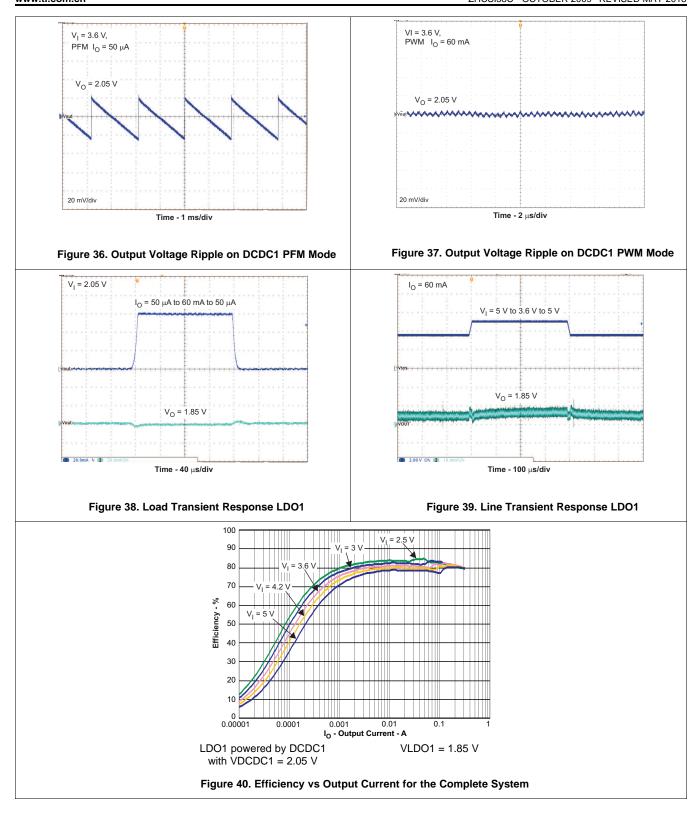

- 效率高达 92%

- 直流/直流转换器的 V<sub>IN</sub> 范围从 2.3V 扩大为 5.6V

- 2.25MHz 固定频率工作

- 轻负载电流状态下的省电模式

- PWM 模式下输出电压精度为 ±2%

- 可实现 100% 占空比,以确保最低压降

- 1 个通用 200mA LDO

- LDO 的 V<sub>IN</sub> 范围为 1.8V 至 5.6V

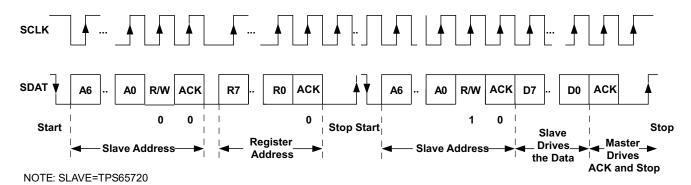

- 与 I<sup>2</sup>C 兼容的接口

- 4 个通用输入输出 (GPIO)

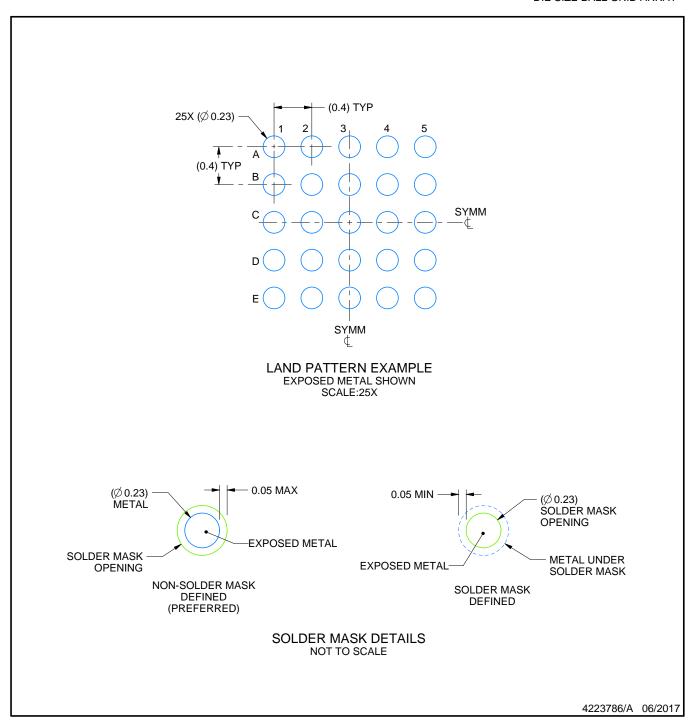

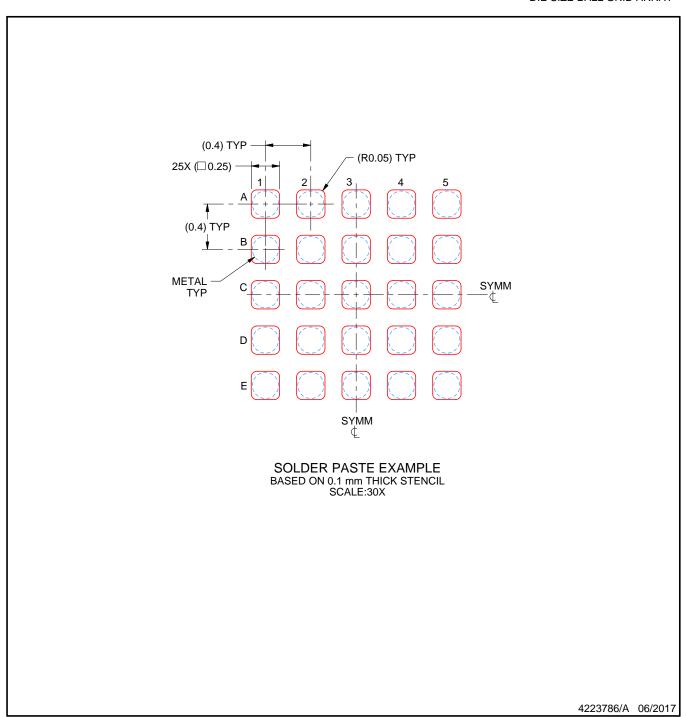

- 采用引脚间距为 0.4mm 的 25 焊球 DSBGA 以及 4mm × 4mm 32 引脚 WQFN 封装。

#### 2 应用

- 蓝牙耳机

- 手持设备

- 可穿戴设备、智能手表

- 便携式配件

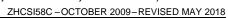

# 3 说明

TPS6572x 器件是一种小型电源管理装置,专用于蓝牙耳机或其他便携式低功耗终端设备。该器件包含一个支持 USB 的锂离子充电器、一个高效的降压转换器和一个低压降线性稳压器,同时还具备其他支持功能。该器件由 I<sup>2</sup>C 接口来控制。可使用出厂时经过编程的非易失性内存来自定义多个设置。

为了在最大可能的负载电流范围内实现最大效率, 2.25MHz 的降压转换器在轻负载时进入低功耗模式。对于低噪声应用, 这些器件可通过与 I<sup>2</sup>C 兼容的接口强制进入固定频率 PWM 模式。

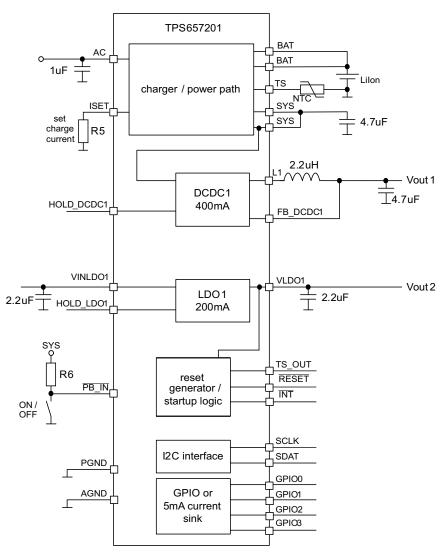

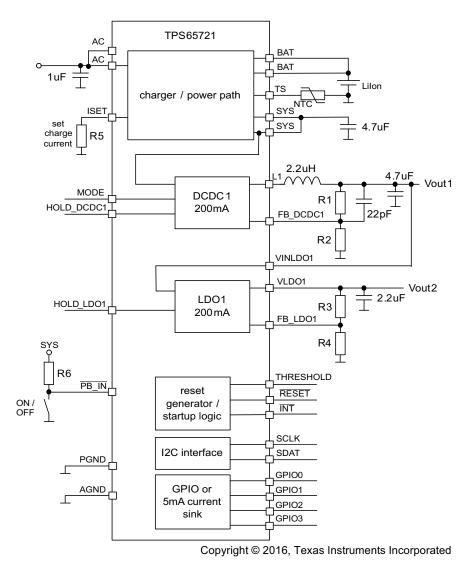

为了实现小解决方案尺寸,该器件允许使用小型电感器和电容器。TPS65720可在直流/直流转换器上提供高达 200mA 的输出电流,而 TPS657201、

TPS657202 和 TPS65721 可提供高达 400mA 的输出电流。TPS6572x 还集成了一个 200mA 的 LDO。该 LDO 可在 1.8V 至 5.6V 输入电压范围内正常运行,这使得它可以由降压转换器的输出供电,也可以由系统电压直接供电。

TPS65720、TPS657201 和 TPS657202 采用焊球间 距为 0.4mm 的小型 25 焊球 2mm × 2mm 晶圆芯片级 封装 (DSBGA) 或者

间距为 0.4mm 的 4mm × 4mm WQFN 封装 (TPS65721)。

#### 器件信息(1)

| 器件型号      | 号 封装 封装尺寸  |                 |  |  |

|-----------|------------|-----------------|--|--|

| TPS65720x | DSBGA (25) | 2.11mm x 2.11mm |  |  |

| TPS65721  | WQFN (32)  | 4.00mm × 4.00mm |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

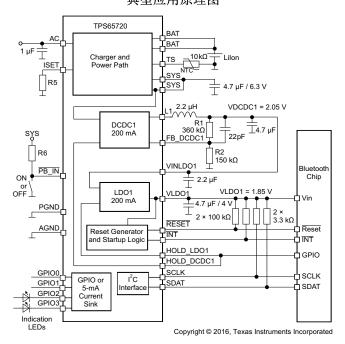

# 典型应用原理图

Changes from Revision A (September 2015) to Revision B

Changes from Original (October 2009) to Revision A

Page

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 目录    |                |                             |                                                                                        |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|-----------------------------|----------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | 特性       1         应用       1         说明       1         修订历史记录       2         Device Options       3         Pin Configuration and Functions       4         Specifications       7         7.1 Absolute Maximum Ratings       7         7.2 ESD Ratings       7         7.3 Recommended Operating Conditions       7         7.4 Thermal Information       8         7.5 Electrical Characteristics       8         7.6 Dissipation Ratings       14         7.7 Timing Requirements       14         7.8 Switching Characteristics       15         7.9 Typical Characteristics       15         7.9 Typical Characteristics       16         Detailed Description       18         8.1 Overview       18         8.2 Functional Block Diagrams       18         8.3 Feature Description       20 | 1 1 1 | 10<br>11<br>12 | 8.4 Device Functional Modes | 31<br>33<br>47<br>47<br>47<br>56<br>56<br>56<br>57<br>57<br>57<br>57<br>57<br>57<br>57 |

| : 之<br>han                      | 多订历史记录<br>L前版本的页码可能与当前版本有所不同。<br>ges from Revision B (October 2016) to Revision C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                |                             | Page                                                                                   |

|                                 | 更改 更改了数据表的标题                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                |                             | 1                                                                                      |

# 5 Device Options

| PART NUMBER (1) | SIZE FOR DSBGA PACKAGE                   | OPTION                                                                                                        |

|-----------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| TPS65720        | D = 2105 μm ±25 μm<br>E = 2105 μm ±25 μm | DCDC1 externally adjustable<br>LDO1 default 1.85 V<br>AC input current limit = 500 mA                         |

| TPS657201       | D = 2105 μm ±25 μm<br>E = 2105 μm ±25 μm | DCDC1 default 1.85 V<br>LDO1 default 1.85 V<br>analog multiplexer (TS_OUT)<br>AC input current limit = 500 mA |

| TPS657202       | D = 2105 μm ±25 μm<br>E = 2105 μm ±25 μm | DCDC1 default 1.90 V<br>LDO1 default 2.85 V<br>analog multiplexer (TS_OUT)<br>AC input current limit = 100 mA |

| TPS65721        | _                                        | DCDC1 externally adjustable<br>LDO1 externally adjustable<br>AC input current limit = 500 mA                  |

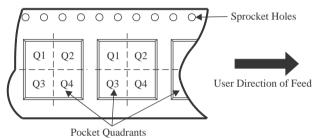

<sup>(1)</sup> The RSN and YFF package is available in tape and reel. Add R suffix (TPS65720YFFR; TPS65721RSNR) to order quantities of 3000 parts per reel. Add T suffix (TPS65720YFFT; TPS65721RSNT) to order quantities of 250 parts per reel.

# 6 Pin Configuration and Functions

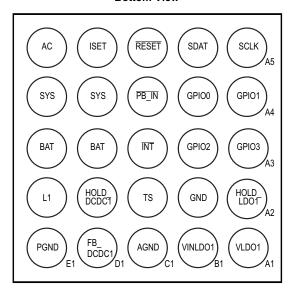

YFF Package 25-Pin DSBGA Bottom View

## Pin Functions—DSBGA (TPS65720)

|          | PIN        |     | 2                                                                                                                                        |  |  |

|----------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. NAME |            | 1/0 | DESCRIPTION                                                                                                                              |  |  |

| A1       | VLDO1      | 0   | Output voltage of LDO1                                                                                                                   |  |  |

| A2       | HOLD_LDO1  | - 1 | Power-on input for LDO1. When pulled HIGH, LDO1 is kept enabled after PB_IN was released HIGH.                                           |  |  |

| A3       | GPIO3      | I/O | General purpose I/O or 5-mA current sink                                                                                                 |  |  |

| A4       | GPIO1      | I/O | eral purpose I/O                                                                                                                         |  |  |

| A5       | SCLK       | - 1 | k input for the I <sup>2</sup> C interface                                                                                               |  |  |

| B1       | VINLDO1    | - 1 | Input voltage for LDO1                                                                                                                   |  |  |

| B2       | GND        | _   | Connect to AGND and PGND                                                                                                                 |  |  |

| B3       | GPIO2      | I/O | General purpose I/O or 5-mA current sink                                                                                                 |  |  |

| B4       | GPIO0      | I/O | General purpose I/O                                                                                                                      |  |  |

| B5       | SDAT       | I/O | Data line for the I <sup>2</sup> C interface                                                                                             |  |  |

| C1       | AGND       | _   | Analog ground                                                                                                                            |  |  |

| C2       | TS         | - 1 | Connect a thermistor from this pin to GND for battery temperature                                                                        |  |  |

| C3       | ĪNT        | 0   | Open-drain interrupt output                                                                                                              |  |  |

| C4       | PB_IN      | 1   | Push button input; Turns on DCDC1 and LDO1 if pulled to GND.                                                                             |  |  |

| C5       | RESET      | 0   | Open-drain output of the reset generator; This output goes active LOW when the output voltage of LDO1 falls 8% below its target voltage. |  |  |

| D1       | FB_DCDC1   | - 1 | Feedback input of step-down converter                                                                                                    |  |  |

| D2       | HOLD_DCDC1 | - 1 | Power-On input for DCDC1 converter. When pulled HIGH, the DC-DC converter is kept enabled after PB_IN was released HIGH.                 |  |  |

| D3       | BAT        | I/O | Connect to battery + terminal                                                                                                            |  |  |

| D4       | SYS        | 0   | System voltage; output of the power path manager. Power input for step-down converter DCDC1                                              |  |  |

| D5       | ISET       | 1   | Connect a resistor from this pin to GND to set fast charge current                                                                       |  |  |

| E1       | PGND       | _   | Power ground                                                                                                                             |  |  |

| E2       | L1         | 0   | Switch output of step-down converter                                                                                                     |  |  |

| E3       | BAT        | I/O | Connect to battery + terminal                                                                                                            |  |  |

| E4       | SYS        | 0   | System voltage; output of the power path manager. Power input for step-down converter DCDC1                                              |  |  |

| E5       | AC         | - 1 | Input power for power manager, connect to external DC supply.                                                                            |  |  |

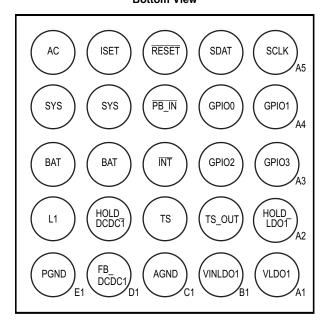

#### YFF Package 25-Pin DSBGA Bottom View

## Pin Functions—DSBGA (TPS657201, TPS657202)

|          | PIN         |     |                                                                                                                                          |  |  |

|----------|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. NAME |             | 1/0 | DESCRIPTION                                                                                                                              |  |  |

| A1       | VLDO1       | 0   | Output voltage of LDO1                                                                                                                   |  |  |

| A2       | HOLD_LDO1   | ı   | Power-on input for LDO1. When pulled HIGH, LDO1 is kept enabled after PB_IN was released HIGH.                                           |  |  |

| A3       | GPIO3       | I/O | General purpose I/O or 5-mA current sink                                                                                                 |  |  |

| A4       | GPIO1       | I/O | General purpose I/O                                                                                                                      |  |  |

| A5       | SCLK        | I   | Clock input for the I <sup>2</sup> C interface                                                                                           |  |  |

| B1       | VINLDO1     | ı   | Input voltage for LDO1                                                                                                                   |  |  |

| B2       | VBAT/TS_OUT | 0   | Output of battery temperature and battery voltage monitor                                                                                |  |  |

| В3       | GPIO2       | I/O | General purpose I/O or 5-mA current sink                                                                                                 |  |  |

| B4       | GPIO0       | I/O | General purpose I/O                                                                                                                      |  |  |

| B5       | SDAT        | I/O | Data line for the I <sup>2</sup> C interface                                                                                             |  |  |

| C1       | AGND        | _   | Analog ground                                                                                                                            |  |  |

| C2       | TS          | - 1 | Connect a thermistor from this pin to GND for battery temperature                                                                        |  |  |

| C3       | ĪNT         | 0   | Open-drain interrupt output                                                                                                              |  |  |

| C4       | PB_IN       | 1   | Push button input; Turns on DCDC1 and LDO1 if pulled to GND.                                                                             |  |  |

| C5       | RESET       | 0   | Open-drain output of the reset generator; This output goes active LOW when the output voltage of LDO1 falls 8% below its target voltage. |  |  |

| D1       | FB_DCDC1    | 1   | Feedback input of step-down converter                                                                                                    |  |  |

| D2       | HOLD_DCDC1  | - 1 | Power-on input for DCDC1 converter. When pulled HIGH, the DC-DC converter is kept enabled after PB_IN was released HIGH.                 |  |  |

| D3       | BAT         | I/O | Connect to battery + terminal                                                                                                            |  |  |

| D4       | SYS         | 0   | System voltage; output of the power path manager. Power input for step-down converter DCDC1                                              |  |  |

| D5       | ISET        | - 1 | Connect a resistor from this pin to GND to set fast charge current                                                                       |  |  |

| E1       | PGND        | _   | Power ground                                                                                                                             |  |  |

| E2       | L1          | 0   | Switch output of step-down converter                                                                                                     |  |  |

| E3       | BAT         | I/O | Connect to battery + terminal                                                                                                            |  |  |

| E4       | SYS         | 0   | System voltage; output of the power path manager. Power input for step-down converter DCDC1                                              |  |  |

| E5       | AC          | 1   | Input power for power manager, connect to external DC supply.                                                                            |  |  |

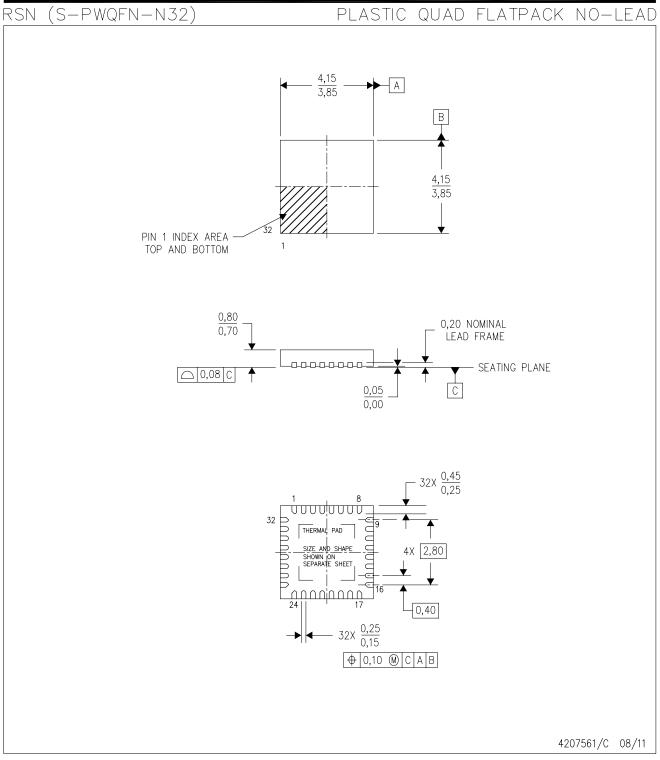

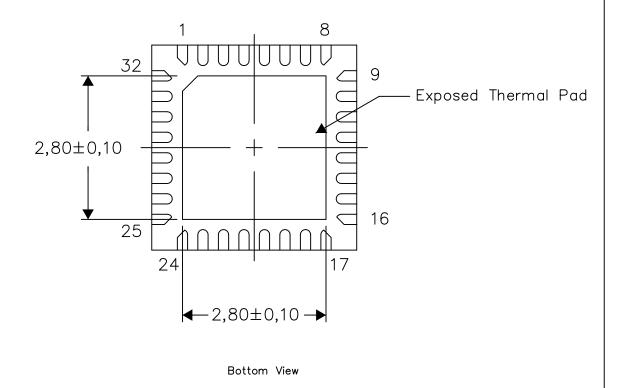

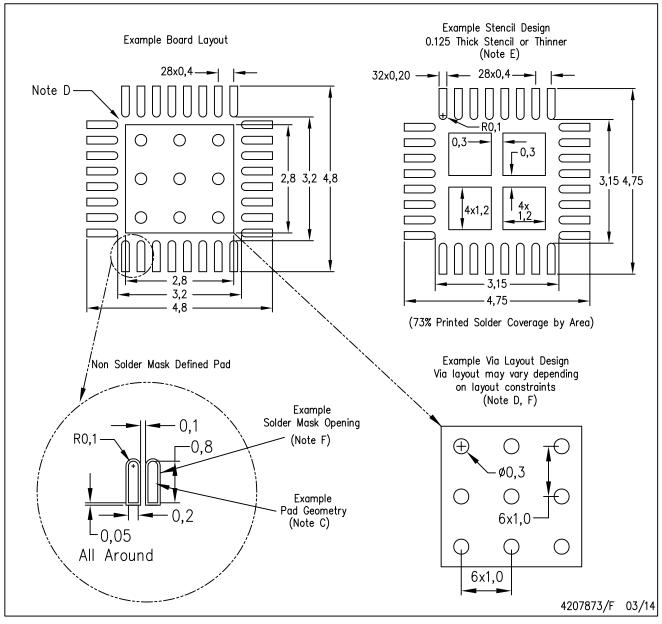

#### RSN Package 32-Pin WQFN With Thermal Pad Top View

## Pin Functions—WQFN (TPS65721)

| PIN        |        |     | FILLI GIICUOIIS—WQL N (1F.303721)                                                                                                                |

|------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | NO.    | I/O | DESCRIPTION                                                                                                                                      |

| AC         | 17, 18 | I   | Input power for power manager, connect to external DC supply.                                                                                    |

| AGND       | 28     | _   | Analog ground                                                                                                                                    |

| BAT        | 21, 22 | I/O | Connect to battery + terminal                                                                                                                    |

| FB_DCDC1   | 26     | I   | Feedback input of step-down converter                                                                                                            |

| FB_LDO1    | 1      | Ţ   | Feedback input for LDO1                                                                                                                          |

| GND        | 29     | _   | Connect to AGND and PGND                                                                                                                         |

| GPIO0      | 7      | I/O | General purpose I/O                                                                                                                              |

| GPIO1      | 6      | I/O | General purpose I/O                                                                                                                              |

| GPIO2      | 5      | I/O | General purpose I/O or 5-mA current source                                                                                                       |

| GPIO3      | 4      | I/O | General purpose I/O or 5-mA current source                                                                                                       |

| HOLD_DCDC1 | 25     | ı   | Power-on input for DCDC1 converter. When pulled HIGH, the DC-DC converter is kept enabled after PB_IN was released HIGH.                         |

| HOLD_LDO1  | 2      | 1   | Power-on input for LDO1. When pulled HIGH, LDO1 is kept enabled after PB_IN was released HIGH.                                                   |

| ĪNT        | 13     | 0   | Open-drain interrupt output                                                                                                                      |

| ISET       | 16     | - 1 | Connect a resistor from this pin to GND to set fast charge current                                                                               |

| L1         | 23     | 0   | Switch output of step-down converter                                                                                                             |

| MODE       | 11     | 1   | Pull HIGH to force the DCDC1 converter to PWM mode.                                                                                              |

| PB_IN      | 15     | - 1 | Push button input; Turns on DCDC1 and LDO1 if pulled to GND.                                                                                     |

| PGND       | 24     | _   | Power ground                                                                                                                                     |

| RESET      | 14     | 0   | Open-drain output of the reset generator; This output goes active LOW when the input voltage at pin THRESHOLD falls below the threshold voltage. |

| SCLK       | 8      | - 1 | Clock input for the I <sup>2</sup> C interface                                                                                                   |

| SDAT       | 12     | I/O | Data line for the I <sup>2</sup> C interface                                                                                                     |

| SYS        | 19, 20 | 0   | System voltage; output of the power path manager. Power input for step-down converter DCDC1                                                      |

| THRESHOLD  | 3      | ı   | Input voltage to the reset comparator. When the input voltage falls below the threshold, the RESET output is actively pulled LOW.                |

| TS         | 27     | 1   | Connect a thermistor from this pin to GND for battery temperature                                                                                |

| VINLDO1    | 30     | I   | Input voltage for LDO1                                                                                                                           |

| VLDO1      | 31     | 0   | Output voltage from LDO1                                                                                                                         |

| ThermalPad |        | _   | Connect to GND                                                                                                                                   |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                       |                                                             | MIN   | MAX          | UNIT   |

|---------------------------------------|-------------------------------------------------------------|-------|--------------|--------|

|                                       | All pins except A/PGND, AC, GPIOx pins with respect to AGND | -0.3  | 7            | V      |

| Input voltage                         | GPIOx pins with respect to AGND                             | -0.3  | VSYS         | V      |

|                                       | AC pin with respect to AGND                                 | -0.3  | 28           | V      |

| Voltage range on pin VLDO1,           | FB_LDO1, TS_OUT, TS with respect to AGND                    | -0.3  | 3.6          | V      |

|                                       | AC, BAT, SYS, L1, VLDO1, VINLDO1, PGND                      |       | 600          | mA     |

| Current                               | GPIOx, AGND                                                 |       | 20           | mA     |

|                                       | All other pins                                              |       | 3            | mA     |

| Continuous total power dissipa        | ation                                                       | See D | issipation R | atings |

| Operating free-air temperature        | , T <sub>A</sub>                                            | -40   | 85           | °C     |

| Maximum junction temperature          | e, T <sub>J</sub>                                           |       | 125          | °C     |

| Storage temperature, T <sub>stg</sub> |                                                             | -65   | 150          | °C     |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|             |                         |                                                                               | VALUE | UNIT |

|-------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|             |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | ±2000 |      |

| $V_{(ESD)}$ | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

|                       |                                                                                                                                    | MIN  | NOM | MAX                  | UNIT |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-----|----------------------|------|

| $V_{AC}$              | Input voltage at AC pin                                                                                                            | 4.35 |     | 28                   | V    |

| $V_{SYS}$             | Voltage at SYS pin                                                                                                                 | 2.2  |     | 5.6                  | V    |

| I <sub>INUSB</sub>    | Input current at AC                                                                                                                |      |     | 500                  | mA   |

| I <sub>OUTSYS</sub>   | Output current at SYS                                                                                                              |      |     | 400                  | mA   |

| I <sub>BAT</sub>      | Average current into and out of BAT pin                                                                                            |      |     | 300                  | mA   |

| V <sub>INDCDC1</sub>  | Input voltage for step-down converter DCDC1                                                                                        | 2.3  |     | 5.6                  | V    |

| V <sub>DCDC1</sub>    | Output voltage for DCDC1 step-down converter; externally adjustable                                                                | 0.6  |     | V <sub>INDCDC1</sub> | V    |

| I <sub>OUTDCDC1</sub> | Output current at L                                                                                                                |      |     | 400                  | mA   |

| L                     | Inductor at L <sup>(1)</sup>                                                                                                       | 2.2  | 3.3 | 4.7                  | μН   |

| V <sub>INLDO1</sub>   | Input voltage for LDO1                                                                                                             | 1.8  |     | VSYS                 | V    |

| V <sub>LDO1</sub>     | Output voltage for LDO1                                                                                                            | 0.8  |     | 3.3                  | V    |

| I <sub>LDO1</sub>     | Output current at LDO1                                                                                                             |      |     | 200                  | mA   |

| C <sub>INAC</sub>     | Input capacitor at AC <sup>(1)</sup>                                                                                               | 0.1  |     | 1                    | μF   |

| C <sub>BAT</sub>      | Capacitor at BAT <sup>(1)</sup>                                                                                                    | 0.1  |     | 4.7                  | μF   |

| C <sub>SYS</sub>      | Capacitor at SYS <sup>(1)</sup>                                                                                                    | 4.7  |     | 10                   | μF   |

| C <sub>INDCDC1</sub>  | Input capacitor at $V_{\text{INDCDC1}}^{(1)}$ ; if connected to SYS, only one 4.7- $\mu$ F capacitor required for SYS and CINDCDC1 | 4.7  |     |                      | μF   |

| C <sub>OUTDCDC1</sub> | Output capacitor at V <sub>DCDC1</sub> <sup>(1)</sup>                                                                              | 4.7  | 10  | 22                   | μF   |

| C <sub>INLDO1</sub>   | Input capacitor at VINLDO1 (1)                                                                                                     | 2.2  |     |                      | μF   |

| C <sub>OUTLDO1</sub>  | Output capacitor at LDO1 <sup>(1)</sup>                                                                                            | 2.2  |     |                      | μF   |

<sup>(1)</sup> See Application and Implementation for more details.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **Recommended Operating Conditions (continued)**

|                   |                                                                                                                        | MIN | NOM | MAX | UNIT |

|-------------------|------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>ISET</sub> | Minimum ${\rm R}_{\rm ISET}$ value for proper operation; lower values may trigger the short circuit protection on ISET | 700 |     |     | Ω    |

| T <sub>A</sub>    | Operating ambient temperature                                                                                          | -40 |     | 85  | °C   |

| $T_{J}$           | Operating junction temperature                                                                                         | -40 |     | 125 | °C   |

#### 7.4 Thermal Information

|                        |                                              | TPS65720    | TPS65721   |      |

|------------------------|----------------------------------------------|-------------|------------|------|

|                        | THERMAL METRIC (1)                           | YFF (DSBGA) | RSN (WQFN) | UNIT |

|                        |                                              | 25 PINS     | 32 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 60.9        | 37.8       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 0.4         | 28.2       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 11.3        | 8.6        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 1.4         | 0.3        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 11.3        | 8.5        | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | n/a         | 2.6        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

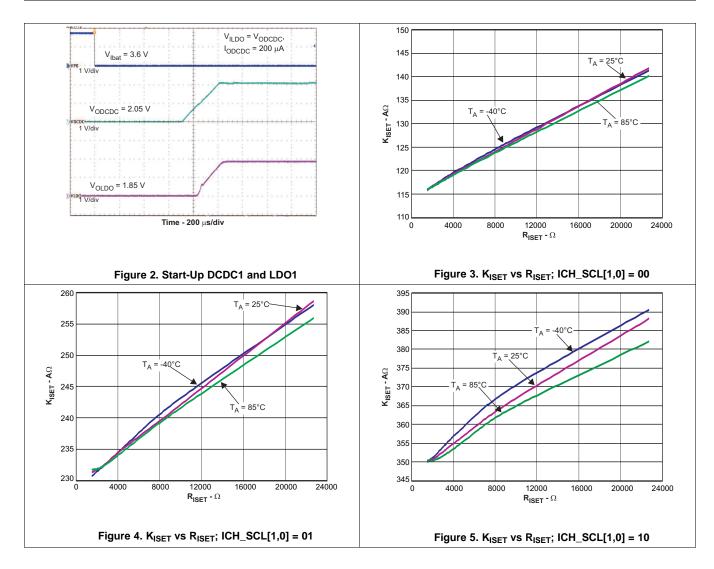

$V_{SYS} = 3.6 \text{ V}$ ,  $V_{DCDC1} = 2.05 \text{ V}$ , PFM mode,  $L = 3.3 \mu\text{H}$ ,  $C_{OUTDCDC1} = 4.7 \mu\text{F}$ ,  $V_{INLDO1} = 2.05 \text{ V}$ ,  $V_{LDO1} = 1.85 \text{ V}$ ,  $T_A = -40 ^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$  typical values apply in a temperature range of 10  $^{\circ}\text{C}$  to 35  $^{\circ}\text{C}$  (unless otherwise noted)

|                             | PARAMETER                                                                                                         | TEST CONDITIONS                                                                                 | MIN                | TYP              | MAX              | UNIT |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------|------------------|------------------|------|

| SUPPLY CURRE                | ENT                                                                                                               |                                                                                                 |                    |                  |                  |      |

| l <sub>a</sub>              | Operating quiescent current when                                                                                  | DCDC1 enabled, IOUT = 0 mA. PFM mode enabled; device not switching                              |                    | 36               | 45               | μА   |

| _                           | only DCDC1 converter is enabled                                                                                   | DCDC1 enabled, IOUT = 0 mA. PWM mode                                                            |                    | 2.8              |                  | mA   |

|                             | Operating quiescent current when                                                                                  | Current into BAT pin (PFM mode)                                                                 |                    | 33               | 50               | μΑ   |

| la                          | LDO1 and DCDC1 are enabled                                                                                        | Current into VINLDO1                                                                            |                    | 13               | 18               | μΑ   |

|                             | Shutdown current after voltage was applied to BAT but device never enabled before (shipping mode)                 | For VINLDO1 = 0 V (LDO1 supplied by DCDC1); powered by VBAT = 3.6 V                             |                    | 4                | 13               | μА   |

| I <sub>SD</sub>             | Shutdown current after first power-<br>up                                                                         | For VINLDO1 = 0 V (LDO1 supplied by DCDC1); powered by VBAT = 3.6 V                             |                    | 12               | 17               | μА   |

|                             | Shutdown current after first power-<br>up                                                                         | For VINLDO1 ≠ 0 V (LDO1 supplied by SYS); powered by VBAT = 3.6 V                               |                    | 12               | 18               | μА   |

| SDAT, SCLK, PE              | B_IN, HOLD, GPIO0 TO GPIO3, INT, RE                                                                               | SET, THRESHOLD                                                                                  |                    |                  |                  |      |

| V <sub>IH</sub>             | High-level input voltage for SCLK,<br>SDAT, GPIOx, HOLD_DCDC1,<br>HOLD_LDO1, PB_IN                                | GPIOs configured as input                                                                       | 1.2                |                  | VSYS             | V    |

| $V_{IL}$                    | Low-level input voltage for SCLK,<br>SDAT, GPIOx, <u>HOLD_DCDC1</u> ,<br>HOLD_LDO1, <u>PB_IN</u>                  | GPIOs configured as input                                                                       | 0                  |                  | 0.4              | V    |

| V <sub>OL</sub>             | Low-level output voltage for SDAT, GPIOx, INT, RESET                                                              | GPIOs configured as output; I <sub>o</sub> = 1 mA; no internal pull-up                          | 0                  |                  | 0.4              | V    |

| I <sub>OL</sub>             | Sink current for GPIO2, GPIO3                                                                                     | GPIO2, GPIO3 configured as current sink; $V_{OL} = 0.4 \ V$ ; for $T_J = 0^{\circ}C$ to 85°C    | -20%               | 5                | 20%              | mA   |

|                             | Sink current for GPIOx                                                                                            | GPIOx configured as open-drain output ; output = LOW                                            |                    |                  | 3                | mA   |

| V <sub>OL</sub>             | Minimum voltage for proper current<br>regulation from GPIO2 or GPIO3 to<br>GND if programmed as a current<br>sink | I <sub>O</sub> = 5 mA; current sink turned on                                                   | 0.4                |                  |                  | ٧    |

| V <sub>RESET-falling</sub>  | LDO1 out of regulation reset                                                                                      | Falling edge; RESET is asserted LOW for TPS65720, TPS657201, TPS657202                          | VLDO1, nom-<br>13% |                  | VLDO1,<br>nom-7% | V    |

| V <sub>RESET-rising</sub>   | voltage                                                                                                           | Rising edge; RESET is released HIGH for TPS65720, TPS657201, TPS657202 after T <sub>RESET</sub> |                    | VLDO1,<br>nom-4% |                  | V    |

| V <sub>THRESHOLD_down</sub> | Threshold voltage for reset input                                                                                 | Falling voltage; WQFN package only                                                              | -3%                | 570              | 3%               | mV   |

| V <sub>THRESHOLD_hys</sub>  | Hysteresis on THRESHOLD                                                                                           | Rising voltage; WQFN package only                                                               |                    | 30               |                  | mV   |

| I <sub>LKG</sub>            | Input leakage current                                                                                             | PB_IN, SDAT, SCLK, GPIOx configured as output, INT, RESET, output high impedance                |                    |                  | 0.2              | μΑ   |

$V_{SYS} = 3.6 \text{ V}, V_{DCDC1} = 2.05 \text{ V}, \text{ PFM mode, L} = 3.3 \text{ } \mu\text{H}, C_{OUTDCDC1} = 4.7 \text{ } \mu\text{F}, V_{INLDO1} = 2.05 \text{ V}, V_{LDO1} = 1.85 \text{ V}, T_{A} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                            | PARAMETER                                              | TEST CONDITIONS                                                            | MIN                | TYP               | MAX               | UNIT |

|----------------------------|--------------------------------------------------------|----------------------------------------------------------------------------|--------------------|-------------------|-------------------|------|

| STEP-DOWN C                | ONVERTER                                               |                                                                            |                    |                   |                   |      |

| V <sub>SYS</sub>           | Input voltage for DCDC1                                |                                                                            | 2.3                |                   | 5.6               | V    |

|                            | Internal undervoltage lockout                          | V <sub>SYS</sub> falling                                                   | 2.15               | 2.2               | 2.25              | V    |

| UVLO                       | threshold hysteresis                                   | V <sub>SYS</sub> rising                                                    |                    | 120               |                   | mV   |

| POWER SWITC                | н                                                      |                                                                            |                    |                   |                   |      |

| Б.                         | High side MOOFFT ON societares                         | V <sub>SYS</sub> = V <sub>INDCDC1</sub> = 3.6 V, YFF package               |                    | 350               | 600               | 0    |

| R <sub>DS(ON)</sub>        | High-side MOSFET ON-resistance                         | V <sub>SYS</sub> = V <sub>INDCDC1</sub> = 3.6 V, RSN package               |                    | 400               | 650               | mΩ   |

| I <sub>LK_HS</sub>         | High-side MOSFET leakage current                       | V <sub>DS</sub> = 5.6 V                                                    |                    |                   | 1                 | μА   |

| Б.                         | Law aida MOOFFT ON assistantes                         | V <sub>INDCDC1/2</sub> = 3.6 V, YFF package                                |                    | 300               | 500               | mΩ   |

| R <sub>DS(ON)</sub>        | Low-side MOSFET ON-resistance                          | V <sub>INDCDC1/2</sub> = 3.6 V, RSN package                                |                    | 350               | 550               | mΩ   |

| I <sub>LK_LS</sub>         | Low-side MOSFET leakage current                        | VDS = 5.6 V                                                                |                    |                   | 1                 | μА   |

|                            | Forward current limit high-side and                    | 2.3 V ≤ V <sub>IN</sub> ≤ 5.6 V, TPS65720                                  | 425                | 600               | 775               | mA   |

| I <sub>LIMF</sub>          | low-side MOSFET                                        | 2.3 V ≤ V <sub>IN</sub> ≤ 5.6 V, TPS65721, TPS657201, TPS657202            | 625                | 850               | 1150              | mA   |

|                            | DC suitant surrent                                     | V <sub>SYS</sub> > 2.7 V; TPS65720                                         |                    |                   | 200               | mA   |

| lo                         | DC output current                                      | V <sub>SYS</sub> > 2.7 V; TPS65721, TPS657201, TPS657202                   |                    |                   | 400               | mA   |

| OUTPUT                     |                                                        |                                                                            |                    |                   |                   |      |

| V <sub>OUT</sub>           | Output voltage range                                   |                                                                            | 0.6                |                   | Vin               | V    |

| V <sub>FB</sub>            | Feedback voltage                                       | for TPS65720, TPS65721                                                     |                    | 0.6               |                   | V    |

| V <sub>OUT</sub>           | Default output voltage for TPS657201                   |                                                                            |                    | 1.85              |                   | ٧    |

| V <sub>OUT</sub>           | Default output voltage for TPS657202                   |                                                                            |                    | 1.90              |                   | V    |

| I <sub>FB</sub>            | FB pin input current for externally adjustable version | External resistor-divider                                                  |                    |                   | 0.1               | μА   |

| I <sub>FB</sub>            | FB pin input current for TPS657201, TPS657202          | Internal resistor-divider                                                  |                    |                   | 5                 | μА   |

|                            | DC output voltage accuracy (1)                         | $V_{IN}$ = 2.3 V to 5.6 V; PFM operation, 0 mA < $I_{OUT}$ < $I_{OUTMAX}$  |                    | 1%                | 3%                |      |

| $V_{\text{OUT}}$           | DC output voltage accuracy V                           | $V_{IN}$ = 2.3 V to 5.6 V, PWM operation, 0 mA < $I_{OUT}$ < $I_{OUTMAX}$  | -2%                |                   | 2%                |      |

|                            | DC output voltage load regulation                      | PWM operation                                                              |                    | 0.5               |                   | %/A  |

| $V_{PGOOD\text{-falling}}$ | PGOOD threshold at falling output voltage              | <pgoodz_dcdc1> is set to 1</pgoodz_dcdc1>                                  | VDCDC1,<br>nom-14% |                   | VDCDC1,<br>nom-7% | V    |

| V <sub>PGOOD-rising</sub>  | PGOOD threshold at rising output voltage               | <pgoodz_dcdc1> is set to 0</pgoodz_dcdc1>                                  |                    | VDCDC1,<br>nom-5% |                   | V    |

| R <sub>DIS</sub>           | Internal discharge resistor at L                       | DCDC1 disabled; the discharge function can be disabled as an EEPROM option | 300                | 400               |                   | Ω    |

| THERMAL PRO                | TECTION FOR DCDC1 AND LDO1                             |                                                                            |                    |                   |                   |      |

| T <sub>SD</sub>            | Thermal shutdown                                       | Increasing junction temperature                                            |                    | 150               |                   | °C   |

|                            | Thermal shutdown hysteresis                            | Decreasing junction temperature                                            |                    | 30                |                   | °C   |

|                            |                                                        |                                                                            |                    |                   |                   |      |

<sup>(1)</sup> Output voltage specification does not include tolerance of external voltage programming resistors.

$V_{SYS} = 3.6 \text{ V}, V_{DCDC1} = 2.05 \text{ V}, \text{ PFM mode, L} = 3.3 \text{ } \mu\text{H}, C_{OUTDCDC1} = 4.7 \text{ } \mu\text{F}, V_{INLDO1} = 2.05 \text{ V}, V_{LDO1} = 1.85 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                        | PARAMETER                                                                                                             | TEST CONDITIONS                                                                       | MIN        | TYP   | MAX      | UNIT |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------|-------|----------|------|

| VLDO1 LOW DI           | ROPOUT REGULATOR                                                                                                      |                                                                                       |            |       |          |      |

| V <sub>INLDO</sub>     | Input voltage range for LDO1                                                                                          |                                                                                       | 1.8        |       | 5.6      | V    |

| V <sub>LDO1</sub>      | LDO1 output voltage range                                                                                             |                                                                                       | 0.8        |       | 3.3      | V    |

| V <sub>LDO1</sub>      | LDO1 output voltage                                                                                                   | Default output voltage for TPS65720, TPS657201                                        |            | 1.85  |          | V    |

| V <sub>LDO1</sub>      | LDO1 output voltage                                                                                                   | Default output voltage for TPS657202                                                  |            | 2.85  |          | V    |

| V <sub>FB_LDO1</sub>   | Feedback voltage                                                                                                      | Externally adjustable version only: TPS65721                                          |            | 0.8   |          | V    |

| I <sub>FB_LDO1</sub>   | FB pin input current                                                                                                  |                                                                                       |            |       | 0.1      | μА   |

| Io                     | Output current for LDO1                                                                                               |                                                                                       |            |       | 200      | mA   |

| I <sub>SC</sub>        | LDO1 short circuit current limit                                                                                      | VLDO1 = GND; V <sub>INLDO1</sub> = 2.05 V                                             |            | 350   | 500      | mA   |

|                        | Dropout voltage at LDO1, YFF package                                                                                  | I <sub>O</sub> = 200 mA, V <sub>INLDO</sub> = 2.05 V                                  |            |       | 180      | mV   |

|                        | Dropout voltage at LDO1, RSN package                                                                                  | I <sub>O</sub> = 200 mA, V <sub>INLDO</sub> = 2.05 V                                  |            | 120   |          | mV   |

|                        | Output voltage accuracy for LDO1                                                                                      | I <sub>O</sub> = 200 mA                                                               | -1.5%      |       | 2.5%     |      |

|                        | Line regulation for LDO1                                                                                              | $\rm V_{INLDO1} = V_{LDO1} + 0.5~V$ (min. 1.8 V) to 5.6 V (VSYS), $\rm I_{O} = 50~mA$ | -1%        |       | 1%       |      |

|                        | Load regulation for LDO1                                                                                              | I <sub>O</sub> = 0 mA to 200 mA for LDO1                                              | -1%        |       | 2%       |      |

| R <sub>DIS</sub>       | Internal discharge resistor at VLDO1                                                                                  | LDO disabled, discharge function per default disabled in register                     | 250        | 400   |          | Ω    |

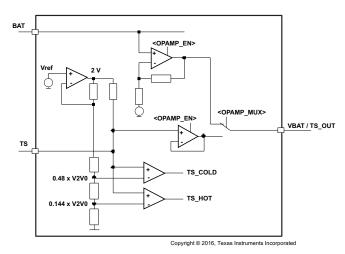

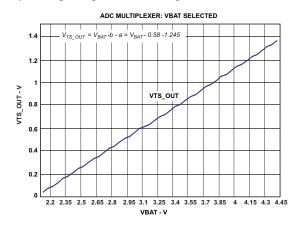

| BATTERY VOL            | TAGE AND BATTERY TEMPERATURE                                                                                          | MONITOR WITH MULTIPLEXER; INTERNAL BATTERY VOLTAGE                                    | COMPARATOR |       |          |      |

| $V_{TS}$               | Input voltage range on TS pin for full scale output on pin TS_OUT (0 V to 1.4 V)  Equals -20°C to 60°C on a 10k NTC 0 |                                                                                       |            | 1.4   | V        |      |

| V <sub>BAT</sub>       | Input voltage range on BAT pin for full scale output on pin TS_OUT (0 V to 1.4 V)                                     |                                                                                       | 2.2        | 2.2   |          | V    |

|                        | Output voltage range on pin                                                                                           | I <sub>TS_OUT</sub> = 0 mA                                                            | 0          |       | 1.4      |      |

| V <sub>TS_OUT</sub>    | TS_OUT                                                                                                                | 0 < I <sub>TS OUT</sub> < 0.05 mA                                                     | 0.06       |       | 1.4      | V    |

|                        | Offset error on pin TS_OUT                                                                                            | In temperature-sense mode; V <sub>O</sub> with V <sub>bat</sub> = 2.2 V               |            |       | ±7.5     | mV   |

| SR                     | Slew rate                                                                                                             | V <sub>TS OUT</sub> ; 0 V to 1.4 V                                                    |            | 1     |          | V/ms |

| I <sub>TS_OUT_SC</sub> | Short circuit current                                                                                                 |                                                                                       | 0.1        |       |          | mA   |

|                        | Load capacitance                                                                                                      | Maximum capacitance at TS_OUT                                                         |            |       | 100      | pF   |

|                        | Battery voltage comparator threshold voltage                                                                          | Depending on Bits <vbat0>, <vbat1>; falling voltage</vbat1></vbat0>                   | -3%        |       | 3%       | V    |

|                        | Battery voltage comparator threshold voltage hysteresis                                                               | Rising voltage                                                                        |            | 200   |          | mV   |

| ACCURACY               |                                                                                                                       |                                                                                       |            |       |          |      |

| VBAT MODE              |                                                                                                                       |                                                                                       |            |       |          |      |

|                        | Offset                                                                                                                | T <sub>J</sub> = 10°C to 35°; for V(TS) ≥ 0.2 V                                       | -22        |       | 22       | mV   |

|                        | Gain error                                                                                                            | T <sub>J</sub> = 10°C to 35°; for V(TS) ≥ 0.2 V                                       | -11        |       | 11       | mV   |

|                        | Offset                                                                                                                | $T_J = -40$ °C to 85°C; for V(TS) $\geq 0.2$ V                                        | -30        |       | 30       | mV   |

|                        | Gain error                                                                                                            | $T_J = -40$ °C to 85°C; for V(TS) $\geq 0.2$ V                                        | -14        |       | 14       | mV   |

| TS MODE                |                                                                                                                       | · ·                                                                                   |            |       | <u> </u> |      |

|                        | Internal TS resistor (for 10k NTC, B=3380)                                                                            | T <sub>J</sub> = 25°C                                                                 | -1.5%      | 29.23 | 1.5%     | kΩ   |

|                        | Internal TS resistor (for 100k NTC)                                                                                   | T <sub>J</sub> = 25°C                                                                 | -1.5%      | 292.3 | 1.5%     | kΩ   |

|                        | Internal TS resistor temperature drift                                                                                | T <sub>J</sub> = -40°C to 85°C                                                        |            | -4.5% |          |      |

|                        | Internal V2V0 reference voltage                                                                                       | $T_J = -40$ °C to 85°C                                                                | -1.2%      | 2     | 1.2%     | V    |

$V_{SYS} = 3.6 \text{ V}, V_{DCDC1} = 2.05 \text{ V}, \text{ PFM mode, L} = 3.3 \text{ } \mu\text{H}, C_{OUTDCDC1} = 4.7 \text{ } \mu\text{F}, V_{INLDO1} = 2.05 \text{ V}, V_{LDO1} = 1.85 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                          | PARAMETER                                                                                                          | TEST CONDITIONS                                                                                                                                        | MIN  | TYP                                               | MAX  | UNIT                                    |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------|------|-----------------------------------------|

| POWER PATH               |                                                                                                                    |                                                                                                                                                        |      |                                                   |      |                                         |

| $V_{UVLO}$               | Undervoltage lockout                                                                                               | $V_{AC}$ : 0 V $\rightarrow$ 4 V                                                                                                                       | 3.2  | 3.3                                               | 3.45 | V                                       |

| V <sub>HYS-UVLO</sub>    | Hysteresis on UVLO                                                                                                 | $V_{AC}$ : 4 $V \rightarrow 0 V$                                                                                                                       | 200  |                                                   | 300  | mV                                      |

| V <sub>IN-DT</sub>       | Input power detection threshold                                                                                    | (Input power detected if V <sub>IN</sub> > V <sub>BAT</sub> + V <sub>IN-DT</sub> ) V <sub>BAT</sub> = 3.6 V, V <sub>IN</sub> : 3.5 V $\rightarrow$ 4 V | 40   | 80                                                | 140  | mV                                      |

| V <sub>HYS-INDT</sub>    | Hysteresis on VIN-DT                                                                                               | $V_{BAT} = 3.6 \text{ V}, V_{IN}: 4 \text{ V} \rightarrow 3.5 \text{ V}$                                                                               | 20   |                                                   |      | mV                                      |

| V <sub>OVP</sub>         | Input overvoltage protection threshold                                                                             | $V_{AC}$ : 5 V $\rightarrow$ 7 V                                                                                                                       | 6.4  | 6.6                                               | 6.8  | V                                       |

| V <sub>HYS-OVP</sub>     | Hysteresis on OVP                                                                                                  | V <sub>AC</sub> : 11 V → 5 V                                                                                                                           |      | 105                                               |      | mV                                      |

|                          | AC pin to SYS pin dropout voltage                                                                                  | $I_{SYS} = 0.3 \text{ A}, V_{AC} = 4.35 \text{ V}, V_{BAT} = 4.2 \text{ V}; YFF package}$                                                              |      | 170                                               | 285  | mV                                      |

| V <sub>DO(AC-SYS)</sub>  | V <sub>AC</sub> – V <sub>SYS</sub>                                                                                 | I <sub>SYS</sub> = 0.3 A, V <sub>AC</sub> = 4.35 V, V <sub>BAT</sub> = 4.2 V; RSN package                                                              |      | 210                                               | 325  | mV                                      |

|                          | Battery to SYS pin dropout voltage                                                                                 | I <sub>SYS</sub> = 0.2 A, V <sub>AC</sub> = 0 V, V <sub>BAT</sub> > 3 V; YFF package                                                                   |      |                                                   | 80   | mV                                      |

| V <sub>DO(BAT-SYS)</sub> | V <sub>BAT</sub> – V <sub>SYS</sub>                                                                                | I <sub>SYS</sub> = 0.2 A, V <sub>AC</sub> = 0 V, V <sub>BAT</sub> > 3 V; RSN package                                                                   |      |                                                   | 120  | mV                                      |

|                          |                                                                                                                    | 00: V <sub>AC</sub> > V <sub>SYS</sub> + V <sub>DO(AC-SYS)</sub> , V <sub>BAT</sub> < 3.3V                                                             | -5%  | 3.4                                               | 5%   | ======================================= |

|                          | SYS pin voltage regulation selectable register                                                                     | 00: V <sub>AC</sub> > V <sub>SYS</sub> + V <sub>DO(AC-SYS)</sub> , V <sub>BAT</sub> ≥ 3.3 V                                                            | -5%  | V <sub>BAT</sub> + 200 mV                         | 5%   |                                         |

| $V_{SYS(REG)}$           | <chgconfig0> Bits <vsys1>;</vsys1></chgconfig0>                                                                    | 01: V <sub>AC</sub> > V <sub>SYS</sub> + V <sub>DO(AC-SYS)</sub>                                                                                       | -5%  | 4.4                                               | 5%   | V                                       |

|                          | <vsys0></vsys0>                                                                                                    | 10: V <sub>AC</sub> > V <sub>SYS</sub> + V <sub>DO(AC-SYS)</sub>                                                                                       | -5%  | 5.0                                               | 5%   |                                         |

|                          |                                                                                                                    | 11: V <sub>AC</sub> > V <sub>SYS</sub> + V <sub>DO(AC-SYS)</sub>                                                                                       | -5%  | 5.5                                               | 5%   |                                         |

| _                        | Maximum Input Current Register                                                                                     | Bit <ac ac="" current0="" current1,="" input=""> = 00</ac>                                                                                             | 90   | 95                                                | 100  |                                         |

| I <sub>AC-MAX</sub>      | <chconfig0></chconfig0>                                                                                            | Bit < AC input current1, AC input current0> = 01 or 10                                                                                                 | 450  | 475                                               | 500  | mA                                      |

| V <sub>AC-LOW</sub>      | Input voltage threshold when input current is reduced                                                              | Input current is reduced if voltage at AC falls below VAC-LOW to keep the AC voltage above 4.5 V                                                       | 4.35 | 4.5                                               | 4.65 | V                                       |

| $V_{DPM}$                | Output voltage threshold when charging current is reduced                                                          | Bit <v_dppm> = 1</v_dppm>                                                                                                                              |      | V <sub>O(REG)</sub> –<br>100 mV                   |      | V                                       |

| DI W                     | Register <chconfig2></chconfig2>                                                                                   | Bit <v_dppm> = 0</v_dppm>                                                                                                                              |      | 4.3                                               |      |                                         |

| V <sub>BSUP1</sub>       | Enter battery supplement mode                                                                                      |                                                                                                                                                        |      | V <sub>OUT</sub> ≤<br>V <sub>BAT</sub> −<br>40 mV |      | V                                       |

| V <sub>BSUP2</sub>       | Exit battery supplement mode                                                                                       |                                                                                                                                                        |      | V <sub>OUT</sub> ≥<br>V <sub>BAT</sub> −<br>20 mV |      | V                                       |

| V <sub>O(SC1)</sub>      | Output short-circuit detection threshold, power-on                                                                 |                                                                                                                                                        | 0.8  | 0.9                                               | 1    | ٧                                       |

| V <sub>O(SC2)</sub>      | Output short-circuit detection threshold, supplement mode $V_{BAT} - V_{OUT} > V_{O(SC2)}$ indicates short-circuit |                                                                                                                                                        | 200  | 250                                               | 300  | mV                                      |

| BATTERY CHAR             | GER                                                                                                                |                                                                                                                                                        |      |                                                   |      |                                         |

| QUIESCENT CUR            | RRENT                                                                                                              |                                                                                                                                                        |      |                                                   |      |                                         |

| 1                        | Standby current into AC pin                                                                                        | V <sub>IN</sub> = 5 V; ACinputcurrent[1,0] = 11                                                                                                        |      | 60                                                | 80   | μΑ                                      |

| IACSTDBY)                | Standby current into AC pin                                                                                        | V <sub>IN</sub> = 28 V; ACinputcurrent[1,0] = 11                                                                                                       |      |                                                   | 530  | μΑ                                      |

| Icc                      | Active supply current, AC pin                                                                                      | $V_{\rm IN}$ = 5 V, no load on DCDC1, LDO1, SYS pin, VSYS[1,0] = 11; ACinputcurrent[1,0] = 10; CH_EN = 0                                               |      |                                                   | 2    | mA                                      |

| IBAT(SC)                 | Source current for BAT pin short-<br>circuit detection                                                             |                                                                                                                                                        | 4    | 7.5                                               | 11   | mA                                      |

| VBAT(SC)                 | BAT pin short-circuit detection threshold                                                                          |                                                                                                                                                        | 1.6  | 1.8                                               | 2.0  | ٧                                       |

|                          |                                                                                                                    |                                                                                                                                                        | -1%  | 4.15                                              | 1%   |                                         |

|                          |                                                                                                                    |                                                                                                                                                        | -1%  | 4.175                                             | 1%   |                                         |

|                          |                                                                                                                    |                                                                                                                                                        | -1%  | 4.20                                              | 1%   |                                         |

| .,                       | 5                                                                                                                  | Depending on setting in CHGCONFIG3 And internal EEPROM                                                                                                 | -1%  | 4.225                                             | 1%   |                                         |

| V <sub>o(BATREG)</sub>   | Battery charger voltage                                                                                            | Default = 4.2 V                                                                                                                                        | -1%  | 4.25                                              | 1%   | V                                       |

|                          |                                                                                                                    |                                                                                                                                                        | -1%  | 4.275                                             | 1%   |                                         |

|                          |                                                                                                                    |                                                                                                                                                        | -1%  | 4.30                                              | 1%   |                                         |

|                          |                                                                                                                    |                                                                                                                                                        | -1%  | 4.325                                             | 1%   |                                         |

| V <sub>LOWV</sub>        | Precharge to fast-charge transition threshold                                                                      |                                                                                                                                                        | 2.9  | 3.0                                               | 3.1  | V                                       |

$V_{SYS} = 3.6 \text{ V}, V_{DCDC1} = 2.05 \text{ V}, \text{ PFM mode, L} = 3.3 \text{ } \mu\text{H}, C_{OUTDCDC1} = 4.7 \text{ } \mu\text{F}, V_{INLDO1} = 2.05 \text{ V}, V_{LDO1} = 1.85 \text{ V}, T_{A} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ (unless otherwise noted)}$

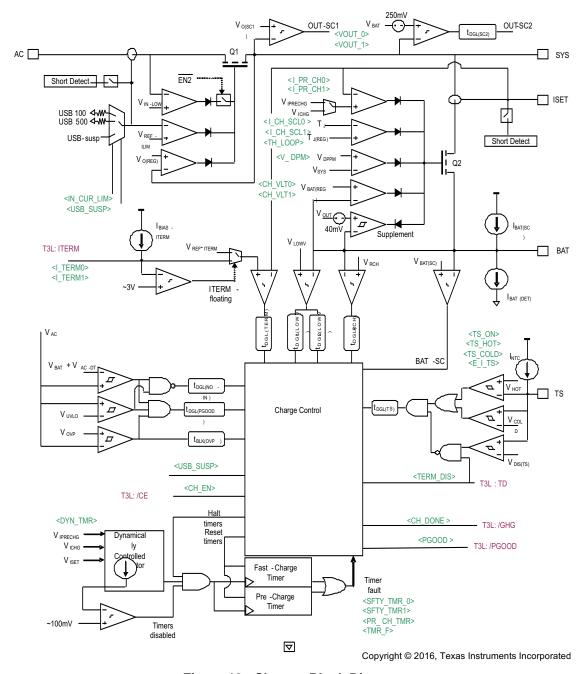

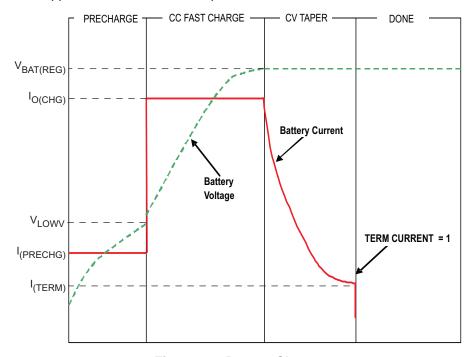

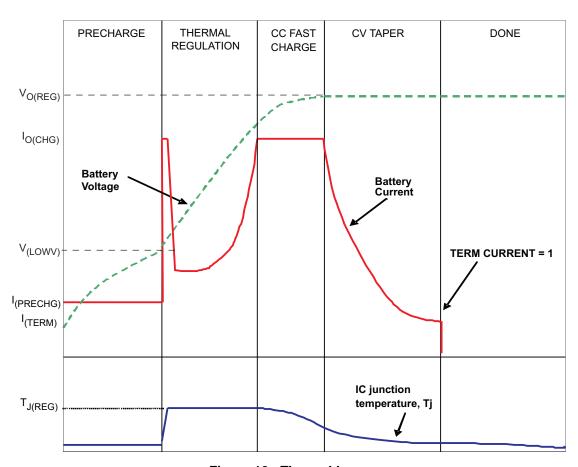

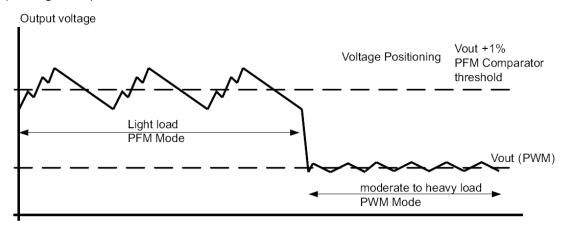

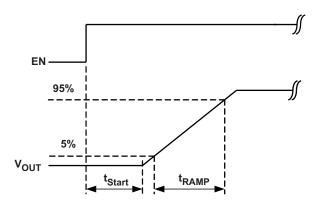

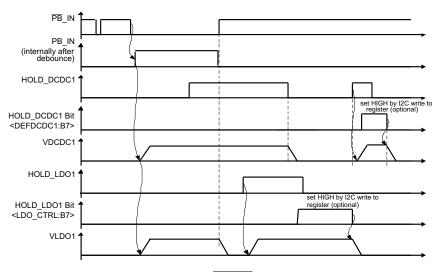

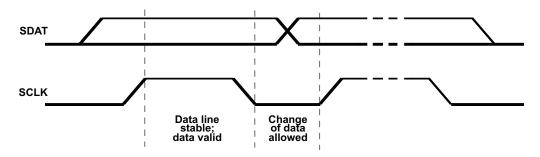

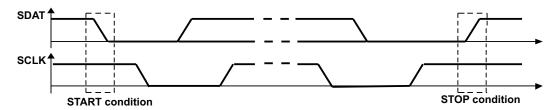

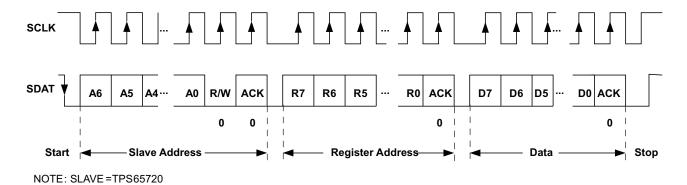

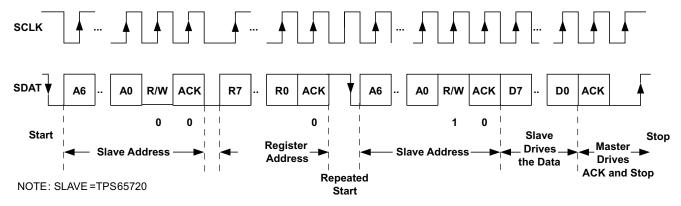

|                       | PARAMETER                              | TEST CONDITIONS                                                                                                                                | MIN                     | TYP                                   | MAX                                                                                                                                               | UNIT |