# **ST8034HN, ST8034HC**

## 24-pin smartcard interfaces

#### Datasheet - production data

### **Features**

- · Complete smartcard interface

- ISO 7816, NDS and EMV 4.3 payment systems compatible

- Three protected half-duplex bidirectional buffered I/O lines to the smartcard

- 5 V, 3 V or 1.8 V supply voltage for the smartcard (V<sub>CC</sub>), pin-selectable. Ensures controlled V<sub>CC</sub> rise and fall times and provides smart overload detection with glitch immunity.

- Very low power consumption in deep shutdown mode

- Chip select function allows the device interface to be isolated from the microcontroller signals allows parallel combination of the card interface devices (ST8034HC)

- Card clock generation by integrated crystal oscillator or from external clock source

- Card clock frequency up to 20 MHz, programmable by CLKDIV1 and CLKDIV2 pins (ST8034HN) or by CLKDIV pin (ST8034HC), with synchronous frequency changes

- Automatic activation and deactivation sequences initiated by the microcontroller

- Emergency deactivation sequences initiated by a card supply short-circuit, card take-off, falling V<sub>DD</sub>, V<sub>DDP</sub>, or V<sub>DD(INTF)</sub> or by the interface device overheating

- Voltage supply supervisors

- with a fixed threshold (V<sub>DD</sub>, V<sub>DDP</sub>)

- with an external resistor divider to set the  $V_{DD(INTF)}$  threshold (PORADJ pin)

- Multipurpose card status signal OFF

- Non-inverted card reset pin RST driven by the RSTIN input

- Thermal and short-circuit protection of all card contacts

- Card presence detection contacts debounced

- Enhanced card side ESD protection of 8 kV

- Space saving QFN24 4 x 4 x 0.8 mm package

- Temperature range -25 to +85 °C

### **Applications**

Smartcard readers for

- Set-top boxes

- Pay-TV

- Identification

- Banking

- Tachographs

# **Contents**

| 1 | Desc   | ription                                                       |

|---|--------|---------------------------------------------------------------|

| 2 | Bloc   | k diagrams 6                                                  |

| 3 | Pin d  | lescription 8                                                 |

| 4 | Maxi   | mum ratings                                                   |

| 5 | Elect  | trical characteristics11                                      |

|   | Electr | rical characteristics over recommended operating conditions   |

| 6 | Func   | tional description                                            |

|   | 6.1    | Power supplies                                                |

|   | 6.2    | Voltage supervisor                                            |

|   | 6.3    | Clock circuits                                                |

|   | 6.4    | Input and output circuits                                     |

|   | 6.5    | Shutdown mode                                                 |

|   | 6.6    | Deep shutdown mode                                            |

|   | 6.7    | Activation sequence                                           |

|   | 6.8    | Deactivation sequence                                         |

|   | 6.9    | V <sub>CC</sub> generator                                     |

|   | 6.10   | Fault detection                                               |

|   | 6.11   | VCC_SEL pin-programmed card supply voltage (V <sub>CC</sub> ) |

|   | 6.12   | Chip select (ST8034HC only)                                   |

| 7 | Pack   | age information                                               |

| 8 | Таре   | and reel information                                          |

| 9 | Revi   | sion history                                                  |

# List of tables

| Table 1.  | Device summary                                              | 5    |

|-----------|-------------------------------------------------------------|------|

| Table 2.  | Pin description ST8034HN and ST8034HC                       | 9    |

| Table 3.  | Absolute maximum ratings,                                   | . 10 |

| Table 4.  | Thermal data                                                | . 10 |

| Table 5.  | Recommended operating conditions                            | . 10 |

| Table 6.  | Supply voltages                                             | . 11 |

| Table 7.  | Card interface                                              | . 13 |

| Table 8.  | Microcontroller interface                                   |      |

| Table 9.  | Clock circuits                                              | . 17 |

| Table 10. | Protection characteristics                                  |      |

| Table 11. | Timing characteristics                                      | . 18 |

| Table 12. | Clock frequency selection                                   | . 21 |

| Table 13. | V <sub>CC</sub> selection by VCC_SEL1, VCC_SEL2 pins        | . 27 |

| Table 14. | QFN24 4 x 4 x 0.8 mm, 0.5 mm pitch package mechanical data, | . 29 |

| Table 15. | Tape and reel specification for QFN24                       | . 30 |

| Table 16. | Document revision history                                   | . 30 |

# List of figures

| Figure 1.  | Block diagram ST8034HN                                                         | 6  |

|------------|--------------------------------------------------------------------------------|----|

| Figure 2.  | Block diagram ST8034HC                                                         | 7  |

| Figure 3.  | Pin connections ST8034HN (top-through view)                                    | 8  |

| Figure 4.  | Pin connections ST8034HC (top-through view)                                    | 8  |

| Figure 5.  | Definition of duty cycle and input and output rise/fall times                  | 18 |

| Figure 6.  | Voltage supervisor, configured with adjustable V <sub>DD(INTF)</sub> threshold | 19 |

| Figure 7.  | Voltage supervisor waveforms                                                   |    |

| Figure 8.  | External clock usage                                                           | 21 |

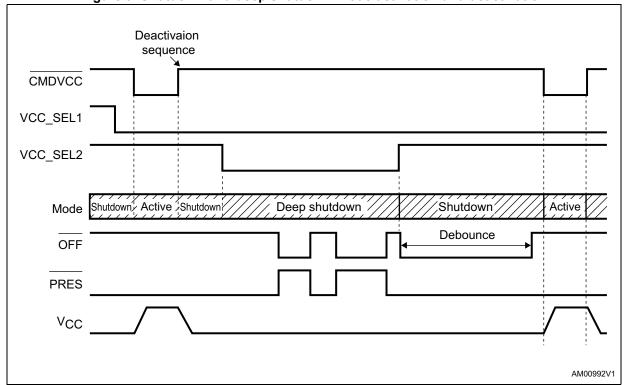

| Figure 9.  | Shutdown and deep shutdown mode activation and deactivation                    | 23 |

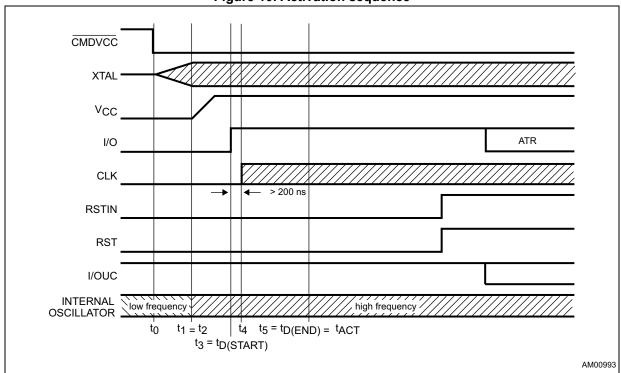

| Figure 10. | Activation sequence                                                            | 24 |

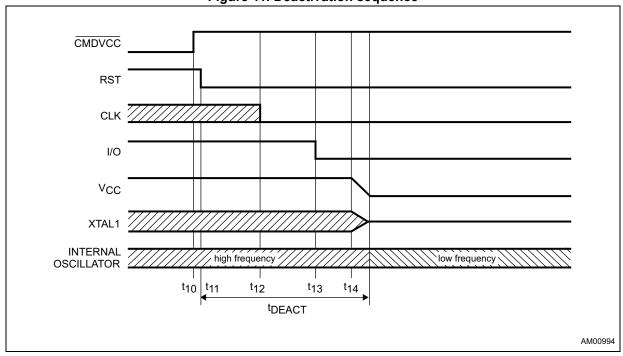

| Figure 11. | Deactivation sequence                                                          | 25 |

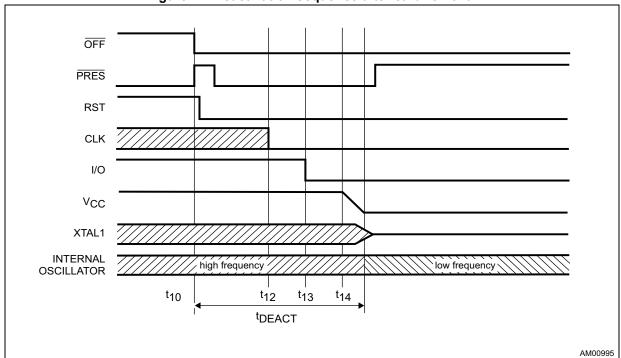

| Figure 12. | Deactivation sequence after card removal                                       | 26 |

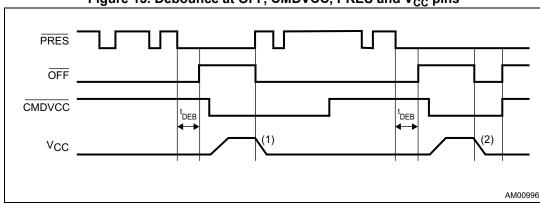

| Figure 13. | Debounce at OFF, CMDVCC, PRES and V <sub>CC</sub> pins                         | 27 |

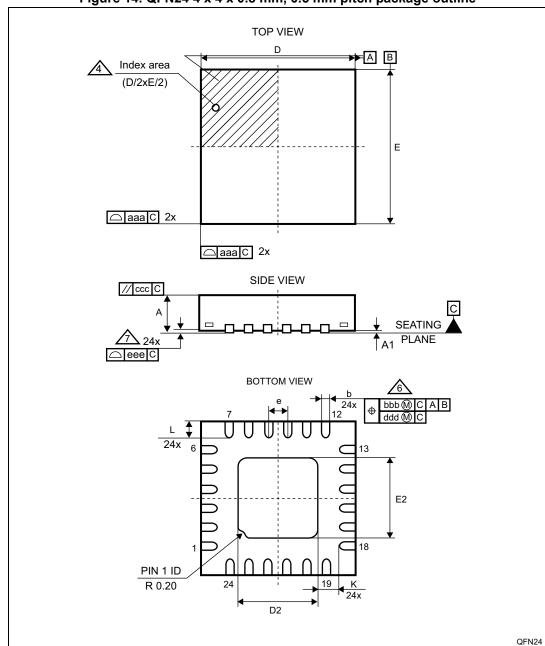

| Figure 14. | QFN24 4 x 4 x 0.8 mm, 0.5 mm pitch package outline                             |    |

| Figure 15. | QFN24 recommended footprint                                                    |    |

| Figure 16  | Carrier tane for OFN24                                                         | 30 |

# 1 Description

The ST8034HN and ST8034HC devices are complete low-cost analog interfaces for asynchronous and synchronous smartcards operating at a supply voltage of 5 V, 3 V or 1.8 V. The ST8034HN and ST8034HC devices can be placed between the card and the microcontroller to provide all supply, protection, detection and control functions, with just a few external components.

Table 1. Device summary

| Order code | PORADJ | V <sub>CC</sub><br>selection<br>pins | Chip<br>select | CLKDIV<br>inputs | NDS<br>compliant | Package                                   | Shipment      | Package<br>topmark |

|------------|--------|--------------------------------------|----------------|------------------|------------------|-------------------------------------------|---------------|--------------------|

| ST8034HNQR | V      | V                                    |                | 2                | <b>&gt;</b>      | QFN24<br>4 x 4 x 0.85 mm,<br>0.5 mm pitch | Tape and reel | 8034HN             |

| ST8034HCQR | V      | V                                    | V              | 1                | <b>V</b>         | QFN24<br>4 x 4 x 0.85 mm,<br>0.5 mm pitch | Tape and reel | 8034HC             |

# 2 Block diagrams

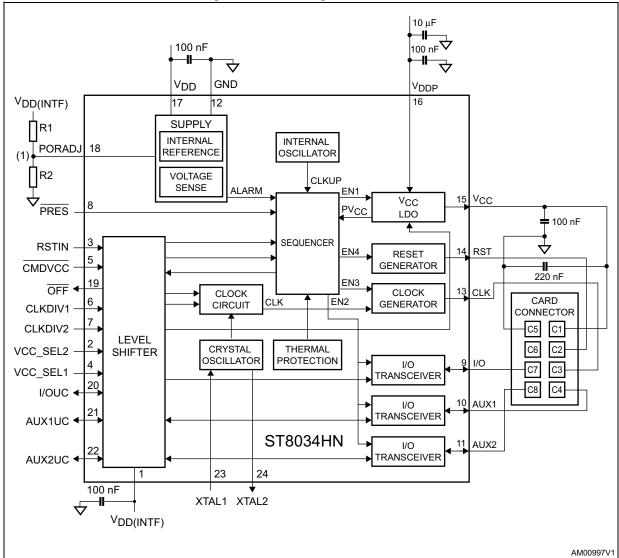

Figure 1. Block diagram ST8034HN

Optional external resistor divider. If not used, connect the PORADJ pin to V<sub>DD(INTF)</sub> for a direct V<sub>DD(INTF)</sub> voltage monitoring.

ST8034HN, ST8034HC Block diagrams

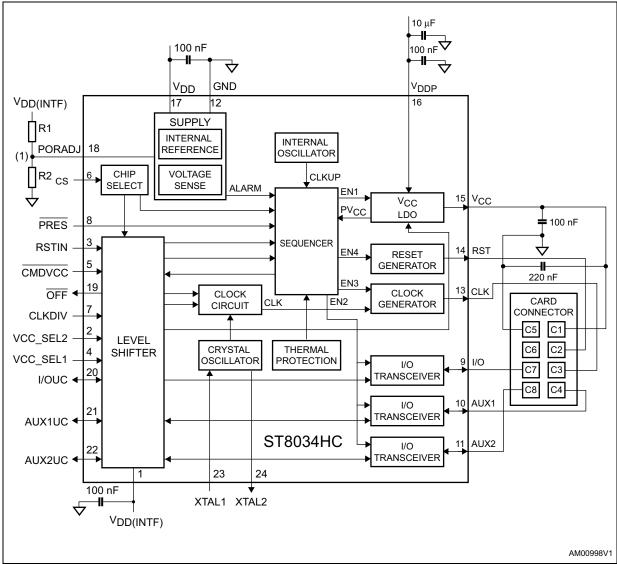

Figure 2. Block diagram ST8034HC

Optional external resistor divider. If not used, connect the PORADJ pin to V<sub>DD(INTF)</sub> for a direct V<sub>DD(INTF)</sub> voltage monitoring.

# 3 Pin description

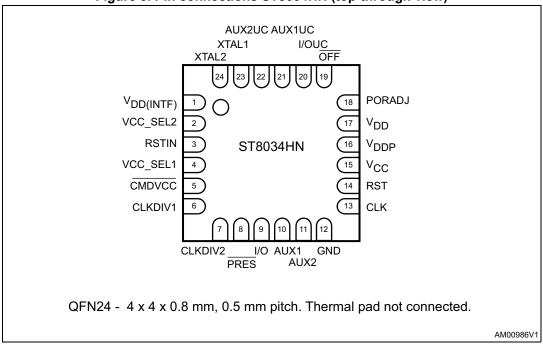

Figure 3. Pin connections ST8034HN (top-through view)

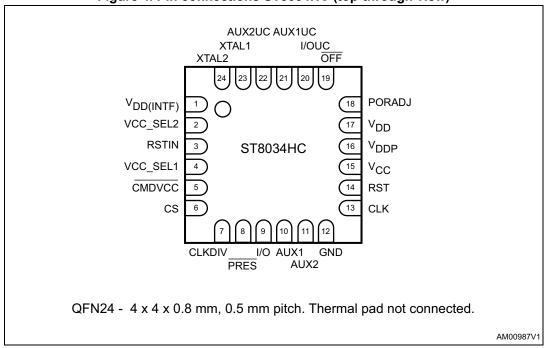

Figure 4. Pin connections ST8034HC (top-through view)

Table 2. Pin description ST8034HN and ST8034HC

| Pin<br>number | Symbol                | Ref. supply                           | Function                                                                                                       |

|---------------|-----------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------|

|               |                       | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Missassantallasiatantassantassantassa                                                                          |

| 1             | V <sub>DD(INTF)</sub> | V <sub>DD(INTF)</sub>                 | Microcontroller interface supply voltage                                                                       |

| 2             | VCC_SEL2              | V <sub>DD(INTF)</sub>                 | V <sub>CC</sub> selection control signal 5 V or 3 V (see <i>Table 13 on page 27</i> )                          |

| 3             | RSTIN                 | V <sub>DD(INTF)</sub>                 | Card reset input from microcontroller; active high                                                             |

| 4             | VCC_SEL1              | V <sub>DD(INTF)</sub>                 | V <sub>CC</sub> selection control signal 1.8 V, overrides VCC_SEL2 (see <i>Table 13 on page 27</i> )           |

| 5             | CMDVCC                | V <sub>DD(INTF)</sub>                 | Activation sequence start, input (from microcontroller, active low)                                            |

| 6             | CLKDIV1               | V <sub>DD(INTF)</sub>                 | CLK frequency division control input (together with CLKDIV2), see <i>Table 12</i> on page 21 (ST8034HN)        |

|               | CS                    | V <sub>DD(INTF)</sub>                 | Chip select input. High = device active, low = all microcontroller interface pins in high impedance (ST8034HC) |

| 7             | CLKDIV2               | V <sub>DD(INTF)</sub>                 | CLK frequency division control (together with CLKDIV1), see <i>Table 12 on page 21</i> (ST8034HN)              |

|               | CLKDIV                | V <sub>DD(INTF)</sub>                 | CLK frequency division control, see <i>Table 12 on page 21</i> (ST8034HC)                                      |

| 8             | PRES                  | V <sub>DD(INTF)</sub>                 | Card presence input (active low: PRES low = card is present). Debounced.                                       |

| 9             | I/O                   | V <sub>CC</sub>                       | Card input/output data line (C7); internal 9 k $\Omega$ pull-up resistor to V <sub>CC</sub>                    |

| 10            | AUX1                  | V <sub>CC</sub>                       | Auxiliary card input/output data line (C4); internal 9 k $\Omega$ pull-up resistor to $V_{CC}$                 |

| 11            | AUX2                  | V <sub>CC</sub>                       | Auxiliary card input/output data line (C8); internal 9 k $\Omega$ pull-up resistor to $V_{CC}$                 |

| 12            | GND                   |                                       | Ground                                                                                                         |

| 13            | CLK                   | V <sub>CC</sub>                       | Clock to card (C3)                                                                                             |

| 14            | RST                   | V <sub>CC</sub>                       | Card reset, output (C2)                                                                                        |

| 15            | V <sub>CC</sub>       |                                       | Supply voltage for the card, output (C1)                                                                       |

| 16            | V <sub>DDP</sub>      |                                       | LDO supply voltage input (for V <sub>CC</sub> generation)                                                      |

| 17            | $V_{DD}$              |                                       | Control logic supply voltage input                                                                             |

| 18            | PORADJ                | V <sub>DD(INTF)</sub>                 | Power-on reset threshold adjustment input (with an optional external resistor divider)                         |

| 19            | OFF                   | V <sub>DD(INTF)</sub>                 | Interrupt to microcontroller (active low output); internal 20 k $\Omega$ pull-up resistor to $V_{DD(INTF)}$    |

| 20            | I/OUC                 | V <sub>DD(INTF)</sub>                 | Microcontroller data I/O line (with internal 10 k $\Omega$ pull-up resistor connected to $V_{DD(INTF)}$ )      |

| 21            | AUXUC1                | V <sub>DD(INTF)</sub>                 | Auxiliary microcontroller input/output data line; internal 10 k $\Omega$ pull-up resistor to $V_{DD(INTF)}$    |

| 22            | AUXUC2                | V <sub>DD(INTF)</sub>                 | Auxiliary microcontroller input/output data line; internal 10 k $\Omega$ pull-up resistor to $V_{DD(INTF)}$    |

| 23            | XTAL1                 | $V_{DD}$                              | Crystal or external clock input                                                                                |

| 24            | XTAL2                 | $V_{DD}$                              | Crystal connection (leave this pin open if external clock is used)                                             |

# 4 Maximum ratings

Table 3. Absolute maximum ratings<sup>(1)</sup>, <sup>(2)</sup>

| Symbol                  | Parameter                                                                                                                                                  | Min. | Max. | Unit |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>DD</sub>         | Supply voltage, logic                                                                                                                                      | -0.3 | 6    | V    |

| V <sub>DDP</sub>        | DDP Supply voltage, power                                                                                                                                  |      | 6    | V    |

| V <sub>DD(INTF)</sub>   | Supply voltage, interface                                                                                                                                  | -0.3 | 6    | V    |

| V <sub>IN</sub>         | Input voltage on XTAL1, XTAL2, RSTIN, I/OUC, AUX1UC, AUX2UC, CLKDIV1, CLKDIV2, CS, VCC_SEL1, VCC_SEL2, PORADJ, CMDVCC, OFF, PRES, I/O, AUX1, and AUX2 pins | -0.3 | 6    | V    |

| V <sub>ESD (HBM)</sub>  | Human body model (HBM) on card lines - I/O, RST, V <sub>CC</sub> , CLK, and PRES pins                                                                      | -8   | 8    | kV   |

| ,                       | Human body model (HBM), all other pins                                                                                                                     | -2   | 2    | kV   |

| V <sub>ESD (MM)</sub>   | Machine model (MM), all pins                                                                                                                               | -200 | 200  | V    |

| V <sub>ESD (FCDM)</sub> | Field charged device model (FCDM), all pins                                                                                                                | -500 | 500  | V    |

| P <sub>TOT</sub>        | Total power dissipation (T <sub>A</sub> = -25 to +85 °C)                                                                                                   |      | 0.25 | W    |

| T <sub>J(MAX)</sub>     | Maximum operating junction temperature                                                                                                                     |      | 125  | °C   |

| T <sub>STG</sub>        | Storage temperature range                                                                                                                                  | -55  | 150  | °C   |

<sup>1.</sup> Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

Table 4. Thermal data

| Symbol            | Parameter                                                                                | Test conditions | Тур. | Unit |

|-------------------|------------------------------------------------------------------------------------------|-----------------|------|------|

| R <sub>THJA</sub> | Thermal resistance junction-ambient temperature (multilayer test board - JEDEC standard) | QFN24           | 47   | °C/W |

Table 5. Recommended operating conditions

| Symbol         | Parameter                 | Test conditions | Min. | Max. | Unit |

|----------------|---------------------------|-----------------|------|------|------|

| T <sub>A</sub> | Ambient temperature range |                 | -25  | 85   | °C   |

<sup>2.</sup> All card contacts are protected against short-circuit to any other card contact.

# 5 Electrical characteristics

# Electrical characteristics over recommended operating conditions

Table 6. Supply voltages

| Symbol                | Parameter                                                    | Test conditions <sup>(1)</sup>                                                | Min.  | Тур.  | Max.                                   | Unit |  |

|-----------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------|-------|-------|----------------------------------------|------|--|

| Device sup            | pply voltages                                                |                                                                               |       |       |                                        |      |  |

| V <sub>DD</sub>       | Supply voltage, logic                                        |                                                                               | 2.7   | 3.3   | 3.6 <sup>(2)</sup>                     | V    |  |

|                       | O                                                            | V <sub>CC</sub> = 5 V                                                         | 4.85  | 5     | 5.5                                    | .,   |  |

| $V_{DDP}$             | Supply voltage, power                                        | V <sub>CC</sub> = 3 V or 1.8 V                                                | 3     | 3.3   | 5.5                                    | V    |  |

| V <sub>DD(INTF)</sub> | Supply voltage,<br>microcontroller interface                 |                                                                               | 1.6   | 3.3   | V <sub>DD</sub><br>+0.3 <sup>(3)</sup> | V    |  |

|                       |                                                              | Shutdown mode                                                                 |       |       | 35                                     | ^    |  |

| $I_{DD}$              | Supply current, logic                                        | Deep shutdown mode                                                            |       |       | 12                                     | μА   |  |

|                       |                                                              | Active mode                                                                   |       |       | 2                                      | mA   |  |

|                       |                                                              | Shutdown mode, f <sub>XTAL</sub> stopped                                      |       |       | 5                                      | μΑ   |  |

| $I_{DDP}$             | Supply current, power                                        | Active mode, f <sub>CLK</sub> = f <sub>XTAL</sub> /2, no I <sub>CC</sub> load |       |       | 1.5                                    | mA.  |  |

|                       |                                                              | Active mode, $f_{CLK} = f_{XTAL}/2$ , $I_{CC} = 65 \text{ mA}$                |       |       | 70                                     |      |  |

|                       | Supply current, interface                                    | Shutdown mode                                                                 |       |       | 6                                      | μΑ   |  |

| I <sub>DD(INTF)</sub> |                                                              | Active mode                                                                   |       |       | 2                                      | mA   |  |

| Card supp             | ly voltage                                                   |                                                                               |       |       |                                        |      |  |

|                       |                                                              | Active mode, $V_{CC}$ = 5 V, $I_{CC}$ < 65 mA                                 | 4.75  | 5.0   | 5.25                                   | V    |  |

|                       |                                                              | With current pulses of 40 nAs at $I_{CC}$ < 200 mA, t < 400 ns <sup>(5)</sup> | 4.65  | 5.0   | 5.25                                   |      |  |

|                       | Card aupply voltage                                          | Active mode, V <sub>CC</sub> = 3 V, I <sub>CC</sub> < 65 mA                   | 2.85  | 3.05  | 3.15                                   |      |  |

| V <sub>CC</sub>       | Card supply voltage (output) <sup>(4)</sup>                  | With current pulses of 40 nAs at $I_{CC}$ < 200 mA, t < 400 ns <sup>(5)</sup> | 2.76  |       | 3.20                                   |      |  |

|                       |                                                              | Active mode, V <sub>CC</sub> = 1.8 V, I <sub>CC</sub> < 65 mA                 | 1.71  | 1.83  | 1.89                                   |      |  |

|                       |                                                              | With current pulses of 15 nAs at $I_{CC}$ < 200 mA, t < 400 ns <sup>(5)</sup> | 1.66  |       | 1.94                                   |      |  |

|                       | Card supply current (refer                                   | V <sub>CC</sub> = 5 V, 3 V or 1.8 V                                           |       |       | 65                                     |      |  |

| I <sub>CC</sub>       | also to Table 10: Protection characteristics on page 17)     | V <sub>CC</sub> shorted to GND                                                | 90    | 120   | 150                                    | mA   |  |

| C <sub>VCC</sub>      | V <sub>CC</sub> decoupling capacitor <sup>(4)</sup>          | V <sub>CC</sub> to GND                                                        | 160   | 320   | 530                                    | nF   |  |

|                       |                                                              | V <sub>CC</sub> = 5 V                                                         | 0.055 | 0.180 | 0.300                                  |      |  |

| SR                    | V <sub>CC</sub> slew rate (rising or falling) <sup>(4)</sup> | V <sub>CC</sub> = 3 V                                                         | 0.040 | 0.180 | 0.300                                  | V/μs |  |

|                       | 9/                                                           | V <sub>CC</sub> = 1.8 V                                                       | 0.025 | 0.180 | 0.300                                  |      |  |

|                       | •                                                            |                                                                               |       |       |                                        |      |  |

Table 6. Supply voltages (continued)

| Symbol                                | Parameter                                            | Test conditions <sup>(1)</sup>                        | Min. | Тур. | Max. | Unit |

|---------------------------------------|------------------------------------------------------|-------------------------------------------------------|------|------|------|------|

| V                                     | V <sub>CC</sub> output voltage in                    | No load                                               | -0.1 |      | 0.1  | V    |

| V <sub>CC(SHDN)</sub>                 | shutdown mode                                        | I <sub>CC</sub> = 1 mA                                | -0.1 |      | 0.3  | V    |

| I <sub>CC(SHDN)</sub>                 | V <sub>CC</sub> output current in shutdown mode      | V <sub>CC</sub> connected to GND                      |      |      | -1   | mA   |

| Device sup                            | ply voltages monitoring                              |                                                       |      |      |      |      |

|                                       |                                                      | V <sub>DD</sub> pin                                   | 2.3  | 2.4  | 2.5  |      |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Falling supply voltage threshold                     | V <sub>DDP</sub> pin (V <sub>CC</sub> = 5 V)          | 3.0  | 4.1  | 4.4  | V    |

| V <sub>TH</sub>                       |                                                      | V <sub>DDP</sub> pin (V <sub>CC</sub> = 3 V or 1.8 V) | 2.3  | 2.4  | 2.5  |      |

|                                       |                                                      | PORADJ pin                                            | 1.20 | 1.24 | 1.29 |      |

|                                       |                                                      | V <sub>DD</sub> pin                                   | 50   | 100  | 150  |      |

| V                                     | Hysteresis on supply                                 | V <sub>DDP</sub> pin (V <sub>CC</sub> = 5 V)          | 100  | 200  | 350  |      |

| V <sub>HYS</sub>                      | voltage threshold                                    | V <sub>DDP</sub> pin (V <sub>CC</sub> = 3 V or 1.8 V) | 50   | 100  | 150  | - mV |

|                                       |                                                      | PORADJ pin                                            | 10   | 20   | 30   |      |

| I <sub>I(PORADJ)</sub>                | Input current, PORADJ pin                            |                                                       | -1   |      | 1    | μА   |

| t <sub>W</sub>                        | Power-on or undervoltage reset pulse width (minimum) |                                                       | 5.1  | 8    | 10.2 | ms   |

- 1.  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V,  $V_{DDP}$  = 5 V,  $V_{DD(INTF)}$  = 3.3 V,  $f_{XTAL}$  = 10 MHz, unless otherwise noted.

- 2. The device can operate at  $V_{DD}$  supply voltage up to 5.5 V, however the specified parameters (mainly related to current consumption) are guaranteed in the basic  $V_{DD}$  range 2.7 to 3.6 V.

- 3. The device can operate at  $V_{DD(INTF)}$  supply voltage up to 5.5 V, however the specified parameters (mainly related to current consumption and input currents) are guaranteed in the basic  $V_{DD(INTF)}$  range 1.6 to 3.6 V.

- 4. Two low ESR (< 350 m $\Omega$ ) ceramic capacitors for V $_{CC}$  decoupling recommended: 100 nF ± 20% (up to 330 nF ± 20%) close to the ST8034 and 100 nF ± 20% (up to 330 nF ± 20%) close to the card.

- These current pulses are filtered by the decoupling capacitors on the V<sub>CC</sub> pin, therefore for the LDO just the mean value matters.

Table 7. Card interface

| Symbol             | Parameter                                           | Test conditions <sup>(1)</sup>                                 | Min.                  | Тур. | Max.                  | Unit |

|--------------------|-----------------------------------------------------|----------------------------------------------------------------|-----------------------|------|-----------------------|------|

| Data line          | s to the card (I/O, AUX1,                           | AUX2 pins) <sup>(2)</sup>                                      |                       |      | I                     |      |

| t <sub>D</sub>     | Delay time                                          | Falling edge on pin I/O to falling edge on I/OUC or vice versa |                       |      | 200                   | ns   |

| t <sub>W(PU)</sub> | Pull-up pulse width                                 |                                                                | 100                   |      | 400                   | ns   |

| f <sub>IO</sub>    | Input/output frequency                              |                                                                |                       |      | 1                     | MHz  |

| C <sub>I</sub>     | Input capacitance                                   |                                                                |                       |      | 10                    | pF   |

| Vo                 | Output voltage in                                   | No load                                                        | 0                     |      | 0.1                   | V    |

| ۷O                 | shutdown mode                                       | I <sub>O</sub> = 1 mA                                          | 0                     |      | 0.3                   | V    |

| I <sub>O</sub>     | Output current in shutdown mode                     | I/O connected to GND                                           |                       |      | -1                    | mA   |

| Va                 | Output voltage low                                  | I <sub>OL</sub> = 1 mA                                         | 0                     |      | 0.3                   | V    |

| V <sub>OL</sub> O  | Output voltage low                                  | I <sub>OL</sub> ≥ 15 mA (current limit)                        | V <sub>CC</sub> - 0.4 |      | V <sub>CC</sub>       | ľ    |

|                    |                                                     | No load                                                        | 0.9 V <sub>CC</sub>   |      | V <sub>CC</sub> + 0.1 |      |

| $V_{OH}$           | Output voltage high                                 | I <sub>OH</sub> < -40 μA, 5 V or 3 V                           | 0.75 V <sub>CC</sub>  |      | V <sub>CC</sub> + 0.1 | V    |

|                    |                                                     | I <sub>OH</sub> < -20 μA, 1.8 V                                | 0.75 V <sub>CC</sub>  |      | V <sub>CC</sub> + 0.1 |      |

|                    |                                                     | I <sub>OH</sub> ≥ -15 mA (current limit)                       | 0                     |      | 0.4                   |      |

| $V_{IL}$           | Input voltage low                                   |                                                                | -0.3                  |      | 0.8                   | V    |

| \/                 | Input voltage high                                  | V <sub>CC</sub> = 5 V                                          | 0.6 V <sub>CC</sub>   |      | V <sub>CC</sub> + 0.3 | V    |

| $V_{IH}$           | input voitage nigh                                  | V <sub>CC</sub> = 3 V or 1.8 V                                 | 0.7 V <sub>CC</sub>   |      | V <sub>CC</sub> + 0.3 | V    |

| $V_{HYS}$          | Hysteresis                                          | I/O pin                                                        |                       | 50   |                       | mV   |

| I <sub>IL</sub>    | Input current low                                   | I/O pin, V <sub>IL</sub> = 0 V                                 |                       |      | 750                   | μА   |

| I <sub>IH</sub>    | Input current high                                  | I/O pin, V <sub>IH</sub> = V <sub>CC</sub>                     |                       |      | 10                    | μА   |

| $t_{R(I)}$         | Input rise time                                     | V <sub>IL</sub> max. to V <sub>IH</sub> min.                   |                       |      | 0.15                  | μS   |

| t <sub>R(O)</sub>  | Output rise time                                    | $C_L \leq~80$ pF, 10% to 90%, 0 V to $V_{CC}$                  |                       |      | 0.1                   | μS   |

| $t_{F(I)}$         | Input fall time                                     | V <sub>IL</sub> max. to V <sub>IH</sub> min.                   |                       |      | 0.15                  | μS   |

| t <sub>F(O)</sub>  | Output fall time                                    | $C_L \leq~80$ pF, 10% to 90%, 0 V to $V_{CC}$                  |                       |      | 0.1                   | μS   |

| $R_{PU}$           | Pull-up resistance to $V_{\mbox{\footnotesize CC}}$ |                                                                | 7                     | 9    | 11                    | kΩ   |

| I <sub>PU</sub>    | Pull-up current (one-shot circuit active)           | V <sub>OH</sub> = 0.9 V <sub>CC</sub>                          | -8                    | -6   | -4                    | mA   |

| Reset ou           | itput to the card (RST pin                          | )                                                              |                       |      |                       |      |

| W                  | Output voltage in                                   | No load                                                        | 0                     |      | 0.1                   | W    |

| V <sub>O</sub>     | shutdown mode                                       | I <sub>O</sub> = 1 mA                                          | 0                     |      | 0.3                   | V    |

| I <sub>O</sub>     | Output current in shutdown mode                     | RST connected to GND                                           |                       |      | -1                    | mA   |

| t <sub>D</sub>     | Delay time                                          | Between RSTIN and RST; RST enabled                             |                       |      | 2                     | μS   |

**Table 7. Card interface (continued)**

| Symbol                                | Parameter                       | Test conditions <sup>(1)</sup>                  | Min.                         | Тур.                          | Max.                           | Unit       |

|---------------------------------------|---------------------------------|-------------------------------------------------|------------------------------|-------------------------------|--------------------------------|------------|

|                                       |                                 | $I_{OL}$ = 200 $\mu$ A, $V_{CC}$ = 5 $V$        | 0                            |                               | 0.3                            |            |

| V <sub>OL</sub>                       | Output voltage low              | $I_{OL}$ = 200 $\mu$ A, $V_{CC}$ = 3 V or 1.8 V | 0                            |                               | 0.2                            | ٧          |

|                                       |                                 | I <sub>OL</sub> = 20 mA (current limit)         | V <sub>CC</sub> - 0.4        |                               | V <sub>CC</sub>                |            |

| V <sub>OH</sub>                       | Output voltage high             | I <sub>OH</sub> = -200 μA                       | 0.9 V <sub>CC</sub>          |                               | V <sub>CC</sub>                | V          |

| VOH                                   | Output voltage high             | I <sub>OH</sub> = -20 mA (current limit)        | 0                            |                               | 0.4                            | V          |

| t <sub>R</sub>                        | Rise time                       | C <sub>L</sub> = 100 pF                         |                              |                               | 0.1                            |            |

| t <sub>F</sub>                        | Fall time                       | C <sub>L</sub> = 100 pF                         |                              |                               | 0.1                            | μS         |

| Clock or                              | itput to the card (CLK pi       | n)                                              |                              |                               |                                |            |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Output voltage in               | No load                                         | 0                            |                               | 0.1                            | V          |

| Vo                                    | shutdown mode                   | I <sub>O</sub> = 1 mA                           | 0                            |                               | 0.3                            |            |

| I <sub>O</sub>                        | Output current in shutdown mode | CLK connected to GND                            |                              |                               | -1                             | mA         |

| M                                     | Outrot valtage leve             | I <sub>OL</sub> = 200 μA                        | 0                            |                               | 0.3                            | V          |

| V <sub>OL</sub>                       | Output voltage low              | I <sub>OL</sub> = 70 mA (current limit)         | V <sub>CC</sub> - 0.4        |                               | V <sub>CC</sub>                | ] <u> </u> |

| ) / Ot                                | Output voltage high             | I <sub>OH</sub> = -200 μA                       | 0.9 V <sub>CC</sub>          |                               | V <sub>CC</sub>                | V          |

| V <sub>OH</sub>                       | Output voltage high             | I <sub>OH</sub> = -70 mA (current limit)        | 0                            |                               | 0.4                            | V          |

| t <sub>R</sub>                        | Rise time <sup>(3)</sup>        | C <sub>L</sub> = 30 pF                          |                              |                               | 16                             | ns         |

| t <sub>F</sub>                        | Fall time <sup>(3)</sup>        | C <sub>L</sub> = 30 pF                          |                              |                               | 16                             | ns         |

| f <sub>CLK</sub>                      | Frequency on pin CLK            | Operational                                     | 0                            |                               | 20                             | MHz        |

| DC                                    | Duty cycle <sup>(3)</sup>       | C <sub>L</sub> = 30 pF                          | 45                           |                               | 55                             | %          |

| SR                                    | Slew rate (rise and fall,       | V <sub>CC</sub> = 5 V                           | 0.2                          |                               |                                | V/ns       |

| SK                                    | C <sub>L</sub> = 30 pF)         | V <sub>CC</sub> = 3 V or 1.8 V                  | 0.12                         |                               |                                | V/IIS      |

| Card det                              | ection input (PRES pin)         | (4)                                             |                              |                               |                                |            |

| V <sub>IL</sub>                       | Input voltage low               |                                                 | -0.3                         |                               | 0.3<br>V <sub>DD(INTF)</sub>   | V          |

| V <sub>IH</sub>                       | Input voltage high              |                                                 | 0.7<br>V <sub>DD(INTF)</sub> |                               | V <sub>DD(INTF)</sub><br>+ 0.3 | V          |

| V <sub>HYS</sub>                      | Hysteresis                      |                                                 |                              | 0.14<br>V <sub>DD(INTF)</sub> |                                | V          |

| I <sub>IL</sub>                       | Input current low               | 0 < V <sub>IL</sub> < V <sub>DD(INTF)</sub>     |                              |                               | 5                              | μА         |

| I <sub>IH</sub>                       | Input current high              | 0 < V <sub>IH</sub> < V <sub>DD(INTF)</sub>     |                              |                               | 5                              | μΑ         |

<sup>1.</sup>  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V,  $V_{DDP}$  = 5 V,  $V_{DD(INTF)}$  = 3.3 V,  $f_{XTAL}$  = 10 MHz, unless otherwise noted.

<sup>2.</sup> With an internal 9  $k\Omega$  pull-up resistor to  $V_{CC}.$

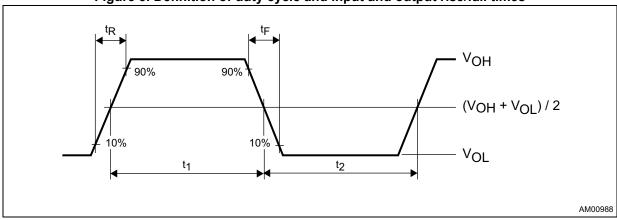

<sup>3.</sup> For rise and fall times and duty cycle definitions, see Figure 5 on page 18.

<sup>4.</sup>  $\overline{\text{PRES}}$  is active low, with an internal current source of 1.25  $\mu\text{A}$  (pull-up) to  $V_{DD(INTF)}$ .

**Table 8. Microcontroller interface**

| Symbol             | Parameter                                   | Test conditions <sup>(1)</sup>                                                    | Min.                          | Тур.                          | Max.                           | Unit |

|--------------------|---------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------|-------------------------------|--------------------------------|------|

| Data lines         | to the microcontroller (I/C                 | DUC, AUX1UC, AUX2UC pins                                                          | (2)                           |                               |                                |      |

| t <sub>D</sub>     | Delay time                                  | Falling edge on pin I/O to falling edge on I/OUC or vice versa                    |                               |                               | 200                            | ns   |

| t <sub>W(PU)</sub> | Pull-up pulse width                         |                                                                                   | 100                           |                               | 400                            | ns   |

| f <sub>IO</sub>    | Input/output frequency                      |                                                                                   |                               |                               | 1                              | MHz  |

| C <sub>I</sub>     | Input capacitance                           |                                                                                   |                               |                               | 10                             | pF   |

| V <sub>OL</sub>    | Output voltage low                          | I <sub>OL</sub> = 1 mA                                                            | 0                             |                               | 0.3                            | V    |

|                    |                                             | No load                                                                           | 0.9<br>V <sub>DD(INTF)</sub>  |                               | V <sub>DD(INTF)</sub><br>+ 0.1 |      |

| $V_{OH}$           | Output voltage high                         | $\begin{array}{l} I_{OH} \leq \ -40 \ \mu A; \\ V_{DD(INTF)} > 2 \ V \end{array}$ | 0.75<br>V <sub>DD(INTF)</sub> |                               | V <sub>DD(INTF)</sub><br>+ 0.1 | V    |

|                    |                                             | $\begin{array}{l} I_{OH} \leq \ -20 \ \mu A; \\ V_{DD(INTF)} < 2 \ V \end{array}$ | 0.75<br>V <sub>DD(INTF)</sub> |                               | V <sub>DD(INTF)</sub><br>+ 0.1 |      |

| $V_{IL}$           | Input voltage low                           |                                                                                   | -0.3                          |                               | 0.3<br>V <sub>DD(INTF)</sub>   | V    |

| $V_{IH}$           | Input voltage high                          |                                                                                   | 0.7<br>V <sub>DD(INTF)</sub>  |                               | V <sub>DD(INTF)</sub><br>+ 0.3 | V    |

| $V_{HYS}$          | Hysteresis                                  | I/OUC pin                                                                         |                               | 0.14<br>V <sub>DD(INTF)</sub> |                                | V    |

| I <sub>IL</sub>    | Input current low                           | V <sub>IL</sub> = 0 V                                                             |                               |                               | 500                            | μΑ   |

| I <sub>IH</sub>    | Input current high                          | $V_{IH} = V_{DD(INTF)}$                                                           |                               |                               | 10                             | μΑ   |

| R <sub>PU</sub>    | Pull-up resistance to V <sub>DD(INTF)</sub> |                                                                                   | 8                             | 10                            | 12                             | kΩ   |

| I <sub>PU</sub>    | Pull-up current (one-shot circuit active)   | V <sub>OH</sub> = 0.9 V <sub>DD(INTF)</sub>                                       | -1                            |                               |                                | mA   |

| t <sub>R(I)</sub>  | Input rise time                             | V <sub>IL</sub> max. to V <sub>IH</sub> min.                                      |                               |                               | 0.15                           | μ\$  |

| t <sub>R(O)</sub>  | Output rise time                            | $C_L \le 30$ pF, 10% to 90%, 0 V to $V_{DD(INTF)}$                                |                               |                               | 0.1                            | μS   |

| t <sub>F(I)</sub>  | Input fall time                             | V <sub>IL</sub> max. to V <sub>IH</sub> min.                                      |                               |                               | 0.15                           | μ\$  |

| t <sub>F(O)</sub>  | Output fall time                            | $C_L \leq 30$ pF, 10% to 90%, 0 V to $V_{DD(INTF)}$                               |                               |                               | 0.1                            | μS   |

| Device cor         | ntrol inputs (CLKDIV1, CL                   | KDIV2, RSTIN, VCC_SEL1, V                                                         | CC_SEL2, C                    | S pins) <sup>(3)</sup>        |                                |      |

| V <sub>IL</sub>    | Input voltage low                           |                                                                                   | -0.3                          |                               | 0.3<br>V <sub>DD(INTF)</sub>   | V    |

| V <sub>IH</sub>    | Input voltage high                          |                                                                                   | V <sub>DD(INTF)</sub>         |                               | V <sub>DD(INTF)</sub><br>+ 0.3 | V    |

| V <sub>HYS</sub>   | Hysteresis                                  |                                                                                   |                               | 0.14<br>V <sub>DD(INTF)</sub> |                                | V    |

Table 8. Microcontroller interface (continued)

| Symbol              | Parameter                                   | Test conditions <sup>(1)</sup> | Min.                          | Тур.                          | Max.                           | Unit |

|---------------------|---------------------------------------------|--------------------------------|-------------------------------|-------------------------------|--------------------------------|------|

| I <sub>IL</sub>     | Input current low                           |                                |                               |                               | 1                              | μА   |

| I <sub>IH</sub>     | Input current high                          |                                |                               |                               | 1                              | μА   |

| Control inp         | out CMDVCC <sup>(4)</sup>                   |                                |                               |                               |                                |      |

| V <sub>IL</sub>     | Input voltage low                           |                                | -0.3                          |                               | 0.3<br>V <sub>DD(INTF)</sub>   | V    |

| V <sub>IH</sub>     | Input voltage high                          |                                | 0.7<br>V <sub>DD(INTF)</sub>  |                               | V <sub>DD(INTF)</sub><br>+ 0.3 | V    |

| V <sub>HYS</sub>    | Hysteresis                                  |                                |                               | 0.14<br>V <sub>DD(INTF)</sub> |                                | V    |

| I <sub>IL</sub>     | Input current low                           | V <sub>IL</sub> = 0 V          |                               |                               | 1                              | μΑ   |

| I <sub>IH</sub>     | Input current high                          | $V_{IH} = V_{DD(INTF)}$        |                               |                               | 1                              | μΑ   |

| f <sub>CMDVCC</sub> | Frequency at CMDVCC pin                     |                                |                               |                               | 100                            | Hz   |

| OFF output          | t <sup>(5)</sup>                            |                                | ·                             |                               |                                |      |

| V <sub>OL</sub>     | Output voltage low                          | I <sub>OL</sub> = 2 mA         | 0                             |                               | 0.3                            | V    |

| V <sub>OH</sub>     | Output voltage high                         | I <sub>OH</sub> = -15 μA       | 0.75<br>V <sub>DD(INTF)</sub> |                               |                                | V    |

| R <sub>PU</sub>     | Pull-up resistance to V <sub>DD(INTF)</sub> |                                | 16                            | 20                            | 24                             | kΩ   |

<sup>1.</sup>  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V,  $V_{DDP}$  = 5 V,  $V_{DD(INTF)}$  = 3.3 V,  $f_{XTAL}$  = 10 MHz, unless otherwise noted.

<sup>2.</sup> With an internal 10  $k\Omega$  pull-up resistor to  $V_{DD(INTF)}.$

<sup>3.</sup> For clock frequency division control (CLKDIV), see Table 12 on page 21.

<sup>4.</sup> CMDVCC is active low.

<sup>5.</sup>  $\overline{\text{OFF}}$  is an  $\underline{\text{NMOS}}$  open drain, with an internal 20 k $\Omega$  pull-up resistor to  $V_{DD(INTF)}$ . The pull-up is connected only when used (i.e. when  $\overline{\text{OFF}}$  = high), otherwise disconnected.

Table 9. Clock circuits

| Symbol                   | Parameter Test conditions                                               |                                                                              | Min.                         | Тур. | Max.                           | Unit |

|--------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------|------|--------------------------------|------|

| Internal oscill          | ator                                                                    |                                                                              |                              |      |                                |      |

| f <sub>OSC(INT)LOW</sub> | Internal cocillator fraguency                                           | Shutdown mode                                                                | 100                          | 150  | 200                            | kHz  |

| f <sub>OSC(INT)</sub>    | Internal oscillator frequency                                           | Active state                                                                 | 2                            | 2.7  | 3.2                            | MHz  |

| Crystal oscilla          | ator (XTAL1 and XTAL2 pins)                                             |                                                                              |                              |      |                                |      |

| C <sub>EXT</sub>         | External capacitances                                                   | XTAL1 and XTAL2 to GND (according to the crystal or resonator specification) |                              |      | 15                             | pF   |

| f <sub>XTAL</sub>        | External crystal frequency  Card clock reference, crystal oscillator  2 |                                                                              |                              | 26   | MHz                            |      |

| f <sub>EXT</sub>         | External clock frequency                                                | External clock on XTAL1                                                      | 0.032                        |      | 26                             | MHz  |

| t <sub>R(fEXT)</sub>     | External clock frequency rise time                                      | External clock on XTAL1                                                      |                              |      | 10                             | ns   |

| t <sub>F(fEXT)</sub>     | External clock frequency fall time                                      | External clock on XTAL1                                                      |                              |      | 10                             | ns   |

|                          |                                                                         | Crystal oscillator                                                           | rystal oscillator -0.3       |      | 0.3 V <sub>DD</sub>            |      |

| V <sub>IL</sub>          | Input voltage low                                                       | External clock on XTAL1                                                      | -0.3                         |      | 0.3<br>V <sub>DD(INTF)</sub>   | V    |

|                          |                                                                         | Crystal oscillator                                                           | 0.7 V <sub>DD</sub>          |      | V <sub>DD</sub> + 0.3          |      |

| V <sub>IH</sub>          | Input voltage high                                                      | External clock on XTAL1                                                      | 0.7<br>V <sub>DD(INTF)</sub> |      | V <sub>DD(INTF)</sub><br>+ 0.3 | V    |

<sup>1.</sup>  $T_A = 25$  °C,  $V_{DD} = 3.3$  V,  $V_{DDP} = 5$  V,  $V_{DD(INTF)} = 3.3$  V,  $f_{XTAL} = 10$  MHz, unless otherwise noted.

**Table 10. Protection characteristics**

| Symbol               | Parameter                              | Test conditions <sup>(1)</sup> | Min. | Тур. | Max. | Unit |

|----------------------|----------------------------------------|--------------------------------|------|------|------|------|

|                      |                                        | I/O pin                        | -15  |      | 15   |      |

| I <sub>OLIM</sub>    | Output current limit <sup>(2)</sup>    | CLK pin                        | -70  |      | 70   | mA   |

|                      |                                        | RST pin                        | -20  |      | 20   |      |

| I <sub>SD(VCC)</sub> | Limit and shutdown card supply current | V <sub>CC</sub> pin            | 90   | 120  | 150  | mA   |

| T <sub>SD</sub>      | Shutdown junction temperature          |                                |      | 150  |      | °C   |

<sup>1.</sup>  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V,  $V_{DDP}$  = 5 V,  $V_{DD(INTF)}$  = 3.3 V,  $f_{XTAL}$  = 10 MHz, unless otherwise noted.

<sup>2.</sup> All card contacts are protected against short-circuit to any other card contact.

| Table 11. Timin | g characteristics |

|-----------------|-------------------|

|-----------------|-------------------|

| Symbol                  | Parameter                             | Test conditions <sup>(1)</sup>                             | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------------------------|------------------------------------------------------------|------|------|------|------|

| t <sub>ACT</sub>        | Activation time                       | See Figure 10 on page 24                                   | 2090 |      | 4160 | μs   |

| t <sub>DEACT</sub>      | Deactivation time                     | See Figure 11 on page 25                                   | 35   | 90   | 250  | μs   |

| t <sub>D(START)</sub> , | Delay time, CLK sent to card using an | $t_{D(START)} = t_3,$<br>see Figure 10 on<br>page 24       | 2090 | 4112 |      | -16  |

| t <sub>D(END)</sub>     | external clock                        | $t_{D(END)} = t_5,$<br>see Figure 10 on 2120 41<br>page 24 | 4160 | - µs |      |      |

| t <sub>DEB</sub>        | Debounce time                         | PRES pin                                                   | 3.2  | 4.5  | 6.4  | ms   |

<sup>1.</sup>  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V,  $V_{DDP}$  = 5 V,  $V_{DD(INTF)}$  = 3.3 V,  $f_{XTAL}$  = 10 MHz, unless otherwise noted.

Figure 5. Definition of duty cycle and input and output rise/fall times

Duty cycle (DC) =  $t_1 / (t_1 + t_2)$ .

## 6 Functional description

Throughout this document it is assumed that the reader is familiar with ISO7816 terminology.

## 6.1 Power supplies

All interface signals to the host microcontroller are referenced to  $V_{DD(INTF)}$ . All card contacts remain inactive during power-up or power-down. After powering up the device,  $\overline{OFF}$  output remains low until  $\overline{CMDVCC}$  input is set high and  $\overline{PRES}$  input is low. During power-down,  $\overline{OFF}$  output goes low when  $V_{DDP}$  falls below the  $V_{DDP}$  falling threshold voltage. The internal oscillator clock frequency  $f_{OSC(INT)}$  is used only during the activation sequence. When the card is not activated ( $\overline{CMDVCC}$  input is high), the internal oscillator is in low frequency mode to reduce power consumption.

Power-on sequence: supply voltages may be applied to the ST8034 in any sequence.

## 6.2 Voltage supervisor

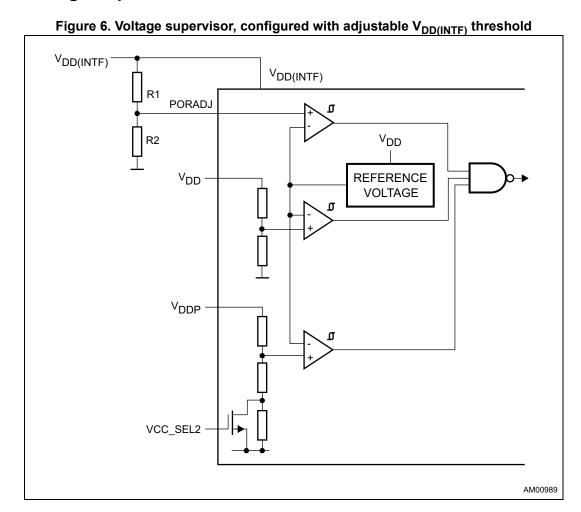

The voltage supervisor monitors the  $V_{DDP}$ ,  $V_{DD}$ , and  $V_{DD(INTF)}$  voltages and provides both power-on reset (POR) and supply dropout detection during a card session. The supervisor threshold voltages for  $V_{DDP}$  and  $V_{DD}$  are set internally, and  $V_{DD(INTF)}$  is set externally by an external resistor divider on the PORADJ pin, which provides additional voltage monitoring flexibility (this pin can be used for monitoring any external voltage, with adjustable threshold):

Undervoltage (UVLO) threshold adjustment on the PORADJ input with the resistor divider:

$V_{DD(INTF)}$  UVLO threshold (falling) = (R1+R2)/R2 x  $V_{TH(PORADJ)}$

$V_{DD(INTF)}$  UVLO threshold (rising) = (R1+R2)/R2 x ( $V_{TH(PORADJ)} + V_{HYST(PORADJ)}$ )

If the external resistor divider is not used, connect the PORADJ pin to  $V_{DD(INTF)}$ , then  $V_{DD(INTF)}$  UVLO threshold =  $V_{TH(PORADJ)}$ .

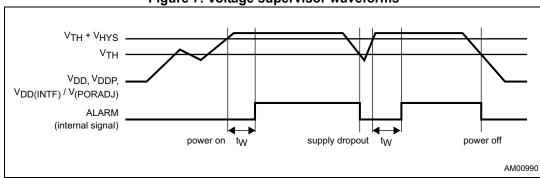

As long as  $V_{DDP}$ ,  $V_{DD}$  or  $V_{DD(INTF)}$  is less than the corresponding  $V_{TH} + V_{HYS}$ , the device remains inactive irrespective of the command line levels. After  $V_{DDP}$ ,  $V_{DD}$ , and  $V_{DD(INTF)}$  has reached a level higher than the corresponding  $V_{TH} + V_{HYS}$ , the device still remains inactive for the duration of  $t_W$ , a defined reset pulse of approximately 8 ms ( $t_W = 1024 \text{ x} + 1/f_{OSC(INT)LOW}$ ) when the output of the supervisor keeps the control logic in reset state. This is used to maintain the device in shutdown mode during the supply voltage power-on, see *Figure 7*. A deactivation sequence is performed when either  $V_{DD}$ ,  $V_{DDP}$  or  $V_{DD(INTF)}$  falls below the corresponding  $V_{TH}$ .

Figure 7. Voltage supervisor waveforms

### 6.3 Clock circuits

The clock signal for the card (CLK output) is either provided by an external clock signal connected to the XTAL1 pin or generated by a crystal connected between the XTAL1 and XTAL2 pins. The ST8034 automatically detects if an external clock is connected to XTAL1, which eliminates the need for a separate clock source selection pin. Automatic clock source detection is performed on each activation command (falling edge of CMDVCC). The presence of an external clock on the XTAL1 pin is checked during a time window defined by the internal oscillator. If the external clock is detected, the crystal oscillator is stopped. If the clock is not detected, the crystal oscillator is started. When the external clock is used, the clock signal must be present on the XTAL1 pin before the CMDVCC falling edge. If the external clock is used, connect it to XTAL1 input and leave the XTAL2 pin floating. The XTAL1 pin can not be left floating, either a crystal or an external clock source needs to be connected, or the XTAL1 pin needs to be grounded.

LOGIC

ENCLKIN

MULTIPLEXER

CRYSTAL

XTAL1

XTAL2

AM00991V1

Figure 8. External clock usage

The clock frequency is selected by the CLKDIV1 and CLKDIV2 pins and is  $f_{XTAL}$ ,  $f_{XTAL}/2$ ,  $f_{XTAL}/4$  or  $f_{XTAL}/8$  in the case of the ST8034HN or either  $f_{XTAL}$  or  $f_{XTAL}/2$  in the case of the ST8034HC, selected by the CLKDIV pin, see *Table 12*.

The frequency change is synchronous, meaning that after transition on the CLKDIV input, the present clock period is completed and after that the new whole clock period starts, therefore no clock period is shortened during the frequency switchover.

If an external crystal is used, the duty cycle on the CLK pin should be between 45% and 55%. If an external clock is connected to the XTAL1 pin, its duty cycle must be between 48% and 52% so that the CLK output duty cycle is between 45% and 55%.

| ST8034HN          |                                                   |                      |  |  |  |  |

|-------------------|---------------------------------------------------|----------------------|--|--|--|--|

| CLKDIV1 pin level | CLKDIV1 pin level CLKDIV2 pin level CLK frequency |                      |  |  |  |  |

| Low               | Low                                               | f <sub>XTAL</sub> /8 |  |  |  |  |

| Low               | High                                              | f <sub>XTAL</sub> /4 |  |  |  |  |

| High              | High                                              | f <sub>XTAL</sub> /2 |  |  |  |  |

| High              | Low                                               | f <sub>XTAL</sub>    |  |  |  |  |

|                   | ST8034HC                                          |                      |  |  |  |  |

| CLKDIV pin leve   | I                                                 | CLK frequency        |  |  |  |  |

| High              |                                                   | f <sub>XTAL</sub> /2 |  |  |  |  |

| Low               |                                                   | f <sub>XTAL</sub>    |  |  |  |  |

Table 12. Clock frequency selection

## 6.4 Input and output circuits

When the I/O and I/OUC pins are pulled high by a 9 k $\Omega$  resistor between I/O and V $_{CC}$  and/or 10 k $\Omega$  resistor between I/OUC and V $_{DD(INTF)}$ , both lines enter the idle state. The I/O pin is referenced to V $_{CC}$  and the I/OUC pin to V $_{DD(INTF)}$ , which allows operation at V $_{CC}$  level different from V $_{DD(INTF)}$  level.

The first side on which a falling edge occurs becomes the master. An anti-latch circuit disables falling edge detection on the other side, making it the slave. After a time delay  $t_D$ , the logic 0 present on the master side is sent to the slave side. When the master side returns logic 1, the slave side sends logic 1 during time delay  $(t_{W(PU)})$ . After this sequence, both master and slave sides return to their idle states.

The active pull-up feature (one-shot circuit) ensures fast low to high transitions, making the ST8034 outputs capable of delivering more than 1 mA, up to an output voltage of 0.9  $V_{CC}$ , at a load of 80 pF. At the end of the active pull-up pulse, the output voltage is dependent on the internal pull-up resistor value and load current. The current sent to and received from the card's I/O lines is limited to 15 mA at a maximum frequency of 1 MHz.

### 6.5 Shutdown mode

After a power-on reset, if  $\overline{\text{CMDVCC}}$  is high, the ST8034 enters shutdown mode, ensuring only the minimum number of circuits are active while the ST8034 waits for the microcontroller to start a session.

- All card contacts are inactive. The impedance between the contacts and GND is approximately 200  $\boldsymbol{\Omega}$

- I/OUC, AUX1UC, AUX2UC pins are in high impedance with the 10  $k\Omega$  pull-up resistor connected to  $V_{DD(INTF)}$

- The voltage generators are stopped

- The voltage supervisor is active

- The internal oscillator runs at its lowest frequency (f<sub>OSC(INT)LOW</sub>).

## 6.6 Deep shutdown mode

When the smartcard reader is inactive, the ST8034HN and ST8034HC enter a deep shutdown mode if the CMDVCC pin is forced high and the VCC\_SEL1 and VCC\_SEL2 pins are low. In deep shutdown mode, all circuits are disabled and the OFF pin follows the status of the PRES pin. Changing the status of either CMDVCC, VCC\_SEL1 or VCC\_SEL2 exits the deep shutdown mode, see *Figure* 9.

Figure 9. Shutdown and deep shutdown mode activation and deactivation

## 6.7 Activation sequence

The following device activation sequence is applied when using an external clock, also see *Figure 10*:

- 1. CMDVCC is pulled low  $(t_0)$ .

- 2. The internal oscillator is triggered (t<sub>0</sub>).

- 3. The internal oscillator changes to high frequency (t<sub>1</sub>).

- 4. V<sub>CC</sub> rises from 0 V to 1.8 V or to 3 V or to 5 V on a controlled slope (t<sub>2</sub>).

- 5. I/O, AUX1, AUX2 are driven high (t<sub>3</sub>).

- 6. The clock on the CLK output is applied to the C3 contact (t<sub>4</sub>).

- 7. RST is enabled (t<sub>5</sub>).

### Time delays

- $t_1 = t_0 + 384 \times 1/f_{OSC(INT)LOW}$

- t<sub>2</sub> = t<sub>1</sub>

- $t_3 (t_{D(START)}) = t_1 + 17T/2$

- t<sub>4</sub> = driven by host microcontroller; > t<sub>3</sub> and < t<sub>5</sub>

- $t_5 (t_{D(END)}) = t_1 + 23T/2.$

$T = 64 \times 1/f_{OSC(INT)}.$

Figure 10. Activation sequence

## 6.8 Deactivation sequence

When a session ends, the microcontroller sets  $\overline{\text{CMDVCC}}$  high. The ST8034 device then executes an automatic deactivation sequence by counting the sequencer back to the inactive state (see *Figure 11*):

- 1. RST goes low  $(t_{11})$ .

- 2. The clock is stopped, CLK is low  $(t_{12})$ .

- 3. I/O, AUX1, AUX2 are pulled low  $(t_{13})$ .

- 4.  $V_{CC}$  falls to 0 V ( $t_{14}$ ). The deactivation sequence is completed when  $V_{CC}$  reaches its inactive state.

- 5.  $V_{CC} < 0.4 \text{ V } (t_{DEACT})$ .

- 6. All card contacts become low impedance to GND. The I/OUC, AUX1UC and AUX2UC pins remain pulled up to  $V_{DD(INTF)}$  by the internal 10 k $\Omega$  pull-up resistor.

- 7. The internal oscillator returns to its low frequency mode.

### Time delays

- $t_{11} = t_{10} + 3T / 64$

- $t_{12} = t_{11} + T/2$

- $t_{13} = t_{11} + T$

- $t_{14} = t_{11} + 3T / 2$

- $t_{DEACT} = t_{11} + 3T / 2 + V_{CC}$  fall time.

$T = 64 \times 1/f_{OSC(INT)}$

Figure 11. Deactivation sequence

## 6.9 V<sub>CC</sub> generator

The LDO on the  $V_{CC}$  output is capable of supplying up to 65 mA continuously at any selected  $V_{CC}$  value (5 V, 3 V or 1.8 V). This output is overcurrent protected by the current limiter with a limit threshold value of 120 mA typ., with a glitch immunity allowing overcurrent pulses up to 200 mA with duration up to several microseconds not causing a deactivation (the average current value must stay below the specified current limit, see *Table 6 on page 11* and *Table 10 on page 17*).

A 100 nF capacitor (min.) with ESR < 350 m $\Omega$  should be tied to GND near the V<sub>CC</sub> pin and another low ESR 100 nF capacitor (min.) should be tied to GND also on the card side, near the card reader contact C1.

### 6.10 Fault detection

The fault conditions monitored by the device are:

- Short-circuit or overcurrent on the V<sub>CC</sub> pin

- Card removal during transaction

- V<sub>DD</sub> falling

- V<sub>DDP</sub> falling

- V<sub>DD(INTF)</sub> falling

- · Overheating.

There are two different fault detection situations:

- Outside card session (CMDVCC pin is high): the OFF pin is low if the card is not in the reader and high if the card is in the reader. Any voltage drop on V<sub>DD</sub>, V<sub>DDP</sub> or V<sub>DD(INTF)</sub> is detected by the voltage <u>supervisor</u>. This generates an internal power-on reset pulse but does not act upon the OFF pin signal. The card is not powered-up and short-circuits or overheating are not detected.

- In card session (CMDVCC pin is low): when the OFF pin goes low, the fault detection circuit triggers the automatic emergency deactivation sequence (see *Figure 12*).

On card insertion or removal, bouncing can occur on the card presence switch (i.e. on the PRES signal). Therefore a debouncing feature is integrated into the ST8034 (4.5 ms typically,  $t_{DEB} = 640 \times 1/f_{OSC(INT)LOW}$ ). See *Figure 13*.

On card insertion, the  $\overline{\text{OFF}}$  pin goes high after the debounce time has elapsed. When the card is extracted, the automatic card deactivation sequence is performed on the first high to low transition on the PRES pin. After this, the  $\overline{\text{OFF}}$  pin goes low.

Figure 12. Deactivation sequence after card removal

Figure 13. Debounce at OFF, CMDVCC, PRES and V<sub>CC</sub> pins

- 1. Deactivation caused by card withdrawal.

- 2. Deactivation caused by short-circuit on card side.

## 6.11 VCC\_SEL pin-programmed card supply voltage (V<sub>CC</sub>)

The card supply voltage ( $V_{CC}$ ) is selected by the VCC\_SEL1 and VCC\_SEL2 inputs, see *Table 13*.

|                    | <u> </u>           |                 |

|--------------------|--------------------|-----------------|

| VCC_SEL1 pin level | VCC_SEL2 pin level | V <sub>CC</sub> |

| Low                | x <sup>(1)</sup>   | 1.8 V           |

| High               | High               | 5 V             |

| High               | Low                | 3 V             |

Table 13. V<sub>CC</sub> selection by VCC\_SEL1, VCC\_SEL2 pins

## 6.12 Chip select (ST8034HC only)

The chip select (CS) input pin of the ST8034HC replaces the CLKDIV1 pin and is active high, meaning normal operation of the device when CS is in logic high state. When the CS pin goes low, the status of the ST8034HC device is frozen (i.e. status of control inputs RSTIN, CMDVCC, CLKDIV, VCC\_SEL1 and VCC\_SEL2 is latched) and the I/OUC, AUX1UC, and AUX2UC pins on the microcontroller interface go into high impedance mode (with pull-up resistors to  $V_{\rm DD(INTF)}$ ), not transferring any data to or from the card. The  $\overline{\rm OFF}$  output pin also goes into high impedance mode. This allows the microcontroller to share interface pins among multiple smartcard interfaces connected in parallel. Status and all the ST8034HC device functions (including the card) are maintained for immediate use when the CS goes high again. For this reason clock input is not affected by the chip select, the clock is provided to the ST8034HC device and to the card even when the CS is low.

x = "don't care". However keep in mind that combination VCC\_SEL1 = VCC\_SEL2 = GND and CMDVCC = high initiates deep shutdown mode.

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

Figure 14. QFN24 4 x 4 x 0.8 mm, 0.5 mm pitch package outline

Table 14. QFN24 4 x 4 x 0.8 mm, 0.5 mm pitch package mechanical data $^{(1)}$ ,  $^{(2)}$

| Min.         Typ.         Max.           A         0.80         0.90         1.00           A1         0.00         0.02         0.05           b         0.18         0.25         0.30 | Note |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| A1 0.00 0.02 0.05                                                                                                                                                                        | (3)  |

|                                                                                                                                                                                          | (3)  |

| b 0.18 0.25 0.30                                                                                                                                                                         | (3)  |

|                                                                                                                                                                                          | 1    |

| D 3.90 4.00 4.10                                                                                                                                                                         |      |

| E 3.90 4.00 4.10                                                                                                                                                                         |      |

| e 0.5 ref.                                                                                                                                                                               |      |

| D2 1.95 2.10 2.20                                                                                                                                                                        |      |

| E2 1.95 2.10 2.20                                                                                                                                                                        |      |