4 x 80W digital input class-D automotive audio amplifier with Hi-Fi audio quality, advanced diagnostics, 2 MHz switching frequency and High Resolution Bandwidth

### LQFP64 (exposed pad up)

Product status link

HFDA801A

**Product summary**

**Package**

LQFP64

(exp. pad

Order code

HFDA801A-

VYY

HFDA801A-

VYT

Packing

Tape&Reel

#### **Features**

- AEC-Q100 qualification on going

- · Integrated 120 dB D/A conversion

- I<sup>2</sup>S and TDM digital input (up to 16 CH TDM)

- Selectable input sample rate frequency (44.1/48/96/192 kHz)

- Wide supply operating range: 4.5 V 2518 V (5 V min at turn-on transition)

- PWM 2 MHz switching PWM:

- Reduced size and cost of output LC

- · High Resolution Bandwidth support:

- Up to 40 kHz (I<sup>2</sup>S 96 kHz) with attenuation [0 dB, -2 dB]

- Up to 80 kHz (I<sup>2</sup>S 192 kHz) with attenuation [0 dB, -2 dB]

- 4 I<sup>2</sup>C addresses

- 4  $\Omega$ , 2  $\Omega$ , 1  $\Omega$  driving with output channels parallelization

- MOSFET power outputs allowing high output power capability:

- Typ 4 x 30 W /4  $\Omega$  @ 14.4 V, 1 kHz THD = 10%

- Typ 4 x 25 W /4  $\Omega$  @ 14.4 V, 1 kHz THD = 1%

- Typ 4 x 50 W/2 Ω @ 14.4 V 1 kHz THD =10 %

- Typ 4 x 80 W/4 Ω @ 25V V, 1 kHz THD =10 %

- I<sup>2</sup>C full configurability and diagnostic:

- 4 x Thermal warning and average junction temperature measurement on I<sup>2</sup>C (8 bits)

- AC and DC diagnostic (independent of channel)

- OCP protection scheme configurable (4 x OCP limit selectable)

- Mute time configuration

- DIM (digital impedance meter)

- Feedback after filter configuration

- · Capability to run complete diagnostic in play:

- Short to GND/VCC

- DC offset detector

- · Extremely Low noise:

- 13 μV A-weighted; 20 kHz (high gain) typ

- Very low THD:

- 0.02% at 1 W 1 kHz on 4 and 2 Ω loads typ

- $\,$  0.08% 20-20 kHz (full audio band) on 4 and 2  $\Omega$  loads (1 W)

- CD/Diag pin (3 selectable CD thresholds)

- Synchronization output pin (only with TDM input stream, on I<sup>2</sup>Sdata2)

- Channel independent Mute/Play/Gain selection/Diagnostic

- · Real Time current monitor

- · Open Load in play

- Battery load dump compatible (40 V)

- Immune to pop/tick noise at turn on /off, battery variations (inside the operative range), during diagnostic

- EMI compliance evaluated according to CISPR25

- Legacy (no I<sup>2</sup>C mode)

- · Integrated short circuit protections

- ESD integrated protections (2 kV HBM, 500 V / 750 V corner CDM)

- LQFP64 exposed pad up package

#### **Description**

HFDA801A is the new ST class-D audio amplifier, specifically designed for automotive applications in the latest BCD technology. The HFDA801A integrates a 24-bits 120 dB DAC conversion, and features 2 MHz switching PWM class D output stage. This configuration enables the design of a compact and inexpensive application, reaching at the same time outstanding level of audio performances. HFDA801A supports wide band applications (80 kHz), with extremely low level of noise and low THD. Moreover it features the most complete diagnostic matrix, including full diagnostic in play to support the most demanding OEM requirements in terms of speaker control and system robustness/ reliability. HFDA801A supports start stop cranking down to 4.5 V (5 V at turn on) and it is housed in a very compact and thin LQFP 10x10 package. Thus the HFDA801A is suitable for any level of automotive application.

DB4402 - Rev 1 page 2/17

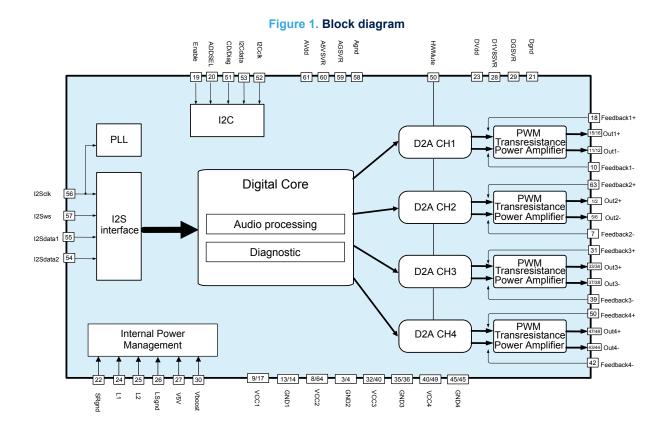

# 1 Block diagram and pins description

DB4402 - Rev 1 page 3/17

Figure 2. Pin connection diagram (top view)

Table 1. Pins list description

| #  | Pin   | Function                                   |

|----|-------|--------------------------------------------|

| 1  | OUT2+ | Channel 2, half bridge plus, Output        |

| 2  | OUT2+ | Channel 2, half bridge plus, Output        |

| 3  | GND2+ | Channel 2, half bridge plus, Power Ground  |

| 4  | GND2- | Channel 2, half bridge minus, Power Ground |

| 5  | OUT2- | Channel 2, half bridge minus, Output       |

| 6  | OUT2- | Channel 2, half bridge minus, Output       |

| 7  | FB2-  | Channel 2, half bridge minus, Feedback     |

| 8  | VCC2- | Channel 2, half bridge minus, Power Supply |

| 9  | VCC1- | Channel 1, half bridge minus, Power Supply |

| 10 | FB1-  | Channel 1, half bridge minus, Feedback     |

| 11 | OUT1- | Channel 1, half bridge minus, Output       |

DB4402 - Rev 1 page 4/17

| #  | Pin     | Function                                                    |

|----|---------|-------------------------------------------------------------|

| 12 | OUT1-   | Channel 1, half bridge minus, Output                        |

| 13 | GND1-   | Channel 1, half bridge minus, Power Ground                  |

| 14 | GND1+   | Channel 1, half bridge plus, Power Ground                   |

| 15 | OUT1+   | Channel 1, half bridge plus, Output                         |

| 16 | OUT1+   | Channel 1, half bridge plus, Output                         |

| 17 | VCC1+   | Channel 1, half bridge plus, Power Supply                   |

| 18 | FB1+    | Channel 1, half bridge plus, Feedback                       |

| 19 | Enable  | Enable pin                                                  |

| 20 | ADDSel  | Address selection pin, input                                |

| 21 | DGnd    | Digital ground                                              |

| 22 | SRGnd   | Power management ground 1                                   |

| 23 | DVdd    | Digital Power Supply                                        |

| 24 | L1      | Power management inductor side1                             |

| 25 | L2      | Power management inductor side2                             |

| 26 | LSGnd   | Power management ground 2                                   |

| 27 | V5V     | Internal 5V supply                                          |

| 28 | D1V8SVR | Positive digital supply V(SVR)+0.9 V (Internally generated) |

| 29 | DGSVR   | Negative digital supply V(SVR)-0.9 V (Internally generated) |

| 30 | Vboost  | Internal boost supply                                       |

| 31 | FB3+    | Channel 3, half bridge plus, Feedback                       |

| 32 | VCC3+   | Channel 1, half bridge plus, Power Supply                   |

| 33 | OUT3+   | Channel 3, half bridge plus, Output                         |

| 34 | OUT3+   | Channel 3, half bridge plus, Output                         |

| 35 | GND3+   | Channel 3, half bridge plus, Power Ground                   |

| 36 | GND3-   | Channel 3, half bridge minus, Power Ground                  |

| 37 | OUT3-   | Channel 3, half bridge minus, Output                        |

| 38 | OUT3-   | Channel 3, half bridge minus, Output                        |

| 39 | FB3-    | Channel 3, half bridge minus, Feedback                      |

| 40 | VCC3-   | Channel 3, half bridge minus, Power Supply                  |

| 41 | VCC4-   | Channel 4, half bridge minus, Power Supply                  |

| 42 | FB4-    | Channel 4, half bridge minus, Feedback                      |

| 43 | OUT4-   | Channel 4, half bridge minus, Output                        |

| 44 | OUT4-   | Channel 4, half bridge minus, Output                        |

| 45 | GND4-   | Channel 4, half bridge minus, Power Ground                  |

| 46 | GND4+   | Channel 4, half bridge plus, Power Ground                   |

| 47 | OUT4+   | Channel 4, half bridge plus, Output                         |

| 48 | OUT4+   | Channel 4, half bridge plus, Output                         |

| 49 | VCC4+   | Channel 4, half bridge plus, Power Supply                   |

| 50 | FB4+    | Channel 4, half bridge plus, Feedback                       |

| 51 | CD/Diag | Clipping detector and diagnostic output pin                 |

| 52 | I2CClk  | I2C Clock                                                   |

DB4402 - Rev 1 page 5/17

| #  | Pin      | Function                                                                  |

|----|----------|---------------------------------------------------------------------------|

| 53 | I2CData  | I2C Data                                                                  |

| 54 | I2SData2 | I2S/TDM Data input 2                                                      |

| 55 | I2SData1 | I2S/TDM Data input 1                                                      |

| 56 | I2Sclk   | I2S/TDM Clock input                                                       |

| 57 | I2Sws    | I2S/TDM Sync input                                                        |

| 58 | Agnd     | Analog ground                                                             |

| 59 | AGSVR    | Negative Analog Supply V(SVR)-2.5 V (Internally generated) <sup>(1)</sup> |

| 60 | A5VSVR   | Positive Analog Supply V(SVR)+2.5 V (Internally generated)                |

| 61 | AVdd     | Analog supply                                                             |

| 62 | HWMute   | Hardware mute pin                                                         |

| 63 | FB2+     | Channel 2, half bridge plus, Feedback                                     |

| 64 | VCC2+    | Channel 2, half bridge plus, Power Supply                                 |

<sup>1.</sup> Internal circuit output pin: not to be controlled externally. AMR not applicable.

DB4402 - Rev 1 page 6/17

# 2 Electrical specifications

## 2.1 Absolute maximum ratings

Table 2. Absolute maximum ratings

| Symbol                                                                                                                                   | Parameter                                              | Value       | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------|------|

| VCC                                                                                                                                      | DC supply voltage                                      | -0.3 to 32  | V    |

| $[V_{CC(x)}^+, V_{CC(x)}^-, A_{VDD}, D_{VDD}]$                                                                                           | Transient supply voltage for t = 100 ms <sup>(1)</sup> | -0.3 to 40  | V    |

| $\begin{aligned} & & & & & & & & & & & & & \\ & & & & & $                                                                                | Ground pin voltage difference                          | -0.3 to 0.3 | V    |

| FB <sub>(x)</sub> +, FB <sub>(x)</sub> -                                                                                                 | Feedback pin                                           | -0.3 to 32  | V    |

| $OUT_{(x)}$ +, $OUT_{(x)}$ -                                                                                                             | Output pin                                             | -0.3 to 32  | V    |

| L1                                                                                                                                       | Internal Regulator pin                                 | -0.3 to 32  | V    |

| L2                                                                                                                                       | Internal Regulator pin                                 | -0.3 to 40  | V    |

| I <sup>2</sup> C <sub>data</sub> , I <sup>2</sup> C <sub>clk</sub>                                                                       | I <sup>2</sup> C bus pins voltage                      | -0.3 to 5.5 | V    |

| I <sup>2</sup> S <sub>data1</sub> , I <sup>2</sup> S <sub>data2</sub> , I <sup>2</sup> S <sub>clk</sub> , I <sup>2</sup> S <sub>WS</sub> | I <sup>2</sup> S bus pins voltage                      | -0.3 to 5.5 | V    |

| Enable                                                                                                                                   | Enable pin voltage                                     | -0.3 to 5.5 | V    |

| CD/Diag                                                                                                                                  | CD/DIAG pin                                            | -0.3 to 5.5 | V    |

| HWMute                                                                                                                                   | Hardware Mute                                          | -0.3 to 5.5 | V    |

| T <sub>amb</sub>                                                                                                                         | Ambient operating temperature                          | -40 to 105  | °C   |

| $T_{stg},T_{j}$                                                                                                                          | Storage and junction temperature                       | -55 to 150  | °C   |

| ESD <sub>HBM</sub>                                                                                                                       | ESD protection HBM <sup>(2)</sup>                      | 2000        | V    |

| ESD <sub>CDM</sub>                                                                                                                       | ESD protection CDM <sup>(2)</sup>                      | 500         | V    |

<sup>1.</sup> Ramp time  $T_r = 2 \text{ ms}$

### 2.2 Thermal data

Table 3. Thermal data

| Symbol            | Parameter                                       | Value | Unit |

|-------------------|-------------------------------------------------|-------|------|

| R <sub>thjc</sub> | R <sub>th</sub> junction to case <sup>(1)</sup> | 1.26  | °C/W |

<sup>1.</sup> Top Cold Plate as per Jedec best practice guidelines (JESD51) in contact with package top side (e-pad). Ambient temperature set to 85°C.

DB4402 - Rev 1 page 7/17

<sup>2.</sup> Definition according to the international standard

### 3 General description

HFDA801A is a fully digital single chip class-D amplifier with high immunity to the demodulation filter effects. The high integration level and the on-board signal processing allow excellent audio performance to be achieved.

Thanks to the digital input and to the feedback strategy in the power stage, HFDA801A makes the amplifier immune from the output filter components non-linearity. The number and size of the external components are minimized.

HFDA801A includes: digital I<sup>2</sup>C and I<sup>2</sup>S interfaces, internal 24 bits DAC conversion, digital signal processing for interpolation and noise shaping, innovative self-diagnostic functions and automatic detection of wrong load connections or variation of the load, internal PLL for a clock generation. Moreover HFDA801A provides a breakthrough innovative digital impedance-meter which can communicate via I<sup>2</sup>C the output load value.

#### 3.1 Feedback topology and switching frequency

HFDA801A adopts an innovative feedback topology, where the LC filter is included in the feedback loop making the amplifier highly insensitive to the characteristics of such demodulation circuit. This solution optimizes the system performance in terms of THD and frequency response in any load condition.

Regardless of the big phase shifting introduced by the output filter the device shows an adequate phase margin for any load condition. The system stability has been designed considering:

- PWM switching variation (from 2.1 MHz to 2.3 MHz)

- Silicon temperature variation (from -40 to 150 °C)

- Load variation (both inductive and capacitive considered)

- · LC demodulator filter variation and tolerance

- Voltage supply variation (from 4.5 to 2518 V)

- Minimum Supply Voltage level during Turn-On transition = 5 V

The system has been designed to guarantee a phase margin > 45 degrees for any working condition.

The new feedback topology assures a strong control of voltage and current across the load making the diagnostic load detection reliable. Moreover, this topology allows to reach exceptionally good values of output damping factor.

#### 3.2 PWM frequencies

HFDA801A PWM frequency is well above the AM band, avoiding by architecture the EMC interference of PWM switching first harmonic. Moreover, this choice permits to optimize the size and cost of the external LC demodulation filter.

The PWM frequency depends on the I<sup>2</sup>S WS frequency as reported in the table below:

Table 4. PWM frequency relation with I<sup>2</sup>S WS frequency

| WS Frequency [kHz] | Nominal PWM Frequency [MHz] |

|--------------------|-----------------------------|

| 44.1               | 2.1168                      |

| 48                 | 2.304                       |

| 96                 | 2.304                       |

| 192                | 2.304                       |

#### 3.3 Load possibilities

HFDA801A supports several load possibilities and configurations. The default configuration is suitable for a 4-channels application (front/rear – left/right): 4 x 4  $\Omega$  (up to 18 V).. By means of the I<sup>2</sup>C bus bit IB1-d7,d6 it is possible to choose a 2-channels solution with parallel outputs (left/right) or a 2.1 configuration for sub-woofer application.

DB4402 - Rev 1 page 8/17

#### Possible channel configurations:

- 4 x 4 Ω (up to 25 V)

- 4 x 2 Ω (up to 18 V)

- +  $2 \times 1 \Omega$  (through channels connected in parallel; limited to 18 V)

- $2 \times 4 \Omega + 1 \times 2 \Omega$  (through parallelized channels)

DB4402 - Rev 1 page 9/17

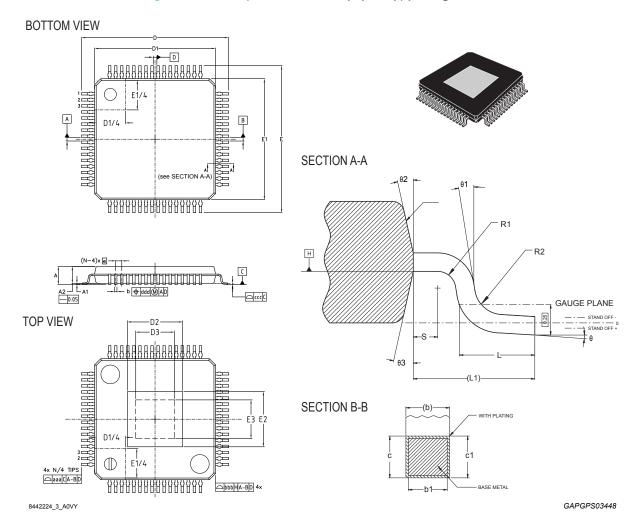

## 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

### 4.1 LQFP64 (10x10x1.4 mm exp. pad up) package information

Figure 3. LQFP64 (10x10x1.4 mm exp. pad up) package outline

Table 5. LQFP64 (10x10x1.4 mm exp. pad up) package mechanical data

| Symbol | Dimension in mm |      |      |  |

|--------|-----------------|------|------|--|

| Symbol | Min.            | Тур. | Max. |  |

| Θ      | 0°              | 3.5° | 6°   |  |

| Θ1     | 0°              | 9°   | 12°  |  |

| Θ2     | 11°             | 12°  | 13°  |  |

| Ө3     | 11°             | 12°  | 13°  |  |

| Α      | -               | -    | 1.49 |  |

DB4402 - Rev 1 page 10/17

|                      | Dimension in mm |                              |      |  |  |

|----------------------|-----------------|------------------------------|------|--|--|

| Symbol               | Min.            | Тур.                         | Max. |  |  |

| A1                   | -0.04           | -                            | 0.04 |  |  |

| A2                   | 1.35            | 1.4                          | 1.45 |  |  |

| b                    | -               | -                            | 0.27 |  |  |

| b1                   | 0.17            | 0.2                          | 0.23 |  |  |

| С                    | 0.09            | -                            | 0.2  |  |  |

| c1                   | 0.09            | 0.127                        | 0.16 |  |  |

| D                    |                 | 12.00 BSC                    |      |  |  |

| D1 <sup>(1)(2)</sup> |                 | 10.00 BSC                    |      |  |  |

| D2                   |                 | See VARIATIONS               |      |  |  |

| D3                   |                 | See VARIATIONS               |      |  |  |

| е                    |                 | 0.50 BSC                     |      |  |  |

| E                    |                 | 12.00 BSC                    |      |  |  |

| E1 <sup>(1)(2)</sup> | 10.00 BSC       |                              |      |  |  |

| E2                   | See VARIATIONS  |                              |      |  |  |

| E3                   |                 | See VARIATIONS               |      |  |  |

| L                    | 0.45            | 0.6                          | 0.75 |  |  |

| L1                   | 1.00 REF        |                              |      |  |  |

| N                    | -               | 64                           | -    |  |  |

| R1                   | 0.08            | -                            | -    |  |  |

| R2                   | 0.08            | -                            | 0.2  |  |  |

| S                    | 0.2             | -                            | -    |  |  |

|                      | Tolerance of fo | orm and position             |      |  |  |

| aaa                  | -               | 0.2                          | -    |  |  |

| bbb                  | -               | 0.2                          | -    |  |  |

| ccc                  | -               | 0.08                         | -    |  |  |

| ddd                  | -               | 0.08                         | -    |  |  |

|                      | VARIA           | ATIONS                       |      |  |  |

|                      | Pad option 6.   | 0x6.0 (T1-T3) <sup>(3)</sup> |      |  |  |

| D2                   | -               | -                            | 6.61 |  |  |

| E2                   | -               | -                            | 6.61 |  |  |

| D3                   | 4.8             | -                            | -    |  |  |

| E3                   | 4.8             | -                            | -    |  |  |

- 1. Dimensions D1 and E1 do not include mold flash or protrusions. Allowable mold flash or protrusion is "0.25 mm" per side.

- 2. The Top package body size may be smaller than the bottom package size by as much as 0.15 mm.

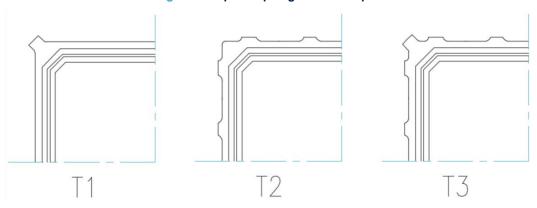

- 3. Number, dimension and position of groves shown in Figure 4 are for reference only.

DB4402 - Rev 1 page 11/17

Figure 4. Exposed-pad groove's shapes

DB4402 - Rev 1 page 12/17

# **Revision history**

Table 6. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 15-Gen-2021 | 1       | Initial release. |

DB4402 - Rev 1 page 13/17

## **Contents**

| 1     | Bloc  | ck diagram and pins description                       | 3  |  |

|-------|-------|-------------------------------------------------------|----|--|

| 2     | Elec  | Electrical specifications                             |    |  |

|       | 2.1   | Absolute maximum ratings                              | 7  |  |

|       | 2.2   | Thermal data                                          | 7  |  |

| 3     | Gen   | General description                                   |    |  |

|       | 3.1   | Feedback topology and switching frequency             | 8  |  |

|       | 3.2   | PWM frequencies                                       | 8  |  |

|       | 3.3   | Load possibilities                                    | 8  |  |

| 4 Pac |       | kage information                                      | 10 |  |

|       | 4.1   | LQFP64 (10x10x1.4 mm exp. pad up) package information | 10 |  |

| Rev   | ision | history                                               | 13 |  |

## **List of tables**

| Table 1. | Pins list description                                     | 4  |

|----------|-----------------------------------------------------------|----|

| Table 2. | Absolute maximum ratings                                  | 7  |

| Table 3. | Thermal data                                              | 7  |

| Table 4. | PWM frequency relation with I <sup>2</sup> S WS frequency | 8  |

| Table 5. | LQFP64 (10x10x1.4 mm exp. pad up) package mechanical data | 10 |

| Table 6. | Document revision history                                 | 13 |

DB4402 - Rev 1 page 15/17

# **List of figures**

| Figure 1. | Block diagram                                     | 3 |

|-----------|---------------------------------------------------|---|

| Figure 2. | Pin connection diagram (top view)                 | 4 |

| Figure 3. | LQFP64 (10x10x1.4 mm exp. pad up) package outline | ( |

| Figure 4. | Exposed-pad groove's shapes                       | 2 |

DB4402 - Rev 1 page 16/17

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DB4402 - Rev 1 page 17/17

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Audio Amplifiers category:

Click to view products by STMicroelectronics manufacturer:

Other Similar products are found below:

LV47002P-E NCP2811AFCT1G NCP2890AFCT2G SSM2377ACBZ-R7 IS31AP4915A-QFLS2-TR NCP2820FCT2G TDA1591T

TDA7563AH SSM2529ACBZ-R7 SSM2518CBZ-R7 MAX9890AETA+T TS2012EIJT NCP2809BMUTXG NJW1157BFC2

SSM2375CBZ-REEL7 IS31AP4996-GRLS2-TR STPA002OD-4WX NCP2823BFCT1G MAX9717DETA+T MAX9717CETA+T

MAX9724AEBC+TG45 LA4450L-E IS31AP2036A-CLS2-TR MAX9723DEBE+T TDA7563ASMTR AS3561-DWLT SSM2517CBZ-R7

MP1720DH-12-LF-P SABRE9601K THAT1646W16-U MAX98396EWB+ PAM8965ZLA40-13 BD37532FV-E2 BD5638NUX-TR

BD37512FS-E2 BD37543FS-E2 BD3814FV-E2 TPA3140D2PWPR TS2007EIJT IS31AP2005-DLS2-TR SSM2518CPZ-R7 AS3410-EQFP-500 FDA4100LV MAX98306ETD+T TS4994EIJT NCP2820FCT1G NCP2823AFCT2G NCS2211MNTXG CPA2233CQ16-A1

OPA1604AIPWR