# **Dual-Phase Synchronous Buck PWM Controller**

## **General Description**

The RT8810 is a dual phase synchronous buck controller which can provide users with a compact, high efficient, well protected and cost effective solution. The RT8810's integrated high driving capability MOSFET drivers makes it more attractive for high current application. The built-in bootstrap diode simplifies the circuit design and reduces external part count and PCB space. For output voltage control, the RT8810 can precisely regulate feedback voltage according to the internal reference voltage 0.6V or external reference voltage from 0.4V to 2.5V.

The MODE pin programs single phase or dual phase operation, making the RT8810 suitable for dual power input applications such as PCI-Express interface graphic cards. To set RT8810 at automatic mode, the RT8810 operates in single phase at light load condition and maintains high efficiency over a wide range of output currents. In addition, the RT8810 features adjustable gate driving voltage for maximum efficiency and optimum performance.

The RT8810 adopts lossless  $R_{DS(ON)}$  current sensing technique for channel current balance and over current protection. Other features include adjustable soft-start, adjustable operation phase, and adjustable over current threshold.

## **Ordering Information**

RT8810 🗆 🗖

-Package Type

QW: WQFN-16L 3x3 (W-Type) QW: WQFN-24L 4x4 (W-Type)

Lead Plating System

G: Green (Halogen Free and Pb Free)

Z : ECO (Ecological Element with Halogen Free and Pb free)

Product Classification

A: Only for WQFN-24L 4x4

B : Only for WQFN-16L 3x3 (With MODE Pin)

C : Only for WQFN-16L 3x3 (With REFIN Pin)

D: Only for WQFN-24L 4x4

### **Features**

- Single IC Supply Voltage: 4.5V to 13.2V

- Supports Manual / Auto Dynamic Phase Number Control

- Integrated Bootstrap Diode

- Lossless R<sub>DS(ON)</sub> Current Sensing for Current Balance

- Adjustable Operation Frequency: 100kHz to 1MHz

- Adjustable Over Current Protection

- Capacitor Programmable Soft-Start

- Support 0% to 80% Duty Cycle

- Selectable Internal/External V<sub>REF</sub>

- Voltage Mode PWM Control with External Feedback Loop Compensation

- Phase Crosstalk Jitter Suspend (CJS<sup>™</sup>)

- Programmable Quick Response

- Driver Shoot Through Protection

- Supports Current Reporting

- 16-Lead WQFN and 24-Lead WQFN Packages

- RoHS Compliant and Halogen Free

## **Applications**

- GPU Core Power

- Desktop PC Memory, V<sub>TT</sub> Power

- Low Output Voltage, High Power Density DC/DC Converters

- Voltage Regulator Modules

### Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

## **Marking Information**

EL= : Product Code YMDNN : Date Code

## RT8810AZQW

EL: Product Code YMDNN: Date Code

### RT8810BGQW

JU=: Product Code YMDNN: Date Code

### RT8810BZQW

JU: Product Code

YMDNN: Date Code

### RT8810CGQW

JV=: Product Code YMDNN: Date Code

### RT8810CZQW

JV : Product Code YMDNN : Date Code

### RT8810DGQW

02= : Product Code YMDNN : Date Code

### RT8810DZQW

02 : Product Code YMDNN : Date Code

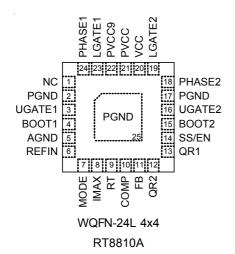

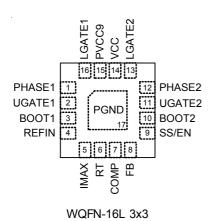

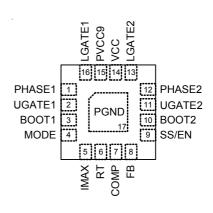

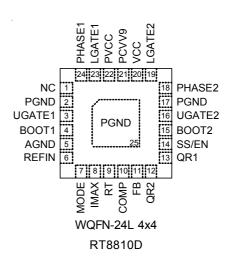

## **Pin Configurations**

### (TOP VIEW)

RT8810C

WQFN-16L 3x3 RT8810B

# **Typical Application Circuit**

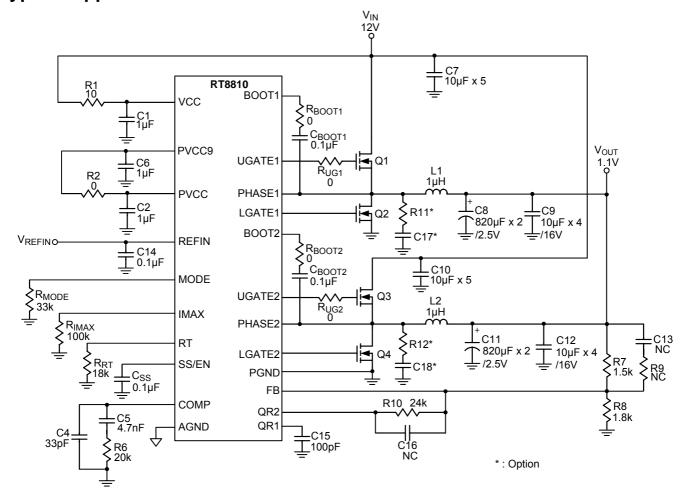

Figure 1. RT8810A/D

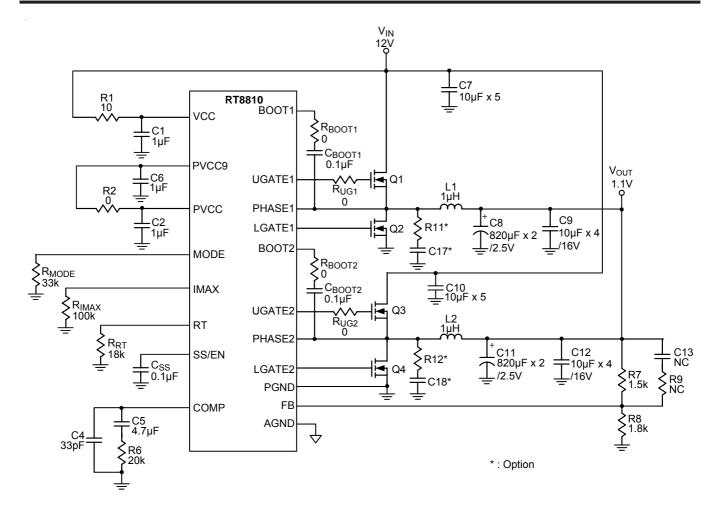

Figure 2. RT8810B

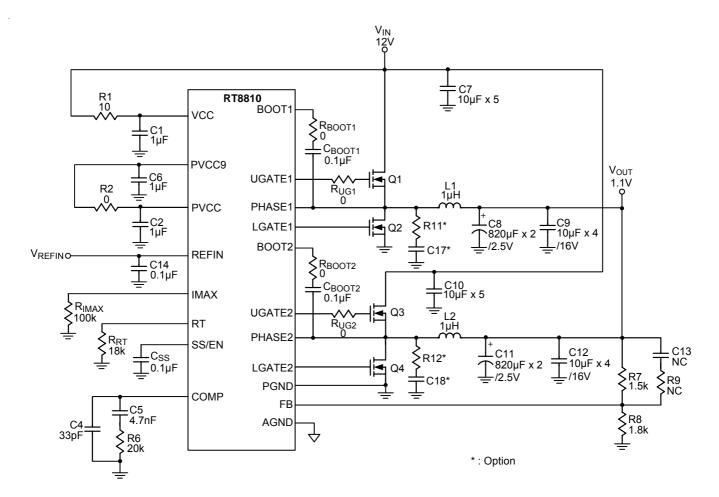

Figure 3. RT8810C

# Functional Pin Description

| Pin No.             |                               |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|---------------------|-------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| WQFN-16L<br>3x3     | WQFN-24L<br>4x4               | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                     | 1                             | NC       | No Internal Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 17<br>(Exposed Pad) | 2, 17,<br>25<br>(Exposed Pad) | PGND     | Power Ground for the IC. These pins are ground returns for the gate drivers. Tie these pins to the ground island/plane through the lowest impedance connection available. The exposed pad must be soldered to a large PCB and connected to PGND for maximular power dissipation.                                                                                                                                                                                                                                                                                                        |  |  |

| 2                   | 3                             | UGATE1   | Upper Gate Driver Output for Channel 1. Connect this pin to the gate of upper MOSFET. This pin is monitored by the adaptive shoot through protection circuitry to determine when the upper MOSFET has turned off.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 3                   | 4                             | BOOT1    | Bootstrap Supply for the Floating Upper Gate Driver of Channel 1. Connect the bootstrap capacitor $C_{BOOT}$ 1 between BOOT1 pin and the PHASE1 pin to form a bootstrap circuit. The bootstrap capacitor provides the charge to turn on the upper MOSFET.                                                                                                                                                                                                                                                                                                                               |  |  |

|                     | 5                             | AGND     | All voltages levels are measured with respect to this pin. Tie this pin to the ground island/plane through the lowest impedance connection available.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 4<br>(RT8810C)      | 6                             | REFIN    | External Reference Input. This is the input pin for the external reference voltage. If external reference voltage is not available, leave this pin open for default internal 0.6V reference.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 4<br>(RT8810B)      | 7                             | MODE     | Operation Phase Control Input. Connect a resistor R <sub>MODE</sub> from the pin to GND to set the threshold current level for single and duphase operations. The RT8810 operates in dual phase if the output current is higher than the threshold current level; in single phase the output current is lower than the threshold current level; see the related sections for detail. Tie this pin to GND for continuous sing phase operation. Leave this pin open for continuous dual phatoperation. Both upper and lower switches of PHASE2 are turned when operating in single phase. |  |  |

| 5                   | 8                             | IMAX     | Output Current Indication. Connect this pin to ground with a resistor to set the output over current protection level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

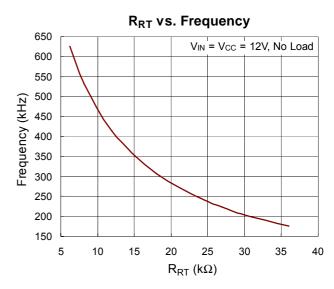

| 6                   | 9                             | RT       | Operation Frequency Setting. Connect a resistor between this pin and AGND to set the operation frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 7                   | 10                            | COMP     | Error Amplifier Output. This is the output of the Error Amplifier (E. and the non-inverting input of the PWM comparators. Use this pin combination with the FB pin to compensate the voltage-contifeedback loop of the converter                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 8                   | 11                            | FB       | Feedback Voltage. This pin is the inverting input to the error amplifier. A resistor divider from the output to GND is used to set the regulation voltage.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                     | 12                            | QR2      | Quick Response Setting Pin for Load Transition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                     | 13                            | QR1      | Quick Response Setting Pin for Load Transition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 9                   | 14                            | SS/EN    | Soft-Start Output. Connect a capacitor from this pin to GND to se the soft-start interval. Pulling this pin low to 0.4V will shut down the RT8810.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

To be continued

| Pin No.     |                                    |          |                                                                                                                                                                                                                                                                                                      |  |  |

|-------------|------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| WQFN-16L    | WQFN-24L                           | Pin Name | Pin Function                                                                                                                                                                                                                                                                                         |  |  |

| 3 <b>x3</b> | <b>4x4</b><br>15                   | BOOT2    | Bootstrap Supply for the Floating Upper Gate Driver of Channel Connect the bootstrap capacitor between BOOT2 pin and the PHAS pin to form a bootstrap circuit. The bootstrap capacitor provides to charge to turn on the upper MOSFET.                                                               |  |  |

| 11          | 16                                 | UGATE2   | Upper Gate Driver Output for Channel 2. Connect this pin to the gate of upper MOSFET. This pin is monitored by the adaptive shoot through protection circuitry to determine when the upper MOSFET has tumed off.                                                                                     |  |  |

| 12          | 18                                 | PHASE2   | Switch Node for Channel 2. Connect this pin to the source of the upp MOSFET and the drain of the lower MOSFET. This pin is used as the si for the UGATE2 driver. This pin is also monitored by the adaptive sho through protection circuitry to determine when the upper MOSFET has turned off.      |  |  |

| 13          | 19                                 | LGATE2   | Lower Gate Driver Output for Channel 2. Connect this pin to the gate lower MOSFET. This pin is monitored by the adaptive shoot throuprotection circuitry to determine when the lower MOSFET has turn off.                                                                                            |  |  |

| 14          | 20                                 | vcc      | Supply Voltage. This pin is the input pin of the internal 9V LDO, where provides current for PVCC9 and PVCC pins. Place a minimum ceramic capacitor physically near the pin to locally bypass the support voltage.                                                                                   |  |  |

|             | 21<br>(RT8810A)<br>22<br>(RT8810D) | PVCC     | Supply Input. This pin receives a supply voltage from 4.5V to 13.2V and provides bias current for the internal control circuit. Physically place a minimum $1\mu\text{F}$ ceramic capacitor near it. This pin to bypass it.                                                                          |  |  |

| 15          | 22<br>(RT8810A)<br>21<br>(RT8810D) | PVCC9    | Supply Input. This pin is the output of the internal 9V LDO regulator. It provides current for lower gate drivers and bootstrap current for upper drivers.                                                                                                                                           |  |  |

| 16          | 23                                 | LGATE1   | Lower Gate Driver Output for Channel 1. Connect this pin to the gate of lower MOSFET. This pin is monitored by the adaptive shoot through protection circuitry to determine when the lower MOSFET has turn off.                                                                                      |  |  |

| 1           | 24                                 | PHASE1   | Switch Node for Channel 1. Connect this pin to the source of the upper MOSFET and the drain of the lower MOSFET. This pin is used as the sink for the UGATE driver. This pin is also monitored by the adaptive shoot through protection circuitry to determine when the upper MOSFET has turned off. |  |  |

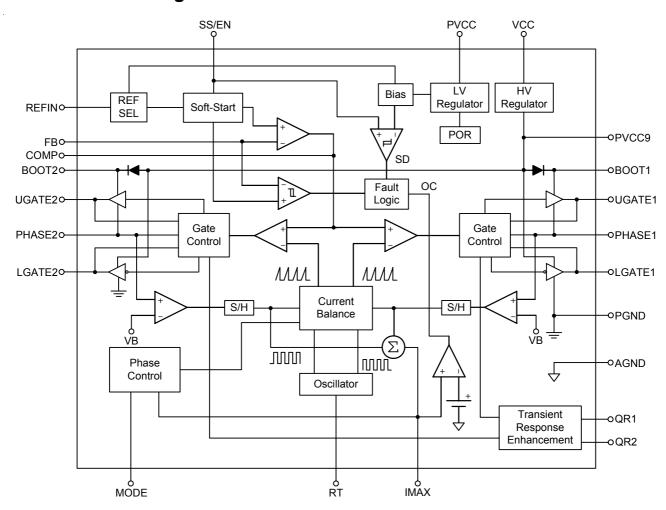

# **Function Block Diagram**

| Absolute Maximum Ratings (Note 1)                                           |                                 |

|-----------------------------------------------------------------------------|---------------------------------|

| • VCC, PVCC, PVCC9 to AGND                                                  | 15V                             |

| • BOOTx to PHASEx                                                           |                                 |

| PHASEx to PGNDx                                                             |                                 |

| DC                                                                          | –0.5V to 15V                    |

| <20ns                                                                       | 5V to 25V                       |

| UGATEx to PHASEx                                                            |                                 |

| DC                                                                          | 0.3V to (BOOTx - PHASEx + 0.3V) |

| <20ns                                                                       | 5V to (BOOTx - PHASEx + 5V)     |

| LGATEx to PGNDx                                                             |                                 |

| DC                                                                          | 0.3V to (PVCC9 + 0.3V)          |

| <20ns                                                                       | 5V to (PVCC9 + 5V)              |

| • Input, Output or I/O Voltage                                              | (AGND – 0.3V) to 6V             |

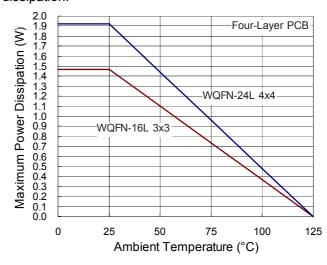

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                                 |

| WQFN-16L 3x3                                                                | 1.471W                          |

| WQFN-24L 4x4                                                                | 1.923W                          |

| Package Thermal Resistance (Note 2)                                         |                                 |

| WQFN-16L 3x3, $\theta_{JA}$                                                 | 68°C/W                          |

| WQFN-16L 3x3, $\theta_{JC}$                                                 |                                 |

| WQFN-24L 4x4, $\theta_{JA}$                                                 | 52°C/W                          |

| WQFN-24L 4x4, $\theta_{JC}$                                                 |                                 |

| Junction Temperature                                                        |                                 |

| Lead Temperature (Soldering, 10 sec.)                                       | 260°C                           |

| Storage Temperature Range                                                   | –65°C to 150°C                  |

| ESD Susceptibility (Note 3)                                                 |                                 |

| HBM (Human Body Mode)                                                       |                                 |

| MM (Machine Mode)                                                           | 200V                            |

|                                                                             |                                 |

| Recommended Operating Conditions (Note 4)                                   |                                 |

| Supply Voltage, V <sub>CC</sub>                                             | 4.5V to 13.2V                   |

| Junction Temperature Range                                                  | 40°C to 125°C                   |

## **Electrical Characteristics**

(V<sub>CC</sub> = 12V, V<sub>PVCC9</sub> = 9V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter                        | Symbol                 | Test Conditions                             | Min  | Тур | Max  | Unit             |

|----------------------------------|------------------------|---------------------------------------------|------|-----|------|------------------|

| Supply Input                     |                        |                                             |      |     |      |                  |

| Bias Voltage                     | V <sub>PVCC</sub>      |                                             | 4.5  |     | 13.2 | V                |

| Regulated Bias Voltage           | V <sub>P</sub> VCC9    |                                             | 8    | 9   | 10   | V                |

| Supply Current                   | I <sub>CC</sub>        | UGATE, LGATE Open                           |      | 6.5 |      | mA               |

| Shutdown Current                 | I <sub>SHDN</sub>      | UGATE, LGATE Open                           |      | 4   |      | mA               |

| Power-On Reset                   | 1                      |                                             | -1   | •   |      | •                |

| VCC POR Threshold                | V <sub>PVCC9R_th</sub> | VCC9 Rising                                 | 3.8  | 4.1 | 4.4  | V                |

| Power On Reset Hysteresis        | V <sub>PVCC9_hys</sub> |                                             |      | 0.3 |      | V                |

| Oscillator                       | 1                      |                                             | 1    | •   | •    |                  |

| Frequency                        | fosc                   | $R_{RT} = 30k\Omega$                        | 175  | 200 | 225  | kHz              |

| Frequency Range                  |                        |                                             | 100  |     | 1000 | kHz              |

| Ramp Amplitude                   | ΔV <sub>OSC</sub>      |                                             |      | 2   |      | V <sub>P-P</sub> |

| Minimum Duty Cycle               |                        |                                             | 0    |     |      | %                |

| Minimum LGATE Pulse              |                        |                                             |      | 300 |      | ns               |

| Reference                        |                        |                                             |      |     | •    |                  |

| Nominal Feedback Voltage         | V <sub>FB</sub>        |                                             | 0.59 | 0.6 | 0.61 | V                |

| Error Amplifier                  |                        |                                             |      |     | •    |                  |

| Open Loop DC Gain                | A <sub>DC</sub>        | Guaranteed by Design                        |      | 70  |      | dB               |

| Gain Bandwidth                   | GBW                    | Guaranteed by Design                        |      | 10  |      | MHz              |

| Slew Rate                        | SR                     | Guaranteed by Design, C <sub>L</sub> = 10pF |      | 6   |      | V/μs             |

| Transconductance                 | gm                     |                                             |      | 1.8 |      | mA/V             |

| Maximum Current (Source & Sink)  | I <sub>COMPsk</sub>    |                                             |      | 360 |      | μΑ               |

| Soft-Start                       |                        |                                             |      |     |      |                  |

| SS Source Current                | I <sub>SS</sub>        | V <sub>SS/EN</sub> = 0V                     | 7    | 10  | 13   | μΑ               |

| Re-Soft-Start Threshold<br>Level |                        |                                             |      | 0.5 |      | V                |

| Current Sense                    |                        |                                             |      |     |      |                  |

| Current Sense Gain               |                        |                                             | 145  | 165 | 185  | μ <b>A</b> /V    |

| Mode Pin Voltage                 | V <sub>MODE</sub>      |                                             |      | 0.6 |      | V                |

| Forced Single Phase<br>Operation | I <sub>MODE</sub>      |                                             | 250  |     |      | μА               |

| Forced Dual Phase<br>Operation   | I <sub>MODE</sub>      |                                             |      |     | 1    | μА               |

| Parameter                                                                                                            | Symbol               | Test Conditions                                                        | Min  | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------|------|-----|------|------|

| PWM Controller Gate Driver                                                                                           |                      |                                                                        | •    |     |      |      |

| Upper Gate Sourcing Ability   I <sub>UGATEsr</sub>   V <sub>BOOTx</sub> - V <sub>PHASEx</sub> = 12<br>Source Current |                      | V <sub>BOOTx</sub> – V <sub>PHASEx</sub> = 12V, Max.<br>Source Current |      | 1.5 |      | Α    |

| Upper Gate R <sub>DS(ON)</sub> Sinking                                                                               | RUGATEsk             | Vugatex - Vphasex = 0.1V                                               |      | 2   |      | Ω    |

| Lower Gate Sourcing Ability                                                                                          | I <sub>LGATEsr</sub> | V <sub>CC</sub> = 12V, Max. Source Current                             |      | 1.5 |      | Α    |

| Lower Gate R <sub>DS(ON)</sub> Sinking                                                                               | R <sub>LGATEsk</sub> | V <sub>LGATEx</sub> = 0.1V                                             |      | 2   |      | Ω    |

| Deadtime                                                                                                             |                      | Vugatex – Vphasex = 1.2V to<br>VLGATEx = 1.2V                          |      | 30  |      | ns   |

| Protection                                                                                                           |                      |                                                                        |      |     |      |      |

| Over Current Threshold                                                                                               | V <sub>IMAX</sub>    |                                                                        | 2.75 | 3   | 3.25 | V    |

| SS Enable Threshold                                                                                                  | V <sub>EN</sub>      |                                                                        | 0.3  | 0.4 | 0.5  | V    |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in natural convection at  $T_A$  = 25°C on a high effective thermal conductivity four-layer test board of JEDEC 51-7 thermal measurement standard. The measurement case position of  $\theta_{JC}$  is on the exposed pad of the packages.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

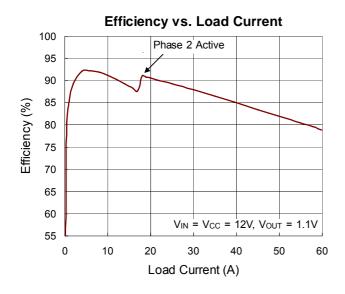

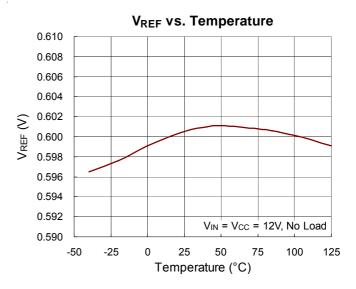

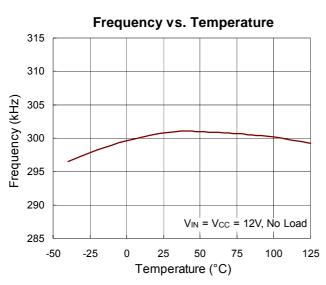

# **Typical Operating Characteristics**

## **Application Information**

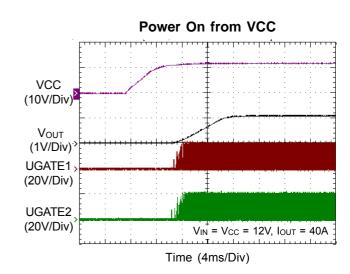

# Dual Supply Voltage (VCC, PVCC) with Internal Regulator

The RT8810 requires an external bias supply for PVCC and VCC. PVCC receives a supply voltage from 4.5V to 13.2V and provides bias current for internal control circuit. VCC is the input pin of the internal 9V LDO which provides current for the PVCC9 pin. PVCC9 is the output pin of the internal 9V LDO regulator. It provides current for lower gate drivers and bootstrap current for upper drivers. Physically place a minimum  $1\mu F$  ceramic capacitor near PVCC and VCC to locally bypass the supply voltage.

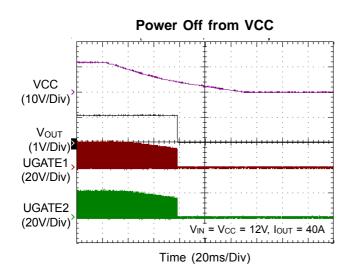

The Power-On-Reset (POR) circuit monitors the supply voltage at the PVCC pin. If PVCC exceeds the POR rising threshold voltage, the controller is reset and prepares the PWM for operation. If PVCC falls below the POR falling threshold during normal operation, all MOSFETs stop switching. The POR rising and falling threshold has a hysteresis to prevent noise caused reset.

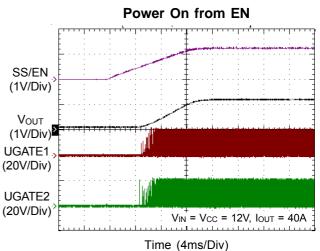

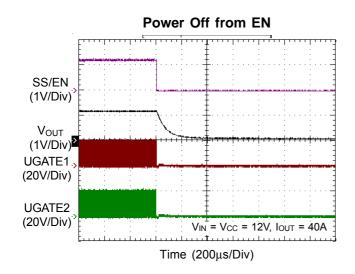

### Soft-Start

The RT8810 provides external soft-start function to prevent large inrush current and output voltage overshoot when the converter starts up. The soft-start begins when OCP programming is complete.

During soft-start, an internal current source ( $10\mu A$ ) is used to charge the external soft-start capacitor at the SS/EN pin.  $V_{SS/EN}$  rises up, and the PWM logic and gate drives become enabled. When the feedback voltage crosses 0.6V, the internal 0.6V reference takes over the behavior of the error operational transconductance amplifier and soft-start is complete. The RT8810 turns off the internal  $10\mu A$  current source when soft-start is complete.

### **Switching Frequency**

High frequency operation optimizes the application by allowing smaller component size, but trades off efficiency due to higher switching losses. Low frequency operation offers the best overall efficiency, but at the expense of component size and board space.

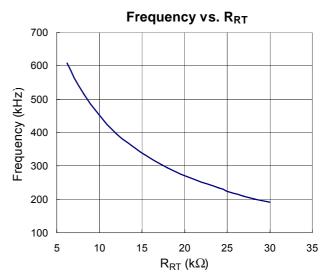

Connect a resistor ( $R_{RT}$ ) between RT and ground to set the switching frequency ( $f_{SW}$ ) per phase. Users can refer to Figure 4 for switching frequency setting.

Figure 4. R<sub>RT</sub> vs. Switching Frequency

A resistor of  $8.6k\Omega$  to  $18k\Omega$  corresponds to a switching frequency of 500kHz to 300kHz, respectively.

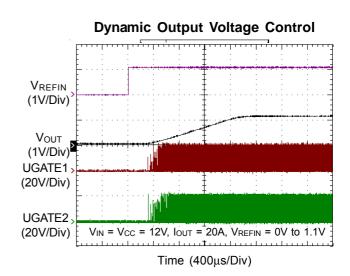

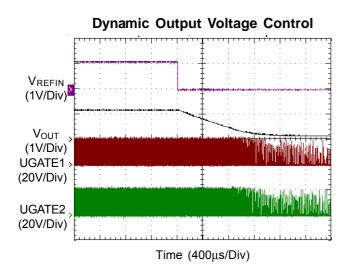

### **External Reference Input**

The RT8810 supports external reference input to provide more flexible applications. The REFIN pin is implemented to be the external reference input. The mode selection is determined and latched after POR. If REFIN pin is floating, a  $10\mu\text{A}$  current source will pull high the REFIN pin and if the pin voltage exceeds 2.8V, the FB pin will follow the internal reference voltage 0.6V. On the other hand, if an external voltage is applied to the REFIN pin, the RT8810 enters tracking mode and regulates FB to be close to this voltage. The applied voltage must be within the tracking range (typically between 0.4V to 2.5V).

If the applied voltage is less than 0.3V, the controller will be shut down.

### **Current Sensing and Reporting**

The RT8810 monitors per phase current for current balance and over current protection. Per phase current is sensed by the on-resistance of low side MOSFET when turned on. The GM amplifier senses the voltage drop across the lower switch and converts it into a current signal each time it turns on. The sensed current is expressed as:

$$I_{CS} = 3.3 \times I_{L} \times R_{DS(ON)} \times 10^{-4} + 5.5 \mu A$$

where I<sub>L</sub> is the per phase current in Ampere,  $R_{DS(ON)}$  is the on-resistance of low side MOSFET in  $m\Omega$ , and 5.5 $\mu$ A is a constant to compensate the offset of the current sensing circuit. Note that the valley inductor current is sampled and held. The sampled and hold current is the averaged inductor current minus half of inductor ripple current :

$$I_{L\_SH} = I_{L\_AVG} - \left(\frac{1}{2} \times \Delta I_L\right)$$

where  $\Delta I_L$  is the inductor ripple current

One half of the summation of the sampled and hold current signal ( $I_{CS1} + I_{CS2}$ ) / 2 is injected to the IMAX pin, that results in a voltage  $V_{IMAX}$  across the resistor  $R_{IMAX}$  connecting IMAX and AGND for over current protection. And  $V_{IMAX}$  is equal to

$$V_{IMAX} = \frac{I_{CS1} + I_{CS2}}{2} \times R_{IMAX}$$

$$= \left[ \frac{3.3 \times (I_{L1\_SH} + I_{L2\_SH}) \times R_{DS(ON)} \times 10^{-4} + 11 \mu A}{2} \right]$$

Therefore, IMAX pin could be used for current reporting.

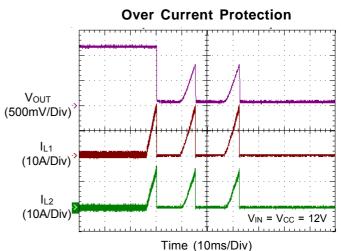

### **Over Current Protection**

The RT8810 features over current protection. The voltage at the IMAX pin ( $V_{IMAX}$ ) is compared with a 3.0V reference voltage. If  $V_{IMAX}$  is higher than 3.0V, OCP is triggered. The over current setting resistor ( $R_{IMAX}$ ) value for dual phase threshold can be calculated according to

$$R_{IMAX} = \frac{3V}{1.65 \times (I_{O\_MAX} - \Delta I_L) \times R_{DS(ON)} \times 10^{-4} + 5.5 \mu A}$$

And the  $R_{\text{IMAX}}$  value for single phase threshold will be

$R_{IMAX}$

$$= \frac{3V}{1.5 x \left[ 1.65 x \left( I_{O\_MAX} - \Delta I_{L} \right) x R_{DS(ON)} x 10^{-4} + 2.75 \mu A \right]}$$

The RT8810 features hiccup and shutdown mode OCP. If OCP is triggered after soft-start ends, the RT8810 turns off both upper and lower MOSFETs and discharges  $C_{\rm SS}$  with a constant current of  $10\mu A$ . When  $V_{\rm SS}$  exceeds 0.5V, the RT8810 initiates another soft-start cycle. The RT8810 shuts down after 3 hiccups. If the OCP is triggered during soft-start cycle, the RT8810 turns off both upper and lower

MOSFETs but continues to charge  $C_{SS}$  with a constant current of  $10\mu A$  until soft-start ends. The shutdown status can only be reset by the POR function.

### **Current Balance**

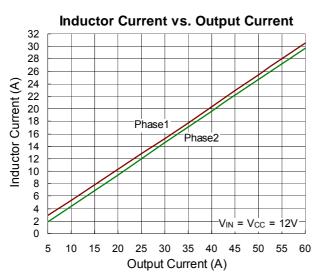

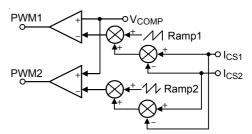

The RT8810 senses each phase current from low side MOSFET  $R_{DS(ON)}$ , and fine tunes the duty cycle of each phase for current balance as shown in Figure 5. If the current of PHASE1 is smaller than the current of PHASE2, the RT8810 increases the duty cycle of the corresponding phase to increase its phase current accordingly.

Figure 5. Current Balance Control Circuit

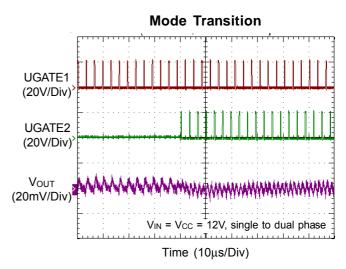

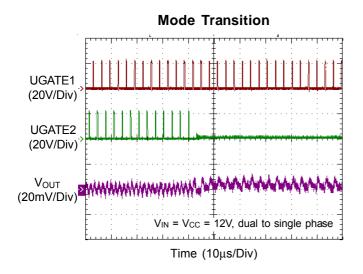

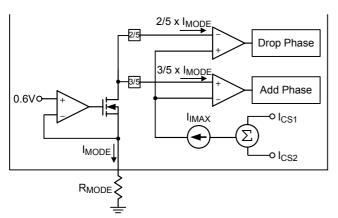

### **Dynamic Phase Number Control**

The RT8810 adaptively controls the operation phase number according to the load current. Figure 6 shows the dynamic phase number control circuit. The phase adding and dropping threshold can be set by a resistor,  $R_{\text{MODE}}$ , which is connected from the MODE pin to AGND. A current,  $I_{\text{MODE}}$ , flows through the resistor,  $R_{\text{MODE}}$ , as

$$I_{MODE} = \frac{0.6}{R_{MODE}}$$

$I_{OUT\ 2P} = 21.2A$

Once  $I_{IMAX}$  is higher than 3 / 5 of  $I_{MODE}$ , the controller will transit to 2-phase operation. When  $I_{IMAX}$  is lower than 2 / 5 of  $I_{MODE}$ , the active phase number will return to one phase.

For example, if  $R_{MODE}$  = 30k $\Omega$ ,  $R_{DS(ON)}$  = 3m $\Omega$ , $\Delta I_L$  = 5A. The load current threshold for adding phase can be calculated as

$$\frac{3 \times I_{MODE}}{5} = \left[ \frac{3.3 \times 10^{-4} \times (I_{OUT\_2P} - 2.5) A \times 3m\Omega + 5.5\mu A}{2} \right]$$

And the load current threshold for dropping phase can be calculated as

www.richtek.com DS8810-01 June 2011

$$\frac{2 \times I_{MODE}}{5}$$

=  $\left[ \frac{3.3 \times 10^{-4} \times (I_{OUT\_2P} - 5) A \times 3m\Omega + 11\mu A}{2} \right]$

$I_{OUT\_2P} = 10A$

Figure 6. Dynamic Phase Number Control Circuit

### **Manual Phase Number Control**

The RT8810 supports manual selecting of single phase or dual phase operation. If  $I_{MODE}$  is higher than 150 $\mu A$ , the RT8810 operates in forced single phase mode. If  $I_{MODE}$  is smaller than  $4\mu A$ , the RT8810 operates in forced dual phase mode.

Note that, the MODE pin is not available for the RT8810C. It supports only two phase operation.

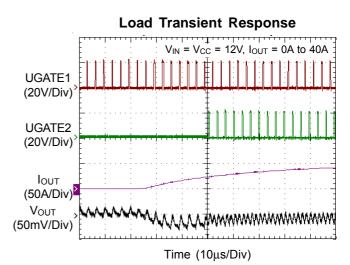

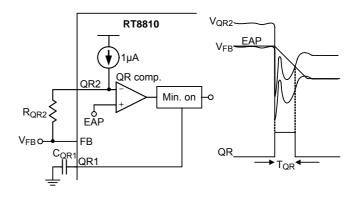

### **Load Transient Quick Response**

The RT8810 utilizes a new quick response feature to supply heavy load current demand during instantaneous load application transient. The RT8810 detects load transient and reacts via  $V_{OUT}$  pin. When  $V_{OUT}$  drops during load application transient, the quick response comparator will send asserted signals to turn on high side MOSFETs and turn off low side MOSFETs. The QR signal will turn on all phase' high side MOSFETs while turning off low side MOSFETs. Therefore, the influence of total quick response function of the RT8810 is adjustable. The quick response threshold can be set by  $R_{QR2}$ . QR is triggered if  $V_{EAP} > 1 \mu A \times R_{QR2} + V_{FB}$ . The QR width can be set according to:

$$T_{QR} = \frac{C_{QR1} \times 0.8V}{300\mu A}$$

Figure 7. Quick Response Active

### **Feedback and Compensation**

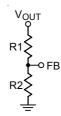

The RT8810 allows the output voltage of the DC/DC converter to be adjusted from 0.6V to 85% of  $V_{IN}$  supply via an external resistor divider. It will try to maintain the feedback pin at internal reference voltage (0.6V).

According to the resistor divider network above, the output voltage is set as :

$$R_2 = R_1 x \left( \frac{V_{REF}}{V_{OUT} - V_{REF}} \right)$$

The RT8810 is a voltage mode controller and requires external compensation to have an accurate output voltage regulation with fast transient response.

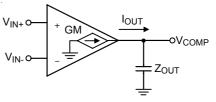

The RT8810 uses a high gain Operational Transconductance Amplifier (OTA) as the error amplifier. As Figure 8 shows, the OTA works as the voltage controlled current source. The characteristic of OTA is as below:

$$gm = \frac{\Delta I_{OUT}}{\Delta V_{M}}$$

where  $\Delta V_{M} = (V_{IN+}) - (V_{IN-})$  and  $\Delta V_{COMP} = \Delta I_{OUT} \times Z_{OUT}$

Figure 8. Operational Transconductance Amplifier, OTA

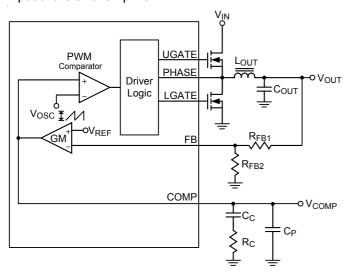

Figure 9 shows a typical buck control loop using Type II compensator. The control loop consists of the power stage, PWM comparator and a compensator. The PWM comparator compares  $V_{COMP}$  with oscillator (OSC) sawtooth wave to provide a Pulse-Width Modulated (PWM) with an amplitude of  $V_{IN}$  at the PHASE node. The PWM wave is smoothen by the output filter  $L_{OUT}$  and  $C_{OUT}$ . The output voltage ( $V_{OUT}$ ) is sensed and fed to the inverting input of the error amplifier.

Figure 9. Typical Voltage Mode Buck Converter Control Loop

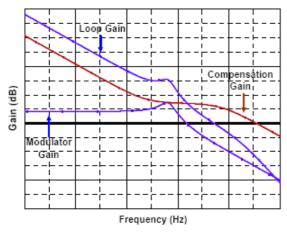

The modulator transfer function is the small signal transfer function of  $V_{\text{OUT}}$  /  $V_{\text{COMP}}$  (output voltage over the error amplifier output). This transfer function is dominated by a DC gain, a double pole, and an ESR zero as shown in Figure 10.

Figure 10. Typical Bode plot of a Voltage Mode Buck Converter

The DC gain of the modulator is the input voltage  $(V_{IN})$  divided by the peak-to-peak oscillator voltage  $V_{OSC}$ .

$$Gain_{modulator} = \frac{V_{IN}}{\Delta V_{OSC}}$$

The output LC filter introduces a double pole, 40dB/decade gain slope above its corner resonant frequency, and a total phase lag of 180 degrees. The resonant frequency of the LC filter is expressed as :

$$f_{LC} = \frac{V_{IN}}{2\pi\sqrt{L_{OUT} \times C_{OUT}}}$$

The ESR zero is contributed by the ESR associated with the output capacitance. Note that this requires the output capacitor to have enough ESR to satisfy stability requirements. The ESR zero of the output capacitor is expressed as follows:

$$f_{ESR} = \frac{1}{2\pi \times C_{OUT} \times ESR}$$

The goal of the compensation network is to provide adequate phase margin (usually greater than 45 degrees) and the highest bandwidth (0dB crossing frequency). It is also recommended to manipulate loop frequency response so that its gain crosses over 0dB at a slope of –20dB/dec. According to Figure 8, the compensation network frequency is as below:

$$F_{P1} = 0$$

$$F_{P2} = \frac{1}{2\pi \times R_{C} \times \left(\frac{C_{C} \times C_{P}}{C_{C} + C_{P}}\right)}$$

$$F_{Z1} = \frac{1}{2\pi \times R_{C} \times C_{C}}$$

Determining the 0dB crossing frequency ( $F_C$ , control loop bandwidth) is the first step of compensator design. Usually,  $F_C$  is set to 0.1 to 0.3 times the switching frequency. The second step is to calculate the open loop modulator gain and find out the gain loss at  $F_C$ . The third step is to design a compensator gain that can compensate the modulator gain loss at  $F_C$ . The final step is to design  $F_{Z1}$  and  $F_{Z2}$  to allow the loop sufficient phase margin.

$F_{Z1}$  is designed to cancel one of the double poles of modulator. Usually,  $F_{Z1}$  is placed before  $f_{LC}$ .  $F_{P2}$  is usually placed below the switching frequency (typically, 0.5 to 1.0 times switching frequency) to eliminate high frequency noise.

www.richtek.com DS8810-01 June 2011

### **Inductor Selection**

The inductor plays an important role in the buck converter because energy from the input power rail is stored in it and then released to the load. From the viewpoint of efficiency, the inductor's DC Resistance (DCR) should be as small as possible since the inductor constantly carries current. In addition, the inductor takes up most of the board space, so its size is also important. Low profile inductors can save board space, especially when there is a height limitation.

Additionally, larger inductance results in lower ripple current, and therefore lower power loss. However, the inductor current rising time increases with inductance value. This means the inductor will have a longer charging time before its current reaches the required output current. Since the response time is increased, the transient response performance will be decreased. Therefore, the inductor design is a trade-off between performance, size and cost.

In general, inductance is designed such that the ripple current ranges between 20% to 30% of full load current. The inductance can be calculated using the following equation.

$$L_{(MIN)} = \frac{V_{IN} - V_{OUT}}{f_{SW} x k x I_{OUT(MAX)}} x \frac{V_{OUT}}{V_{IN}}$$

where k is 0.2 to 0.3.

### **Output Capacitor Selection**

Output capacitors are used to maintain high performance for the output beyond the bandwidth of the converter itself. Two different settings of output capacitors can be found, bulk capacitors closely located to the inductors and ceramic output capacitors in close proximity to the load. Latter ones are for mid frequency decoupling with especially small ESR and ESL values, while the bulk capacitors have to provide enough stored energy to overcome the low frequency bandwidth gap between the regulator and the GPU.

### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC

package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications of the RT8810, the maximum junction temperature is 125°C and  $T_A$  is the ambient temperature. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WQFN-16L 3x3 packages, the thermal resistance,  $\theta_{JA}$ , is 68°C/W on a standard JEDEC 51-7 four-layer thermal test board. For WQFN-24L 4x4 packages, the thermal resistance,  $\theta_{JA}$ , is 52°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated by the following formula :

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (68^{\circ}C/W) = 1.471W$$

for

WQFN-16L 3x3 package

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (52^{\circ}C/W) = 1.923W$$

for

WQFN-24L 4x4 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . For the RT8810 package, the derating curves in Figure 11 allow the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 11. Derating Curves for the RT8810 Packages

### **Layout Considerations**

Careful PC board layout is critical to achieve low switching losses and clean, stable operation. The switching power stage requires particular attention. If possible, mount all of the power components on the top side of the board with their ground terminals flush against one another. Follow these guidelines for optimum PC board layout:

- Power components should be placed first. Place the input capacitors close to the power MOSFETs, then locate the filter inductors and output capacitors between the power MOSFETs and the load.

- Place both the ceramic and bulk input capacitor close to the drain pin of the high side MOSFET. This can reduce the impedance presented by the input bulk capacitance at high switching frequency. If there is more than one high side MOSFET in parallel, each should have its own individual ceramic capacitor.

- Keep the power loops as short as possible. For low voltage high current applications, power components are the most critical part in the layout because they switch a large amount of current. The current transition from one device to another at high speed causes voltage spikes due to the parasitic components on the circuit board. Therefore, all of the high current switching loops should be kept as short as possible with large and thick copper traces to minimize the radiation of electromagnetic interference.

- Minimize the trace length between the power MOSFETs and its drivers. Since the drivers use short, high current pulses to drive the power MOSFETs, the driving traces should be sized as short and wide as possible to reduce the trace inductance. This is especially true for the low side MOSFET, since this can reduce the possibility of shoot through.

- Provide enough copper area around the power MOSFETs and the inductors to aid in heat sinking. Use thick copper PCB to reduce the resistance and inductance for improved efficiency.

- The bank of output capacitor should be placed physically close to the load. This can minimize the impedance seen by the load, and then improve the transient response.

- Place all of the high frequency decoupling ceramic capacitors close to their decoupling targets.

- ▶ Small signal components should be located as close to the IC as possible. The small signal components include the feedback components, current sensing components, the compensation components, function setting components and any bypass capacitors. These components belong to the high impedance circuit loop and are inherently sensitive to noise pick-up. Therefore, they must be located close to their respective controller pins and away from the noisy switching nodes.

- A multi layer PCB design is recommended. Make use of one single layer as the power ground and have a separate control signal ground as the reference of all signals.

www.richtek.com DS8810-01 June 2011

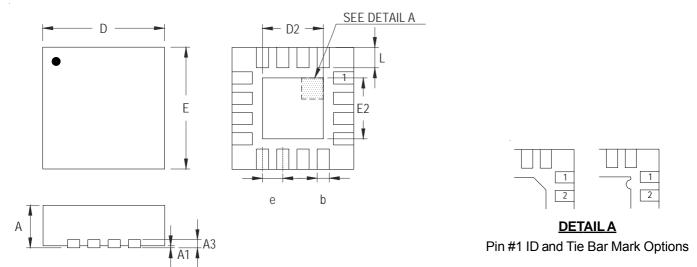

# **Outline Dimension**

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Cumbal | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

| Symbol | Min        | Max            | Min                  | Max   |  |

| А      | 0.700      | 0.800          | 0.028                | 0.031 |  |

| A1     | 0.000      | 0.050          | 0.000                | 0.002 |  |

| A3     | 0.175      | 0.250          | 0.007                | 0.010 |  |

| b      | 0.180      | 0.300          | 0.007                | 0.012 |  |

| D      | 2.950      | 3.050          | 0.116                | 0.120 |  |

| D2     | 1.300      | 1.750          | 0.051                | 0.069 |  |

| Е      | 2.950      | 3.050          | 0.116                | 0.120 |  |

| E2     | 1.300      | 1.750          | 0.051                | 0.069 |  |

| е      | 0.500      |                | 0.0                  | )20   |  |

| L      | 0.350      | 0.450          | 0.014                | 0.018 |  |

W-Type 16L QFN 3x3 Package

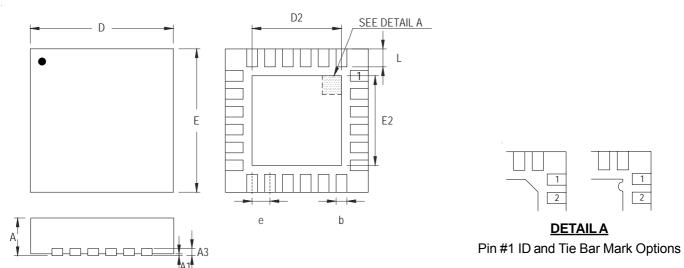

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Oh a l | Dimensions I | In Millimeters | Dimensions In Inches |       |  |

|--------|--------------|----------------|----------------------|-------|--|

| Symbol | Min          | Max            | Min                  | Max   |  |

| А      | 0.700        | 0.800          | 0.028                | 0.031 |  |

| A1     | 0.000        | 0.050          | 0.000                | 0.002 |  |

| A3     | 0.175        | 0.250          | 0.007                | 0.010 |  |

| b      | 0.180        | 0.300          | 0.007                | 0.012 |  |

| D      | 3.950        | 4.050          | 0.156                | 0.159 |  |

| D2     | 2.300        | 2.750          | 0.091                | 0.108 |  |

| Е      | 3.950        | 4.050          | 0.156                | 0.159 |  |

| E2     | 2.300        | 2.750          | 0.091                | 0.108 |  |

| е      | 0.500        |                | 0.0                  | )20   |  |

| L      | 0.350        | 0.450          | 0.014                | 0.018 |  |

W-Type 24L QFN 4x4 Package

### **Richtek Technology Corporation**

Headquarter

5F, No. 20, Taiyuen Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789 Fax: (8863)5526611

### **Richtek Technology Corporation**

Taipei Office (Marketing)

5F, No. 95, Minchiuan Road, Hsintien City

Taipei County, Taiwan, R.O.C.

Tel: (8862)86672399 Fax: (8862)86672377

Email: marketing@richtek.com

Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Richtek manufacturer:

Other Similar products are found below:

5962-8670403PA A4450KESTR-J A6727TR AAC243E-S8A-G-LF-TR ADP1055ACPZ-R7 ADP1621ARMZ-R7 ADP1850ACPZ-R7

ADP1864AUJZ-R7 ADP3211AMNR2G ADP3211MNR2G AIC2857FGR8TR AOZ1267QI-01 AOZ1282CI-2 AOZ2261NQI-11 AP1501-12

AP1501-12/TR AP1501-3.3 AP1501-3.3/TR AP1501-5.0 AP1501-ADJ/TR AP1509-12ME/TR AP2008TC-A1 AP2900TB-A1

AP3302K6TR-G1 AP3303S9-13 AP3842CMTR-E1 AP3843CMTR-E1 AP3844CMTR-E1 AP8012HSEC-R1 APR3401W6-7

APW8713AQBI-TRG ASP8120ZC-R AW360994DNR AW36099CSR AZ494AP-E1 AZ7500BP-E1 AZ7500EP-E1 BA9741F-E2

BA9743AFV-E2 BA9744FV-E2 BD63536FJ-E2 BD6525 BD7672BG-GTR BD7673AG-GTR BD7679G-GTR BD87007FJ-E2

BD9018KV-E2 BD9300F-E2 BD9611MUV-E2 BD9615MUV-LBE2