## **AVB Audio Endpoint**

## **Highlights**

Supports the implementation of an Automotive Ethernet Audio Device (AED-A) to transmit and/or receive uncompressed audio over an Ethernet Audio Video Bridging (AVB) network

## **Target Applications**

- · Automotive in-vehicle networking

- Infotainment

- Telematics

#### **Features**

- · generalized Precision Time Protocol (gPTP)

- Grandmaster

- Slave

- Precise time synchronization

- 1PPS measurement support

- · Audio Video Transport Protocol (AVTP)

- AVTP Audio Format (AAF) Listener or Talker

- AVTP Clock Reference Format (CRF) Listener or Talker

- Real-time Transport Protocol (RTP)

- Extended with AVB RTCP support

- Configurable Payload Type Id for fitting to custom RTP profile specifications

- · Stream routing

- Up to 8 streams in parallel

- Processing of up to 40 audio channels

- Parallel processing of incoming and outgoing streams

- PDM to PCM decimation

- · Media Clock recovery, from an:

- AVTP AAF stream

- AVTP CRF stream

- RTP stream

- · Media Clock generation, based on:

- Local crystal

- External FSY signal

- Configuration

- Avnu entity model based

- Tool assisted by MPLAB® Network Creator

- Bootloader

- Remote firmware update over Ethernet

- Remote configuration update over Ethernet

- External MCU connectivity

- MCU connected as Layer 2 device

- Ethernet frame pass through on SPI

- · Secure element (optional)

- High-bandwidth Digital Content Protection (HDCP) receiver

- Secure boot

- Secure update

- Ethernet MAC 10/100 Mbps in Reduced Media Independent Interface (RMII) mode

- Two I<sup>2</sup>C Ports

- PLL, TA100 and EEPROM control

- User-specific external modules

- · Serial Peripheral Interface (SPI) Port

- · Two Audio Interfaces supporting:

- Inter-IC Sound (I<sup>2</sup>S)

- Time-Division Multiplexing (TDM)

- Pulse-Density Modulation (PDM)

- · System

- Embedded voltage regulator for single-supply operation

- Power-on-Reset (POR), Brown-out Detector (BOD)

- AEC-Q100 Grade 2 qualified

- Package

- 100-ball TFBGA, 9x9 mm, pitch 0.8 mm

## Conformity

- Automotive Ethernet AVB Functional and Interoperability Specification

- IEEE 1722™-2016 (AVTP)

- RFC 3550-2003 (RTP/RTP Control Protocol (RTCP))

- IEEE 1733™-2011 (AVB RTCP packet extension)

- IEEE 802.1AS™-2011 (gPTP)

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

## http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 1.0 INTRODUCTION

The LAN9360 supports the implementation of an Automotive Ethernet Audio Device enabling uncompressed audio data transfers over an Ethernet Audio Video Bridging network. Hence, it is designed to route audio data between an AVB/TSN Media Stream on the Ethernet network and an Audio Interface that connects to digital audio sources and sinks.

The LAN9360 provides an implementation of an AVB/TSN protocol stack. By connection to an external Ethernet PHY Transceiver, it can be used with several Ethernet physical layers.

Figure 1-1 depicts the block diagram of the LAN9360.

FIGURE 1-1: LAN9360 BLOCK DIAGRAM

As outlined in Figure 1-1, the LAN9360 consists of functional blocks. Each functional block contains one or multiple components that provide specific functionality.

## 1.1 LAN9360 Functional Blocks

The LAN9360 functional blocks are described in the LAN9360 data sheet.

Functional blocks, which interfere with external devices via physical pins are called interfaces.

## 1.2 External Devices

## **Ethernet PHY Transceiver**

100BASE-T1 or 100BASE-TX may be selected by configuration. 10BASE-T1S is supported for evaluation.

#### **PLL**

The LAN9360 requires an external PLL of type CS2100 to generate the Bit-Clock for the Audio Interface.

## **Audio Device**

An external audio device, e.g., a DSP or a CODEC, is connected to the Audio Interface to transfer digital audio data. It is used as sink and/or source of Pulse-Code Modulation/Pulse-Density Modulation (PCM/PDM) coded audio data.

## **Secure Element (Optional)**

A TA100 is used for HDCP, secure boot and secure update.

## **EEPROM (Optional)**

The I<sup>2</sup>C Serial EEPROM is used to read a pre-programmed globally unique EUI-48 node identity for MAC address configuration. The LAN9360 can operate with EEPROMs that are compatible to the storage format as used with Microchip's 24AA025E48.

## MCU (Optional)

An external MCU may be connected to the SPI to send and receive Ethernet frames.

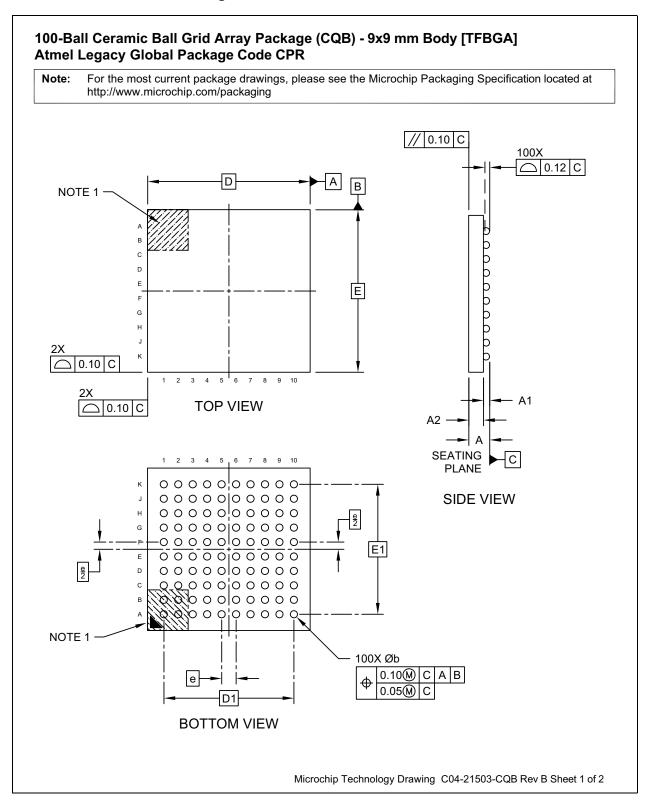

## 2.0 PACKAGE AND PINOUT

## 2.1 100-Ball TFBGA Package Outline

## 100-Ball Ceramic Ball Grid Array Package (CQB) - 9x9 mm Body [TFBGA] **Atmel Legacy Global Package Code CPR**

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                       | MILLIMETERS |          |          |      |

|-----------------------|-------------|----------|----------|------|

| Dimension             | Limits      | MIN      | NOM      | MAX  |

| Number of Terminals   | N           | 100      |          |      |

| Pitch                 | е           |          | 0.80 BSC |      |

| Overall Height        | Α           | 1.10     | -        | 1.20 |

| Ball Height           | A1          | 0.20     | -        | -    |

| Molded Package Height | A2          | 0.65     | -        | -    |

| Overall Length        | D           |          | 9.00 BSC |      |

| Overall Pitch         | D1          |          | 7.20 BSC |      |

| Overall Width         | Е           |          | 9.00 BSC |      |

| Overall Pitch         | E1          | 7.20 BSC |          |      |

| Terminal Diameter     | b           | 0.40     | 0.45     | 0.50 |

## Notes:

- 1. Terminal A1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-21503-CQB Rev B Sheet 2 of 2

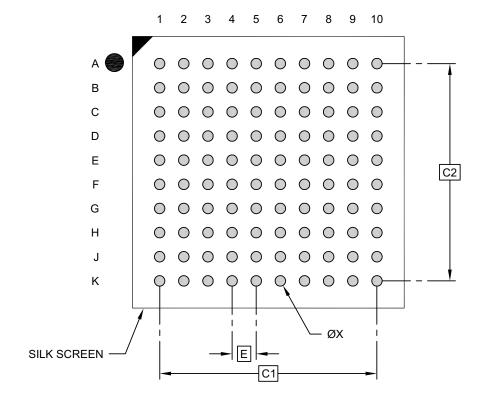

# 100-Ball Ceramic Ball Grid Array Package (CQB) - 9x9 mm Body [TFBGA] Atmel Legacy Global Package Code CPR

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                             | Units  | N   | IILLIMETER: | S    |

|-----------------------------|--------|-----|-------------|------|

| Dimension                   | Limits | MIN | NOM         | MAX  |

| Contact Pitch               | Е      |     | 0.80 BSC    |      |

| Overall Pitch               | C1     |     | 7.20 BSC    |      |

| Contact Pad Spacing         | C2     |     | 7.20 BSC    |      |

| Contact Pad Diameter (X100) | X1     |     |             | 0.35 |

#### Notes:

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-23503-CQB Rev B

## 2.2 100-Lead Package Pinout

| TFBGA<br>Ball | Signal            | Conditions/<br>I/O Type | Pin Description                 | Туре                            | Note                                                                                          |

|---------------|-------------------|-------------------------|---------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------|

| Audio Int     | erface            |                         |                                 |                                 |                                                                                               |

| E2            | SCKA              | GPIO                    | Serial Clock                    | Input/Output                    | _                                                                                             |

| E1            | FSYA              |                         | Word Select                     | Input/Output                    | 1                                                                                             |

| K9            | SRA               | GPIO_AD                 | Serial Data Input               | Input                           | 1                                                                                             |

| G3            | SXA               | GPIO                    | Serial Data Output              | Output                          | 7                                                                                             |

| C10           | SCKB              | GPIO_AD                 | Serial Clock                    | Input/Output                    | _                                                                                             |

| J6            | FSYB              |                         | Word Select                     | Input/Output                    |                                                                                               |

| J5            | SRB               |                         | Serial Data Input               | Input                           |                                                                                               |

| C7            | SXB               | GPIO                    | Serial Data Output              | Output                          |                                                                                               |

| B1            | CLKEN             | GPIO_AD                 | Bit-Clock and Word-Clock enable |                                 | Assigned, when PLL clock output is stable                                                     |

| Serial Pe     | ripheral Interfac | ce                      |                                 |                                 |                                                                                               |

| H1            | PCS               | GPIO                    | Peripheral Chip Select          | Master: Output,<br>Slave: Input | _                                                                                             |

| K3            | MISO              |                         | Master In Slave Out             | Master: Input,<br>Slave: Output |                                                                                               |

| H5            | MOSI              | GPIO_AD                 | Master Out Slave In             | Master: Output,<br>Slave: Input |                                                                                               |

| J4            | SPCK              |                         | Serial Clock                    | Master: Output,<br>Slave: Input |                                                                                               |

| G1            | IRQ               |                         | Interrupt Request               | Output                          |                                                                                               |

| K1            | FC                |                         | Flow Control                    |                                 |                                                                                               |

| Clock Int     | erface            |                         |                                 |                                 |                                                                                               |

| F8            | REFCLK0           | GPIO                    | Reference Clock 0               | Output                          | Reference clock output to be connected to REFCLKIN. Used for internal clock management        |

|               | ERASE             |                         | _                               | Input                           | _                                                                                             |

| K8            | REFCLK1           |                         | Reference Clock 1               | Output                          | Signal is used to drive<br>the clock reference of<br>the external PLL for<br>the audio clock. |

|               |                   |                         | 1PPS Measurement Signal         |                                 | 1PPS method for clock accuracy measurement                                                    |

| G2            | MCLK              | GPIO_AD                 | Master Clock                    |                                 | _                                                                                             |

| J1            | PLLDIVSEL         |                         | PLL Divider Select              |                                 |                                                                                               |

| J3            | PLLIN             |                         | Reference Clock Input           | Input                           |                                                                                               |

| A9            | EVIN              | GPIO                    | Event Input for Timestamping    |                                 |                                                                                               |

| H7            | UNLOCK            | GPIO_AD                 | Media Clock Unlock              | Output                          | Signals media clock synchronization failures                                                  |

| H8            | REFCLKIN          |                         | Reference Clock Input           | Input                           | _                                                                                             |

| TFBGA<br>Ball            | Signal        | Conditions/<br>I/O Type | Pin Description                | Туре         | Note                                                                  |

|--------------------------|---------------|-------------------------|--------------------------------|--------------|-----------------------------------------------------------------------|

| Crystal 1                | 2 MHz         |                         |                                |              |                                                                       |

| A2                       | XOUT          | CLOCK                   | _                              | Output       | _                                                                     |

| A1                       | XIN           |                         |                                | Input        |                                                                       |

| AVB LAN                  | Interface     |                         |                                |              |                                                                       |

| C1                       | GTXCK         | GPIO_AD                 | Transmit Clock                 | Input        | Input only. GTXCK must be provided with a 50 MHz external oscillator. |

| D2                       | GTXEN         | GPIO                    | Transmit Enable                | Output       | _                                                                     |

| E3                       | GTX0          |                         | Transmit Data                  | Output       |                                                                       |

| B5                       | GTX1          |                         |                                |              |                                                                       |

| A5                       | GRXDV         | GPIO_CLK                | Receive Data Valid             | Input        |                                                                       |

| D5                       | GRX0          |                         | Receive Data                   | Input        |                                                                       |

| B6                       | GRX1          |                         |                                |              |                                                                       |

| A6                       | GRXER         |                         | Receive Error                  | Input        |                                                                       |

| B7                       | GMDC          |                         | Management Data Clock          | Output       |                                                                       |

| B8                       | GMDIO         |                         | Management Data Input/Output   | Input/Output |                                                                       |

| F1                       | GINT          | GPIO_AD                 | LAN interrupt                  | Input        | From LAN PHY                                                          |

| J8                       | GRST          |                         | LAN reset                      | Output       | To LAN PHY                                                            |

| I <sup>2</sup> C Interfa | ace           |                         |                                |              |                                                                       |

| H4                       | SDA0          | GPIO_AD                 | Serial Data                    | Input/Output | Interface to host                                                     |

| J7                       | SCK0          |                         | Serial Clock                   | Output       |                                                                       |

| F9                       | SDA1          | GPIO_AD                 | Serial Data                    | Input/Output | Interface to connect a                                                |

| H10                      | SCK1          | GPIO                    | Serial Clock                   | Output       | PLL and an optional Secure Element                                    |

| H6                       | TA100RST      | GPIO_CLK                | TA100 reset                    |              | _                                                                     |

| Debug In                 | terface       |                         |                                |              |                                                                       |

| C8                       | SWO           | GPIO                    | Serial Wire Output             | Output       | _                                                                     |

| G8                       | SWDIO         |                         | Serial Wire Debug Input/Output | Input        |                                                                       |

| E9                       | SWCLK         | GPIO                    | Serial Wire Debug Clock        | Input        |                                                                       |

| Miscellar                | Miscellaneous |                         |                                |              |                                                                       |

| G10                      | RST           | RST                     | _                              | Input        | _                                                                     |

| TFBGA<br>Ball                           | Signal           | Conditions/<br>I/O Type | Pin Description | Туре | Note |

|-----------------------------------------|------------------|-------------------------|-----------------|------|------|

| Power ar                                | Power and Ground |                         |                 |      |      |

| C5, F3,<br>G7                           | VDDIO            | POWER                   | Power           | _    | _    |

| C6, D6,<br>G6                           | VDDCORE          |                         |                 |      |      |

| D7                                      | VDDPLL           |                         |                 |      |      |

| E5                                      | VDDUTMII         |                         |                 |      |      |

| В3                                      | VDDUTMIC         |                         |                 |      |      |

| E6                                      | VDDPLLUSB        |                         |                 |      |      |

| C3                                      | VDDOUT           |                         |                 |      |      |

| C2                                      | VDDIN            |                         |                 |      |      |

| D1                                      | VREFP            | =                       |                 |      |      |

| D3                                      | VREFN            | GROUND                  |                 |      |      |

| A8, C4,<br>D4, E4,<br>E7, F4,<br>F5, F6 | GND              |                         | Ground          |      |      |

| Not Conr                                | nected           |                         |                 |      |      |

| A3, A4,<br>A7, A10                      | Not connected    | _                       | _               | _    | _    |

| B2, B4,<br>B9, B10                      |                  |                         |                 |      |      |

| C9                                      |                  |                         |                 |      |      |

| D8, D9,<br>D10                          |                  |                         |                 |      |      |

| E8, E10                                 |                  |                         |                 |      |      |

| F2, F7,<br>F10                          |                  |                         |                 |      |      |

| G4, G5,<br>G9                           |                  |                         |                 |      |      |

| H2, H3,<br>H9                           |                  |                         |                 |      |      |

| J2, J9,<br>J10                          |                  |                         |                 |      |      |

| K2, K4,<br>K5, K6,<br>K7, K10           |                  |                         |                 |      |      |

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO. X  Device Device Family Variant | - <u>X</u><br>Opera<br>Temper<br>Ran | ature Type Reel Option Code Code                                                      |

|------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------|

| Device Family:                           | LAN936                               | 50                                                                                    |

| Device Variant:                          | Α                                    | = Basis feature set                                                                   |

| Operating Temperature Range:             | V                                    | = -40°C to +105°C (AEC-Q100 Grade 2)<br>= -40°C to +85°C (Industrial)                 |

| Package Type:                            | CQB                                  | = TFBGA (100-ball)                                                                    |

| Tape and Reel<br>Option:                 | Blank<br>T                           | = Standard packaging (tray)<br>= Tape and Reel <sup>(1)</sup>                         |

| Automotive Code<br>Option:               | Blank<br>VXX                         | = Industrial grade<br>= Automotive grade                                              |

| Revision Code:                           | 100<br>CXX                           | = Standard revision code = Custom revision code, contact Microchip support if needed. |

## Examples:

a) LAN9360A-V/CQBT-VAO-100, Basis feature set, TFBGA (100 ball), -40°C to +105°C, Tape and Reel, Automotive grade Standard revision code 100

b)LAN9360A-I/CQBT-CXX, Basis feature set, TFBGA (100 ball), -40°C to +85°C, Tape and Reel, Industrial grade Custom revision code CXX

Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option. Reel size is 5,000.

## APPENDIX A: REVISION HISTORY

| Revision    | Date      | Comment                                                                        |

|-------------|-----------|--------------------------------------------------------------------------------|

| DS60001577D | Jan. 2021 | Initial release of this document                                               |

| DS60001577C | July 2020 | Updated draft document. For details refer to the respective document revision. |

| DS60001577B | Nov. 2019 |                                                                                |

| DS60001577A | July 2019 | Initial version of draft document                                              |

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- · Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. We at Microchip are

committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection

feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or

other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUEN-TIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet Iogo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2019-2021, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-6716-8

## Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Fax: 317-773-5453 Tel: 317-536-2380 **Los Angeles**

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

**China - Xian** Tel: 86-29-8833-7252

China - Xiamen

Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

**Korea - Daegu** Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4485-5910 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

**Germany - Karlsruhe** Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

**Italy - Padova** Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820