# **User guide for REF-22K-GPD-INV-EASY3B**

## A reference design for a general purpose drive

#### **About this document**

#### **Scope and purpose**

This user guide provides an overview of the reference kit REF-22K-GPD-INV-EASY3B including its main features, key data, pin assignments, mechanical dimensions and corresponding control card. The reference kit REF-22K-GPD-INV-EASY3B is an industrial motor drive for three-phase 400 V AC grids and has a nominal power of 22 kW.

The REF-22K-GPD-INV-EASY3B includes the Easy3B power module FP100R12W3T7\_B11, the current sensor TLIh4971-A120T5, the gate driver IC 1ED3240MC12H, the 1.7 kV SiC-MOSFET IMBF170R1K0M1 and the microcontrollers XMC4800-F144F2048 and XMC4300-F100K256. The combination of these Infineon products allows the customer to evaluate these products in one design and experience the interaction between the products.

Beside the hardware, the REF-22K-GPD-INV-EASY3B offers you software for control and communication. The inverter can be controlled via PC-GUI.

Note:

Please note that this product is not qualified according to the AEC Q100 or AEC Q101 documents of the Automotive Electronics Council.

#### **Intended audience**

This user guide is intended for all technical specialists working on industrial drives and those interested in how the latest Infineon products like IGBT7, XENSIV™ current sensors, EICE™ drivers and CoolSiC™ MOSFETs perform under application conditions.

#### **Reference Kit**

The Infineon products are embedded on this PCB with functions and form factor close to a commercial design. PCB and auxiliary circuits are optimized for the final design.

Note: Boards do not necessarily meet safety, EMI, quality standards (for example UL, CE) requirements.

### **User Guide for REF-22K-GPD-INV-EASY3B**

#### Reference design for motor general purpose drives

### Important notice

"Evaluation Boards and Reference Boards" shall mean products embedded on a printed circuit board (PCB) for demonstration and/or evaluation purposes, which include, without limitation, demonstration, reference and evaluation boards, kits and design (collectively referred to as "Reference Board").

Environmental conditions have been considered in the design of the Evaluation Boards and Reference Boards provided by Infineon Technologies. The design of the Evaluation Boards and Reference Boards has been tested by Infineon Technologies only as described in this document. The design is not qualified in terms of safety requirements, manufacturing and operation over the entire operating temperature range or lifetime.

The Evaluation Boards and Reference Boards provided by Infineon Technologies are subject to functional testing only under typical load conditions. Evaluation Boards and Reference Boards are not subject to the same procedures as regular products regarding returned material analysis (RMA), process change notification (PCN) and product discontinuation (PD).

Evaluation Boards and Reference Boards are not commercialized products, and are solely intended for evaluation and testing purposes. In particular, they shall not be used for reliability testing or production. The Evaluation Boards and Reference Boards may therefore not comply with CE or similar standards (including but not limited to the EMC Directive 2004/EC/108 and the EMC Act) and may not fulfill other requirements of the country in which they are operated by the customer. The customer shall ensure that all Evaluation Boards and Reference Boards will be handled in a way which is compliant with the relevant requirements and standards of the country in which they are operated.

The Evaluation Boards and Reference Boards as well as the information provided in this document are addressed only to qualified and skilled technical staff, for laboratory usage, and shall be used and managed according to the terms and conditions set forth in this document and in other related documentation supplied with the respective Evaluation Board or Reference Board.

It is the responsibility of the customer's technical departments to evaluate the suitability of the Evaluation Boards and Reference Boards for the intended application, and to evaluate the completeness and correctness of the information provided in this document with respect to such application.

The customer is obliged to ensure that the use of the Evaluation Boards and Reference Boards does not cause any harm to persons or third party property.

The Evaluation Boards and Reference Boards and any information in this document is provided "as is" and Infineon Technologies disclaims any warranties, express or implied, including but not limited to warranties of non-infringement of third party rights and implied warranties of fitness for any purpose, or for merchantability.

Infineon Technologies shall not be responsible for any damages resulting from the use of the Evaluation Boards and Reference Boards and/or from any information provided in this document. The customer is obliged to defend, indemnify and hold Infineon Technologies harmless from and against any claims or damages arising out of or resulting from any use thereof.

Infineon Technologies reserves the right to modify this document and/or any information provided herein at any time without further notice.

### User Guide for REF-22K-GPD-INV-EASY3B

### Reference design for motor general purpose drives

### Safety precautions

Note: Please note the following warnings regarding the hazards associated with development systems.

#### Table 1 **Safety precautions**

**Warning:** The DC link potential of this board is up to 1000 VDC. When measuring voltage waveforms by oscilloscope, high voltage differential probes must be used. Failure to do so may result in personal injury or death.

Warning: The evaluation or reference board contains DC bus capacitors which take time to discharge after removal of the main supply. Before working on the drive system, wait five minutes for capacitors to discharge to safe voltage levels. Failure to do so may result in personal injury or death. Darkened display LEDs are not an indication that capacitors have discharged to safe voltage levels.

**Warning:** The evaluation or reference board is connected to the grid input during testing. Hence, high-voltage differential probes must be used when measuring voltage waveforms by oscilloscope. Failure to do so may result in personal injury or death. Darkened display LEDs are not an indication that capacitors have discharged to safe voltage levels.

Warning: Remove or disconnect power from the drive before you disconnect or reconnect wires, or perform maintenance work. Wait five minutes after removing power to discharge the bus capacitors. Do not attempt to service the drive until the bus capacitors have discharged to zero. Failure to do so may result in personal injury or death.

**Caution:** The heat sink and device surfaces of the evaluation or reference board may become hot during testing. Hence, necessary precautions are required while handling the board. Failure to comply may cause injury.

**Caution:** Only personnel familiar with the drive, power electronics and associated machinery should plan, install, commission and subsequently service the system. Failure to comply may result in personal injury and/or equipment damage.

**Caution:** The evaluation or reference board contains parts and assemblies sensitive to electrostatic discharge (ESD). Electrostatic control precautions are required when installing, testing, servicing or repairing the assembly. Component damage may result if ESD control procedures are not followed. If you are not familiar with electrostatic control procedures, refer to the applicable ESD protection handbooks and guidelines.

**Caution:** A drive that is incorrectly applied or installed can lead to component damage or reduction in product lifetime. Wiring or application errors such as undersizing the motor, supplying an incorrect or inadequate AC supply, or excessive ambient temperatures may result in system malfunction.

**Caution:** The evaluation or reference board is shipped with packing materials that need to be removed prior to installation. Failure to remove all packing materials that are unnecessary for system installation may result in overheating or abnormal operating conditions.

## Reference design for motor general purpose drives

## **Table of contents**

Table of contents

| About    | t this documentt                               | 1  |

|----------|------------------------------------------------|----|

| Impo     | rtant notice                                   | 2  |

| Safet    | ty precautions                                 | 3  |

| Table    | e of contents                                  | 4  |

| 1        | The reference board at a glance                | 6  |

| -<br>1.1 | Delivery content                               |    |

| 1.2      | Block diagram                                  |    |

| 1.3      | Main features                                  |    |

| 1.4      | Board parameters and technical data            |    |

| 1.4.1    | Overload profile normal duty                   | 9  |

| 1.4.2    | Heavy duty overload profile                    | 9  |

| 1.5      | Advantages of two level slew rate gate drivers | 10 |

| 2        | System design                                  | 11 |

| 2.1      | Schematics                                     |    |

| 2.2      | Layout                                         | 11 |

| 2.2.1    | Power board                                    | 11 |

| 2.3      | Inverter cooling concept                       | 13 |

| 2.4      | Bill of material                               | 14 |

| 2.5      | Connector details                              | 14 |

| 3        | Software structure                             | 17 |

| 3.1      | Overview                                       | 17 |

| 3.2      | R-CPU Software                                 | 17 |

| 3.2.1    | Real-time Domain                               | 18 |

| 3.2.1.   | 1 Auto-generated Code                          | 19 |

| 3.2.1.2  | 2 Control-Framework                            | 19 |

| 3.2.1.3  | 3 Measurement and Conditioning                 | 20 |

| 3.2.1.4  | 4 Protection                                   | 21 |

| 3.2.1.5  | 5 Background Domain                            | 22 |

| 3.2.1.6  | 6 Tasks                                        | 23 |

| 3.2.1.   | 7 Main State Machine                           | 23 |

| 3.2.1.8  |                                                |    |

| 3.2.1.9  | · ·                                            |    |

| 3.2.2    | Hardware Abstraction (DAVE)                    |    |

| 3.2.3    | Signals and Parameters                         |    |

| 3.2.4    | Folder and file reference                      |    |

| 3.3      | Inter-Processor Communication                  |    |

| 3.3.1    | Packet Structure and Code Layers               |    |

| 3.3.2    | State Machine                                  |    |

| 3.3.3    | Command Reference                              |    |

| 3.4      | C-CPU Software                                 |    |

| 3.4.1    | Structure                                      |    |

| 3.4.2    | Parameter Database                             |    |

| 3.4.3    | Folder and file reference                      |    |

|          | System and functional description              |    |

| 4.1      | Usage                                          |    |

| 4.1.1    | Prerequisites and Installation                 | 40 |

### **Table of contents**

| 4.1.2    | Installing the GPD software package                      | 40  |

|----------|----------------------------------------------------------|-----|

| 4.1.3    | Installing PLECS                                         |     |

| 4.1.4    | Installing the J-Link drivers for flashing               | 40  |

| 4.1.5    | Installing DAVE                                          | 41  |

| 4.1.5.   | 1 Installation                                           | 41  |

| 4.1.5.   | 2 Compiling the R-CPU software package                   | 41  |

| 4.1.5.   | 1 0                                                      |     |

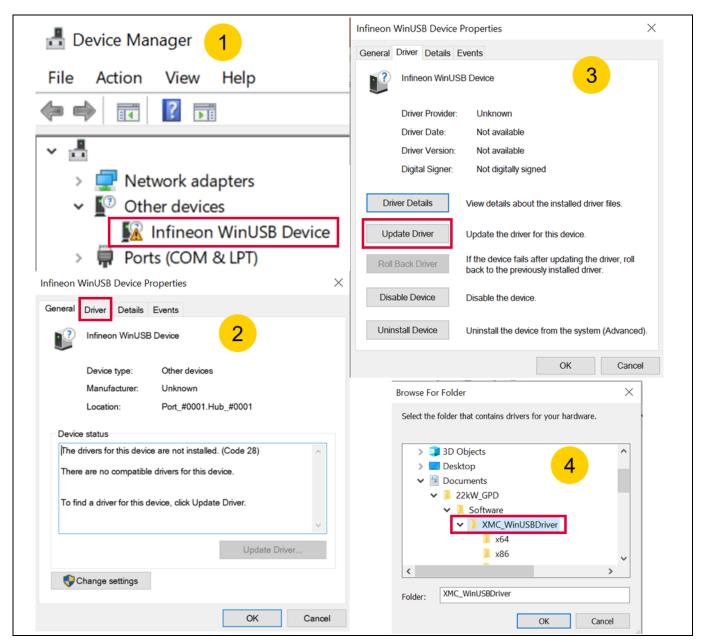

| 4.1.6    | Installing the WinUSB drivers                            |     |

| 4.1.7    | Setting up the XScope software oscilloscope              | 42  |

| 4.1.8    | Setting up the GUI                                       |     |

| 4.1.9    | Setting up the GPDTarget and PLECS model                 |     |

| 4.1.9.   |                                                          |     |

| 4.1.9.   | 0 1                                                      |     |

| 4.1.9.   | 3 Setting up the code generation and flashing            | 43  |

| 4.2      | Graphical Programming and Workflow                       | 43  |

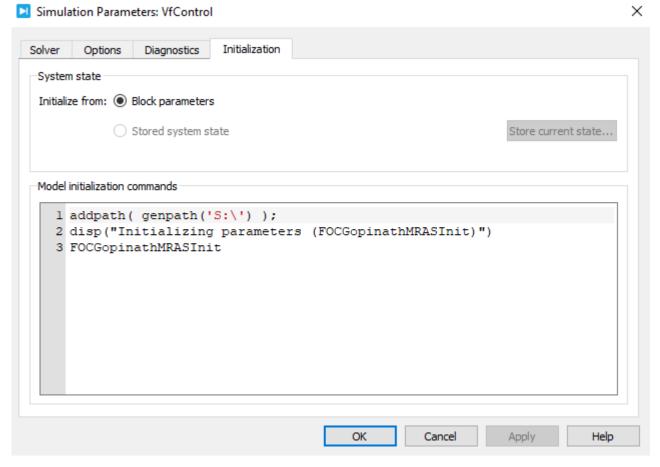

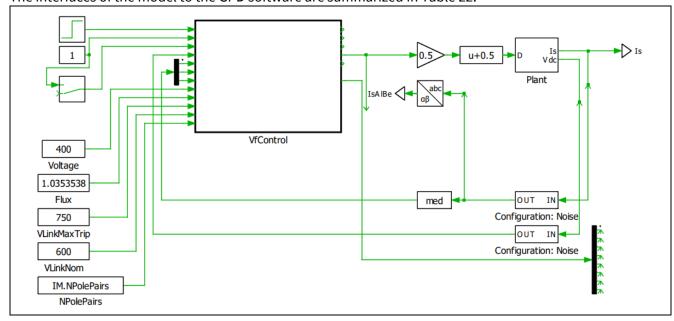

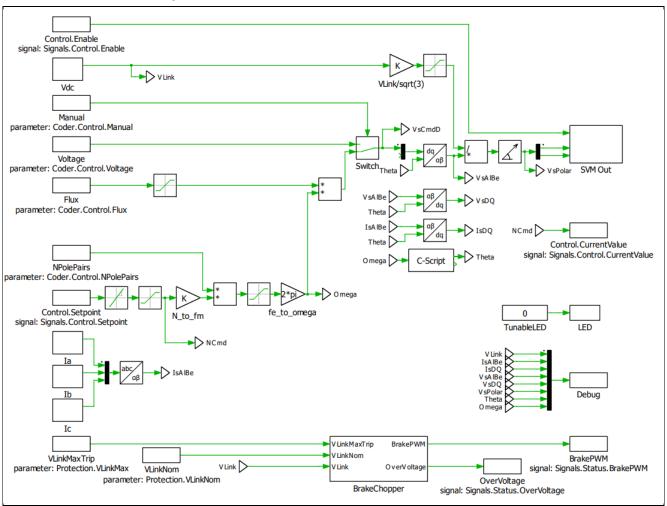

| 4.2.1    | Model configuration                                      | 43  |

| 4.2.2    | Coder configuration                                      | 44  |

| 4.2.3    | Parameter definition                                     | 45  |

| 4.2.4    | Code generation                                          | 46  |

| 4.2.5    | GPD target library reference                             |     |

| 4.2.6    | Example models                                           | 47  |

| 4.2.7    | V/f                                                      | 47  |

| 4.2.8    | Debugging with XScope                                    |     |

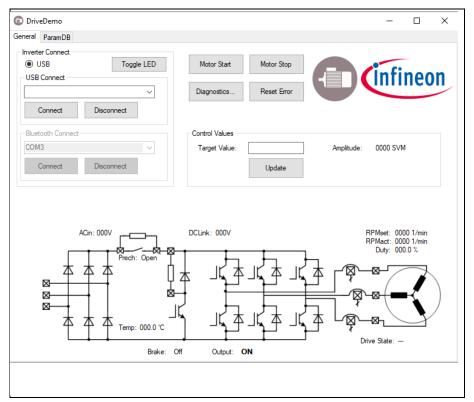

| 4.3      | GPD Operation                                            | 53  |

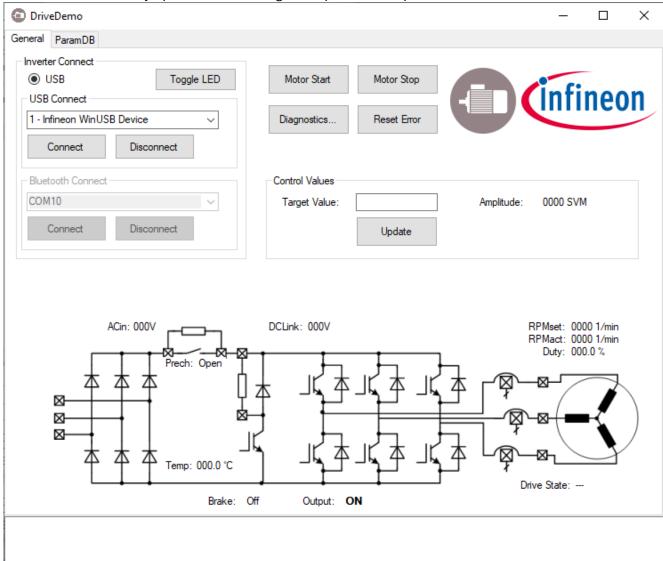

| 4.4      | General tab                                              | 53  |

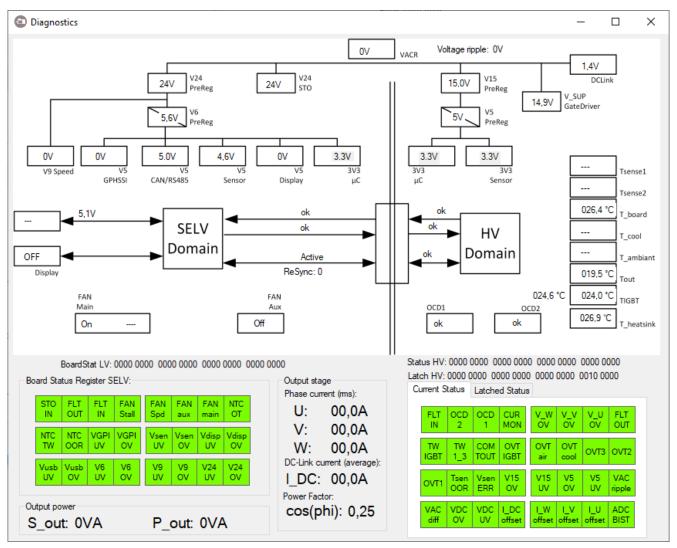

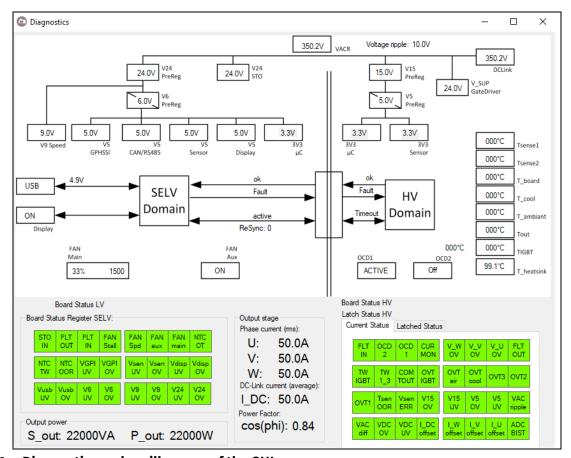

| 4.5      | Diagnostics view                                         | 54  |

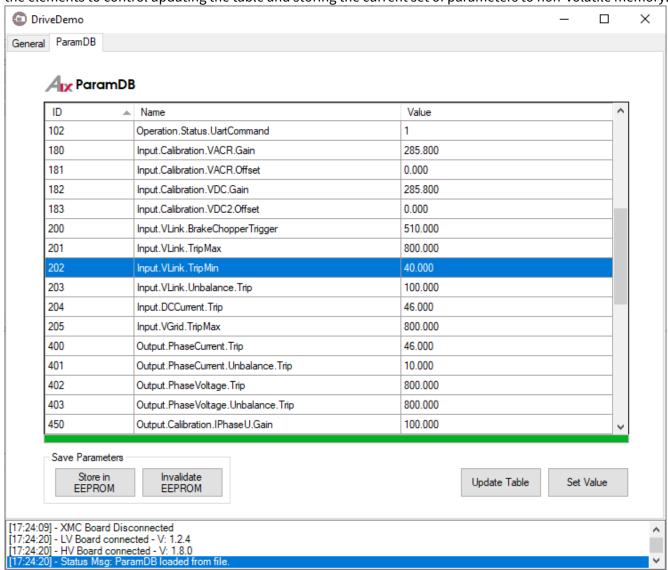

| 4.5.1    | ParamDB tab                                              | 57  |

| 5        | Commissioning                                            | 59  |

| 5.1      | Description of the functional blocks                     | 63  |

| 5.1.1    | Hardware partitioning                                    | 63  |

| 5.1.2    | Isolation coordination                                   | 65  |

| 5.1.3    | Board interconnection schemes                            | 66  |

| 5.1.4    | Supply schemes                                           | 67  |

| 5.1.5    | Component selection                                      | 67  |

| 5.2      | Setup two level slew rate gate driver                    | 69  |

| 6        | System performance                                       | 71  |

| 6.1      | Test results inverter start-up                           | 71  |

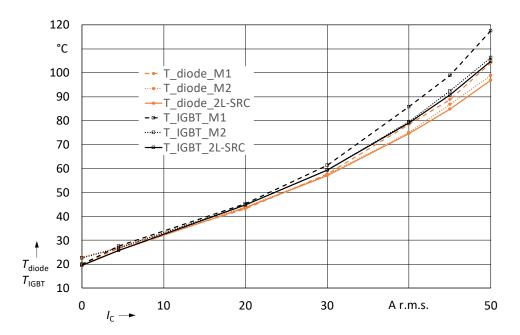

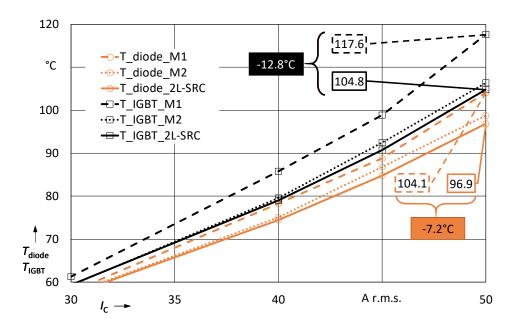

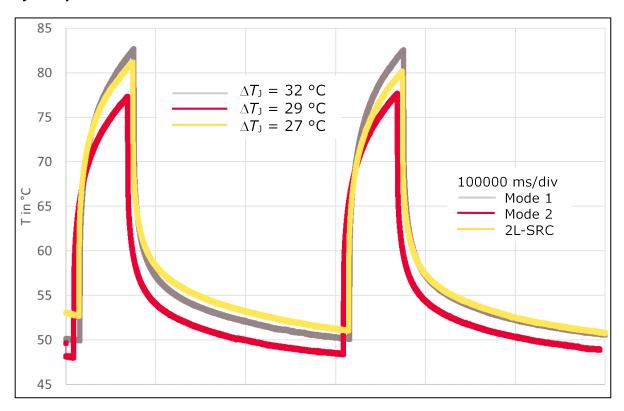

| 6.2      | Operation under rated conditions                         | 72  |

| 6.3      | Switching behavior of the IGBT – turn on/off             | 74  |

| 6.4      | Thermal behavior of the inverter under nominal operation | 75  |

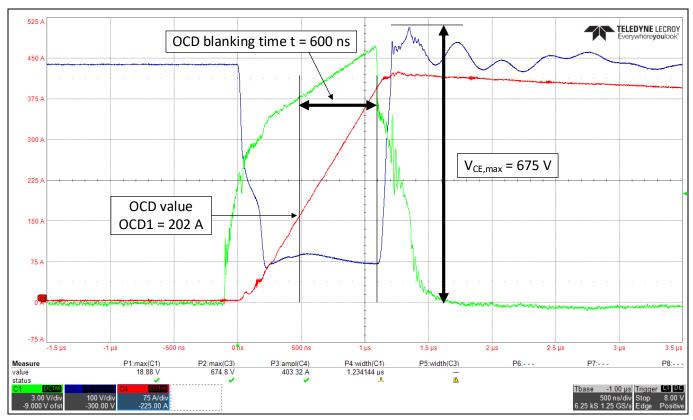

| 6.5      | Short-circuit measurement                                | 77  |

| 7        | References and appendices                                | 80  |

| 7.1      | Abbreviations and definitions                            |     |

| 7.2      | References                                               | 80  |

| <b>.</b> | ian kistam.                                              | 0.4 |

Reference design for motor general purpose drives

The reference board at a glance

## 1 The reference board at a glance

### 1.1 Delivery content

The reference kit is a general purpose drive developed for applications like pumps, fans, compressors, conveyor belts. The design has the look and feel of a typical drive and includes EMI filter, pre-charge and capacitor bank, isolated power supplies, power module, controls and heat sink with fan. It can be operated directly on a three-phase grid or by a external high voltage DC-supply, enabling a fast evaluation of Infineon's newest technologies like IGBT7, gate driver, current sensor and control in one system. This enables the unique opportunity to see the improvement by combining Infineon's newest technologies. You will see how the new IGBT7 modules work with the EICE™ gate driver, or test the accuracy of the current sensor.

The drive has been tested according to DIN EN IEC 61800-5-1. It passed the isolationstest according to the specified requirements of the shortcircuit powerterminals and shortcircuit SELV terminals.

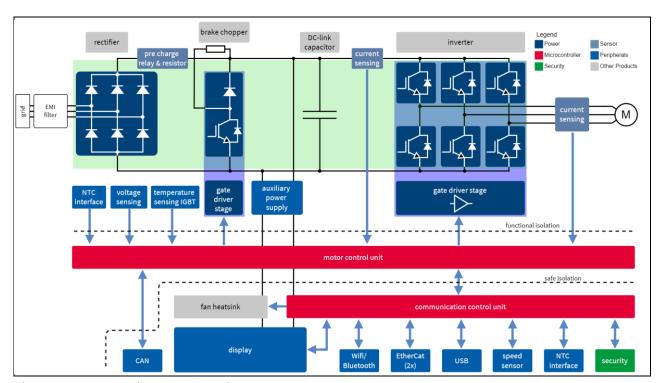

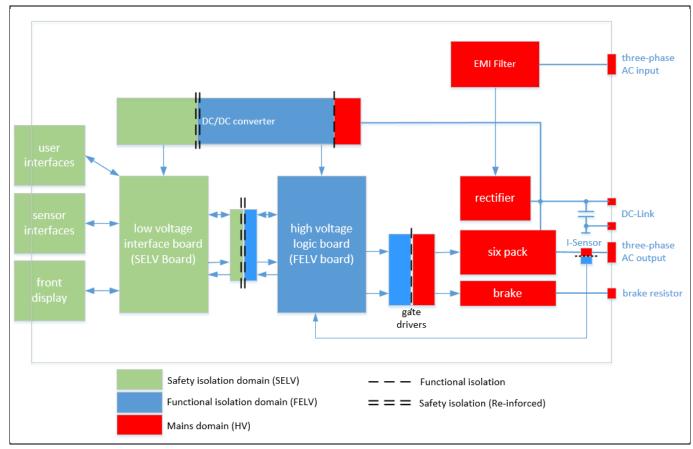

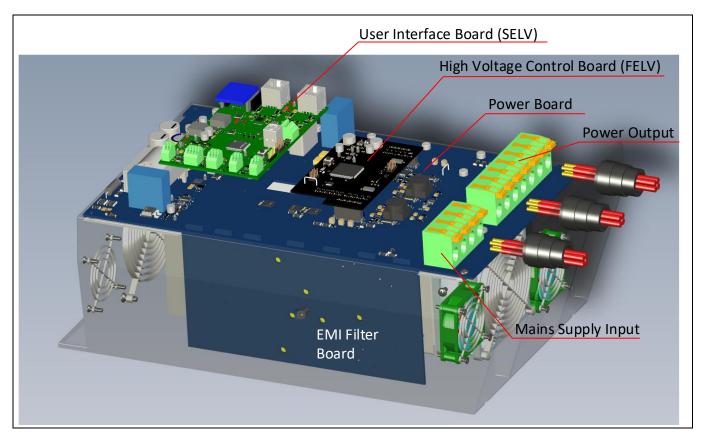

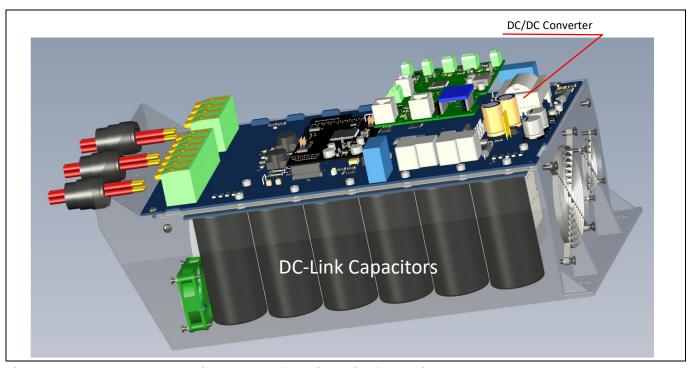

### 1.2 Block diagram

The block diagram of the inverter REF-22K-GPD-INV-EASY3B is shown in Figure 1. The board consists of five boards: power board, EMI filter, high-voltage logic board, low-voltage interface board, and the DC-link board which are mounted in one housing. For more details see Section 5.

Figure 1 Block diagram of the inverter

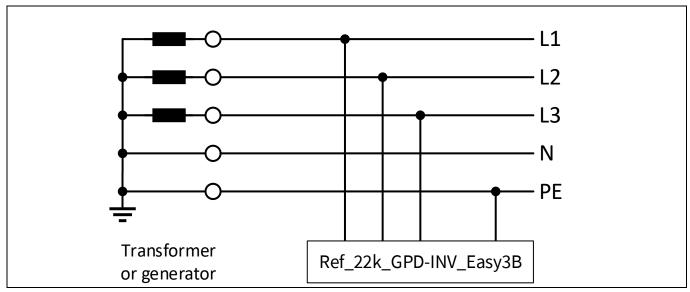

The reference kit REF-22K-GPD-INV-EASY3B is a industrial drive inverter which can be connected to a three-phase AC input. The reference kit includes an input EMI-filter. The AC voltage is rectified via the uncontrolled diode full bridge. The inrush current is limited by pre-charge circuitry. The rectified AC voltage is stabilized by a DC-link capacitor bank. The IGBT six pack allows for the modulation of a three-phase output voltage/current which can be varied in terms of its amplitude and frequency. This three-phase voltage is used for controlling the speed and torque of the motor. During braking or deceleration of the motor, energy is transferred back into the DC-link capacitor increasing the DC bus voltage. Therefore, a brake chopper is included that absorbs this energy by switching an external brake resistor across the DC bus capacitors. The

#### Reference design for motor general purpose drives

#### The reference board at a glance

The Infineon EasyPIM<sup>™</sup> 3B power module, FP100R12W3T7\_B11, includes the three-phase input rectifier, the six pack as well as the brake chopper. All IGBTs are driven by the Infineon EiceDRIVER<sup>™</sup> 1ED3240MC12H. The isolation coordination details of the unit can be found in Section 5.1.2.

The current measurement of the three-phase output current is done with TLI4971-A120T5 current sensors. The current signals are used for the motor control; additionally, these sensors are used to detect an external short circuit for the IGBT's. To protect the module against an internal short circuit, a fourth current sensor is integrated between the DC-link capacitor and the IGBT module.

The auxiliary voltage for the inverter is generated by a DC/DC switch mode power supply (SMPS) converter. The CoolSiC<sup>™</sup>-MOSFET IMBF170R1K0M1 is used in a flyback topology. More details about the flyback SMPS are listed in Section 5.1.5

The reference inverter uses two microcontrollers; one for control and one for communication. For control the XMC4800-F144F2048 is used, for communication the XMC4300-F100K256 AA is designed in. Both microcontrollers communicate via an UART interface. The communication microcontroller allows the inverter to be controlled via a touch-screen or a PC-GUI.

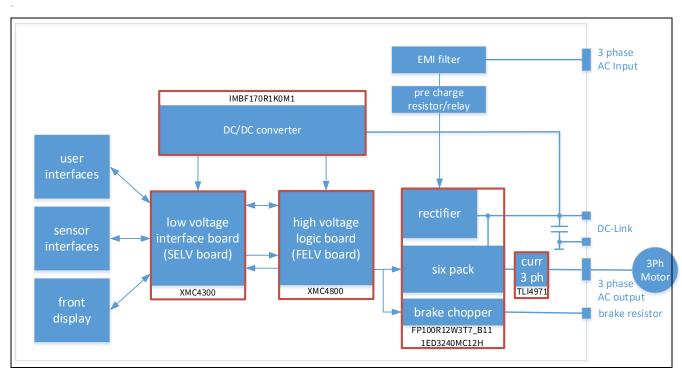

A simplified block diagram is shown in Figure 2. This block diagram shows the main components of the boards, the DC/DC SMPS converter, the low-voltage interface board (SELV board), high-voltage logic board (FELV board), the IGBT module incl. gate driver ICs, and the current measurement of the AC output. The main Infineon components used in the specific blocks are listed in the diagram.

Figure 2 Simplified block diagram of the inverter

#### 1.3 Main features

- FP100R12W3T7\_B11: EASY3B IGBT7 module for high-current and high-power density [3]

- TLI4971-A120T5: XENSIV<sup>™</sup> current sensor for measuring high currents with minimal power loss [4]

- 1ED3240MC12H: Gate driver for optimal EMI performance and reduced power losses [5]

- IMBF170R1K0M1: Infineon CoolSiC<sup>™</sup> MOSFET 1700 V enables direct drive by most flyback controllers [6]

- XMC4800-F144F2048 and XMC4300-F100K256 AA: XMC microcontrollers for inverter control and communication [7]

Reference design for motor general purpose drives

## The reference board at a glance

#### **Board parameters and technical data** 1.4

The key parameters of the REF-22K-GPD-INV-EASY3B are shown in Table 2.

Table 2 Parameters of REF-22K-GPD-INV-EASY3B

| Parameter                           | Symbol            | Conditions                          | Value                    | Unit |

|-------------------------------------|-------------------|-------------------------------------|--------------------------|------|

| Input line voltage                  | $V_{\rm in}$      | Three-phase AC ± 10%                | 380 480                  | V    |

| Input frequency                     | $f_{in}$          | ±3 Hz                               | 50 60                    | Hz   |

| Output voltage                      | $V_{ m out}$      | three-phase AC                      | 0 V 0.95 x input voltage | V    |

| Output frequency                    | $f_{ m out}$      |                                     | 0599                     | Hz   |

| Switching frequency of motor output | $f_{\sf sw}$      | Factory setting 4 kHz               | 4                        | kHz  |

| Rated power                         | $P_{rated}$       |                                     | 22                       | kW   |

| Rated current                       | $I_{rated}$       |                                     | 45                       | Α    |

| Low overload - base load power      | P <sub>LO</sub>   | T <sub>amb</sub> <= 35°C            | 22                       | kW   |

| Low overload - base load current    | I <sub>LO</sub>   |                                     | 45                       | А    |

| High overload - base load power     | Рно               |                                     | 18.5                     | kW   |

| High overload - base load current   | I <sub>HO</sub>   |                                     | 38                       | А    |

| Power losses                        | P <sub>loss</sub> |                                     | < 700                    | W    |

| Weight                              | $m_{inv}$         |                                     | < 10                     | kg   |

| Ambient temperature                 | $T_{amb}$         | Relative humidity RH; 30% < RH< 80% | 10 to 35                 | °C   |

#### The reference board at a glance

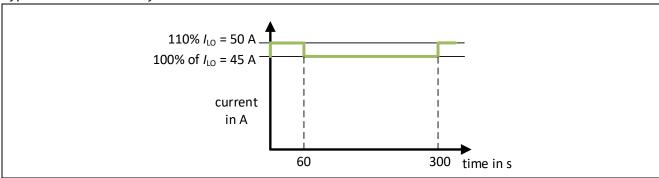

### 1.4.1 Overload profile normal duty

The normal duty (ND) load cycle assumes a uniform base load with low requirements during short acceleration times at high torque; see Figure 3. Typical applications when designing according to normal duty include:

- Pumps, fans and compressors

- Wet or dry blasting technology

- Mills, mixers, kneaders, crushers, agitators

- Basic spindles

- Rotary kilns

- Extruders

Typical converter load cycle:

Figure 3 Overload profile normal duty

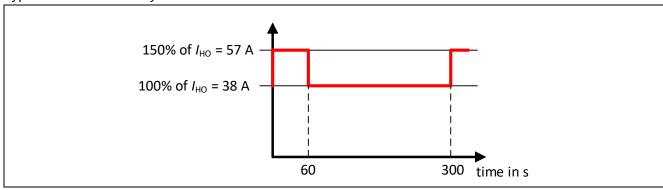

### 1.4.2 Heavy duty overload profile

The heavy duty (HD) load cycle permits dynamic accelerating phases at a reduced base load; see Figure 4. Typical applications when designing according to heavy duty include:

- Horizontal and vertical conveyor technology (conveyor belts, roller conveyors, chain conveyors)

- Centrifuges

- Escalators/moving stairways

- Lifters

- Elevators

- Gantry cranes

- Storage and retrieval machines

Typical converter load cycle:

Figure 4 Overload profile heavy duty

#### Reference design for motor general purpose drives

#### The reference board at a glance

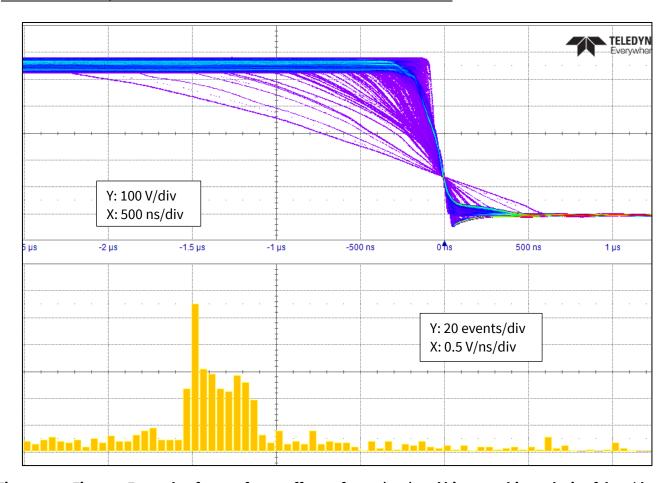

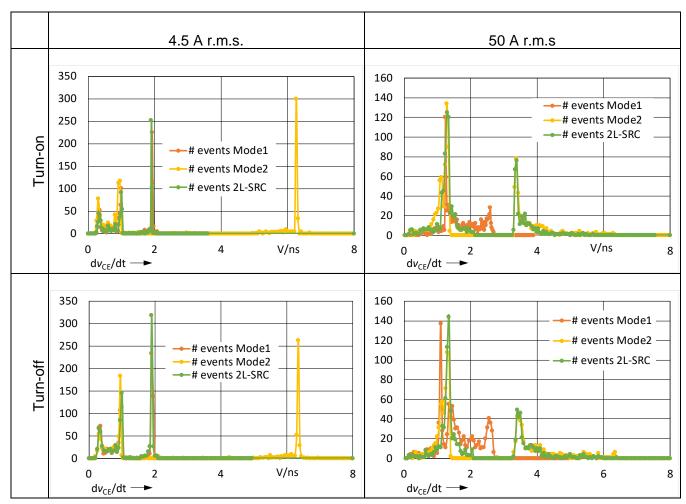

#### 1.5 Advantages of two level slew rate gate drivers

The dvCE/dt level of an IGBT turn-on event is usually higher at low temperatures and low currents. This means that if the dvCE/dt level is to be limited, the value of the gate resistor needs to be increased. Such limitations of dvCE/dt are common in motor drives, where the motor current also contains zero crossings. That is why the gate resistance should be dimensioned at 0 for example, or perhaps at 1/10 of the rated current of the power module at room temperature. It is known that high dvCE/dt has detrimental effects on motors. These effects include voltage doubling at the motor windings with longer motor cables and highstep voltage changes across the stator end-windings. [8]

While allowing the dvCE/dt levels to be capped, the higher gate resistor value causes higher switching losses, and thus, reduces the efficiency of the converter. It also causes higher junction temperatures, reduces the lifetime of the power modules, and increases cooling requirements.

If, however, two gate resistors can be used, higher gate resistor values can be applied for turn-on at low currents and low temperatures, thus limiting dvCE/dt levels. Also, lower gate resistor values can be used for turn-on at higher currents and temperatures to minimize losses.

On the other hand, the inductive turn-off overshoot may violate the power transistor's breakdown voltage Vbr. The turn-off at short circuit or overcurrent is especially critical. It is possible to mitigate this risk by increasing the gate resistance for turn-off. This results in higher switching losses, which in turn increases junction temperatures and cooling requirements.

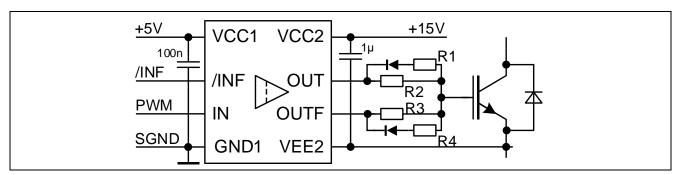

Figure 5 shows a schematic diagram for the proposed gate drive circuit using the 2L-SRC driver IC 1ED3240MC12H. The driver IC has a single control input for fast or slow switching (/INF), and a time in parallel, so that the IGBT gate is driven by the correlated combination of R1, R2, R3, and R4 in parallel. During slow operation, the IGBT is driven only by a combination of R1 and R1 in parallel with R2.

Schematic diagram of the proposed dual-gate resistor gate-drive circuit using Figure 5 1ED3240MC12H

(IN) for fast operation, both output terminals OUT and OUTF switch at the same time in parallel, so that the IGBT gate is driven by the correlated combination of R1, R2, R3, and R4 in parallel. During slow operation, the IGBT is driven only by a combination of R1 and R1 in parallel with R2.

User Guide 10 of 82 Revision 2.0

Reference design for motor general purpose drives

#### System design

#### System design 2

#### **Schematics** 2.1

The schematics of the design are available via Infineon.com. Keep in mind that the inverter consists of five boards, hence you will find one schematic for each board.

Table 3 Schematic overview

| Board name                                                            | File name in zip folder                   |

|-----------------------------------------------------------------------|-------------------------------------------|

| Power board                                                           | 22kW_Inverter_Power_Board_02.11.2022.pdf  |

| DC-link board                                                         | U109_GPD_DCLinkCaps_01.11.2022.pdf        |

| EMI filter                                                            | U109_22kWGPD_EMI-filter_02.11.2022.pdf    |

| High voltage logic board                                              | 22kW_Inverter_Logic_02.11.2022.pdf        |

| Low voltage interface                                                 | 22kW_Inverter_Interfaces_02.11.2022.pdf   |

| Connection between high voltage logic board and low voltage Interface | U109_GPD_FlexPCBConnector_02.11.2022.pdf  |

| Isolation sheet between power board and heat sink                     | U109_GPD_HeatsinkIsolation_01.11.2022.pdf |

| Gasket to separate clean and dirty air                                | U109_GPD_Sealing_01.11.2022.pdf           |

The Altium™ project files are available on request.

#### 2.2 Layout

#### 2.2.1 **Power board**

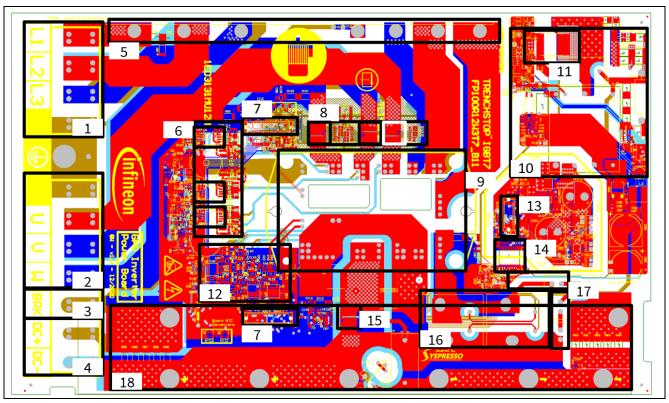

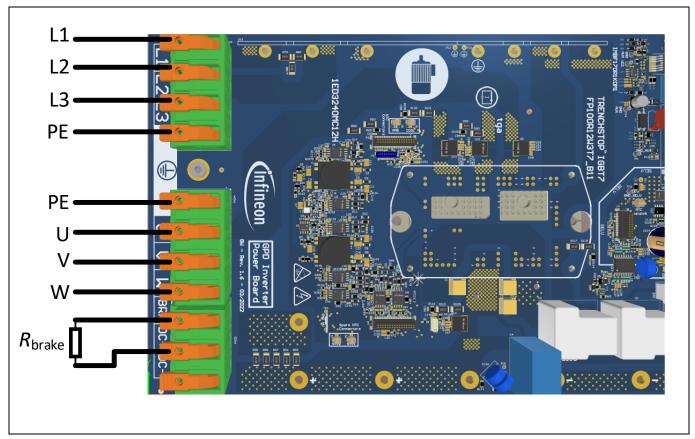

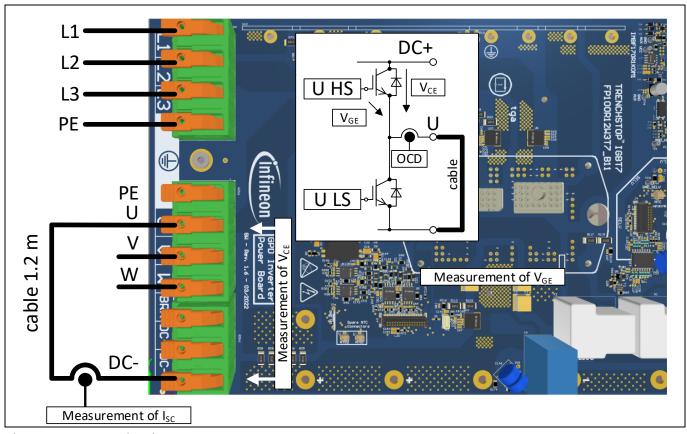

The layout of the power board is shown in Figure 6; in Table 4 you will find the names of each block.

The AC input connector (1), AC output connector (2), the brake resistor connector (3) as well as the DC-link connections (4) are located on the left hand side of the power board. The EMC filter is connected to the board in the area marked (5). The high-side gate drivers are located in the area marked (6) and the low-side gate driver are marked in section (12).

The interface to the high-voltage logic board (FELV board) is marked (7); this board has the interface connectors. The output phase current measurement is marked (8); all three-phase currents are measured, also the current between the DC-link capacitor and IGBT module is measured.

The IGBT module will be pressed in the area marked (9). The auxiliary power supply is located in the area marked (10), the SiC MOSFET is soldered to the PCB in the area (11). The DC-link board is screwed to the power board in the area marked (12).

The interface to the low-voltage interface board (SELV board) is marked (13). The safe isolation communication between the high-voltage logic board (FELV board) and low-voltage interface board (SELV board) is realized with the IC located on the PCB in area (14). The position of the pre-charge relay is shown at (16) and the pre-charge resistors are shown at (17).

### Reference design for motor general purpose drives

### System design

Layout of the power board Figure 6

Table 4 Functional block - power board layout

| Table 4 Full        | ctonat block - power board tayout                                                                                              |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------|

| <b>Block number</b> | Function                                                                                                                       |

| 1                   | AC input connector                                                                                                             |

| 2                   | AC output connector                                                                                                            |

| 3                   | Brake resistor connector                                                                                                       |

| 4                   | DC-link connector                                                                                                              |

| 5                   | EMI-filter connections                                                                                                         |

| 6                   | High-side gate driver with gate driver IC 1ED3240MC12H                                                                         |

| 7                   | Connector for motor control board                                                                                              |

| 8                   | Output phase current sensor measurement with TLI4971-A120T5                                                                    |

| 9                   | IGBT module with IGBT7 - FP100R12W3T7_B11                                                                                      |

| 10                  | Auxiliary power supply                                                                                                         |

| 11                  | CoolSiC <sup>™</sup> MOSFET IMBF170R1K0M1 of the auxiliary power supply                                                        |

| 12                  | Low-side gate driver with gate driver IC 1ED3131MC12H                                                                          |

| 13                  | Connector for communication interface board                                                                                    |

| 14                  | Isolation barrier for communication between high-voltage logic board (FELV board) and low voltage interface board (SELV board) |

| 15                  | DC-link current sensor TLI4971-A120T5                                                                                          |

| 16                  | Pre-charge relay                                                                                                               |

| 17                  | Pre-charge resistors                                                                                                           |

| 18                  | DC-Link                                                                                                                        |

|                     |                                                                                                                                |

#### Reference design for motor general purpose drives

#### System design

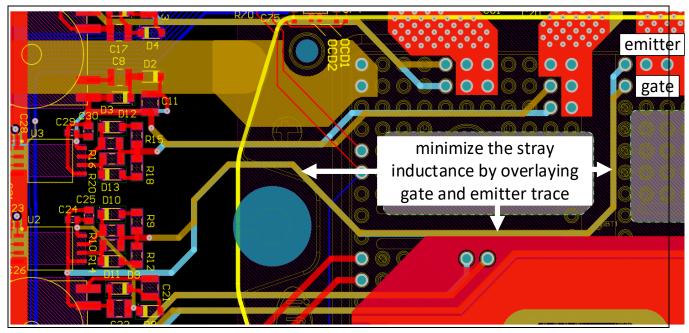

The gate layout of the high-side IGBT of the phase U is shown as an example in Figure 7. The traces of the emitter and gate trace are on top of each other, which minimizes any parasitic inductances.

Gate layout of the high-side IGBT of phase U Figure 7

#### 2.3 **Inverter cooling concept**

The main cooling of the IGBT is done by a heat sink and an integrated 92 mm fan with a temperature controlled flowrate of 0-270 m<sup>3</sup>/h. The air is drawn in the bottom of the unit and blown up through the heat sink to the outlet at the top of the enclosure, assuming a normal wall mounting position.

A 52 mm auxiliary fan cools the DC-link capacitors and operates at a constant speed with a flow rate of 20m<sup>3</sup>/h. The air is blown into an air channel at the bottom of the capacitor array. To provide an improved cooling over the entire surface of each capacitor the air is directed up one side and then channeled via small slits between each capacitor and then finally along the side of the heat sink to the air outlet at the top of the enclosure.

A second 52 mm fan, also operating at a constant speed, cools a third channel containing the EMI filter. The air flows beside the heat sink and over the indictors and capacitors of the EMI filter. This cooling channel has a separate air outlet at the top of the enclosure.

Reference design for motor general purpose drives

### System design

#### **Bill of material** 2.4

The complete bill of material is available on the download section of the Infineon homepage. A log-in is required to download this material.

BOM of the most important/critical parts of the evaluation or reference board (example) Table 5

| Board name                                                            | File name in zip folder                                |

|-----------------------------------------------------------------------|--------------------------------------------------------|

| Power board                                                           | BOM_22kW_Inverter_Power_Board_v1.3_01.11.2022.xlsx     |

| DC-link board                                                         | BOM_U109_GPD_DCLinkCaps_v1.0_01.11.2022.xlsx           |

| EMI filter                                                            | BOM_U109_22kWGPD_EMI-filter_V2_v1.0_01.11.2022.xlsx    |

| High voltage logic board                                              | BOM_22kW_Inverter_Logic_v1.2_01.11.2022.xlsx           |

| Low voltage interface                                                 | BOM_U109_22kW_Inverter_Interfaces_v1.2_01.11.2022.xlsx |

| Connection between high voltage logic board and low voltage Interface | BOM_U109_GPD_FlexPCBConnector_v1.0_01.11.2022.xlsx     |

#### **Connector details** 2.5

Connectors of the power board:

Table 6 **Connector PH1**

| PIN | Label | Function                                                   |

|-----|-------|------------------------------------------------------------|

| 1   | Earth | Earth potential for safe operation always connect to earth |

| 2   | L3    | Line feeder cable phase L3                                 |

| 3   | L2    | Line feeder cable phase L2                                 |

| 4   | L1    | Line feeder cable phase L1                                 |

Table 7 **Connector PH2**

| PIN | Label | Function                                                                       |

|-----|-------|--------------------------------------------------------------------------------|

| 1   | Earth | Earth potential for safe operation always connect to earth                     |

| 2   | DC-   | DC-minus voltage                                                               |

| 3   | DC+   | DC-plus voltage, the brake resistor must be connected here                     |

| 4   | brake | The brake resistor must be connected here, it is connect between DC+ and brake |

| 5   | W     | Motor feeder cable phase W                                                     |

| 6   | V     | Motor feeder cable phase V                                                     |

| 7   | U     | Motor feeder cable phase U                                                     |

### Reference design for motor general purpose drives

## System design

Connectors of the user interface board:

#### **Connector P1** Table 8

| PIN | Label   | Function                  |

|-----|---------|---------------------------|

| 1   | SPEED_1 | Input signal speed sensor |

| 2   | V9_SELV | 9 V power supply          |

#### Table 9 **Connector P2**

| PIN | Label | Function         |

|-----|-------|------------------|

| 1   | Input | Input signal NTC |

| 2   | GND   | Ground           |

#### Table 10 **Connector P4**

| PIN | Label | Function       |

|-----|-------|----------------|

| 1   | VCC   | Supply voltage |

| 2   | D-    | Data signal -  |

| 3   | D+    | Data signal +  |

| 4   | GND   | Ground         |

The USB port for remote control via the PC-GUI can be found at the front side of the inverter.

#### Table 11 **Connector P14**

| PIN | Label       | Function                  |

|-----|-------------|---------------------------|

| 1   | VCC         | Supply voltage            |

| 2   | VCC         | Supply voltage            |

| 3   | GND         | Ground                    |

| 4   | STOA        | Safe torque off Channel A |

| 5   | STOB        | Safe torque off Channel B |

| 6   | Chassis_GND | Chassis GND               |

Reference design for motor general purpose drives

## System design

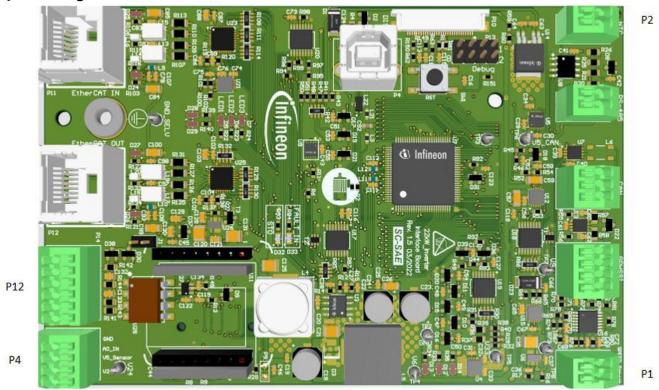

Figure 8 Interfaceboard

User Guide 16 of 82 Revision 2.0

Reference design for motor general purpose drives

#### **Software structure**

#### 3 **Software structure**

#### **Overview** 3.1

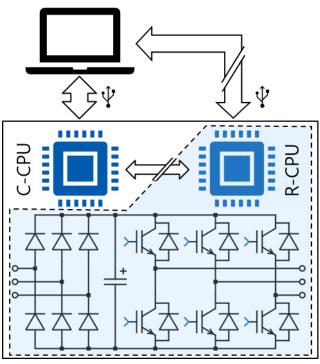

The system depicted can be simplified to the structure in Figure 9 from the perspective of the interacting software applications. The system contains two central processing units (CPUs) which both are connected to each other and to a computer.

The R-CPU (real-time CPU) executes the control of the connected power electronic setup. It is connected to C-CPU (communication CPU) to exchange parameters and to respond to commands from the user. Additionally, it is connected to the computer to support a live view of internal quantities of the software for debugging purposes.

The C-CPU connects the user interface running on the computer to the R-CPU handling the control. It provides access to the parameter database for the user and the R-CPU.

The computer is used to execute the graphical user interface (GUI) provided to control and parameterize the connected system. It can optionally run the software oscilloscope XScope to allow inspection of internal quantities of the R-CPU software.

The software structure of both CPUs and the involved software components for communication are described in more detail in the subsequent sections.

The USB connection between R-CPU and computer needs a isolation ! (see Section 4.1.7)

Figure 9 System abstraction focusing on communication

#### 3.2 **R-CPU Software**

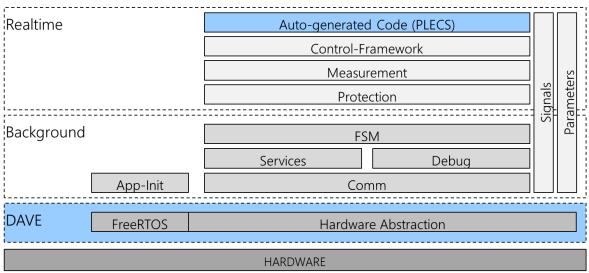

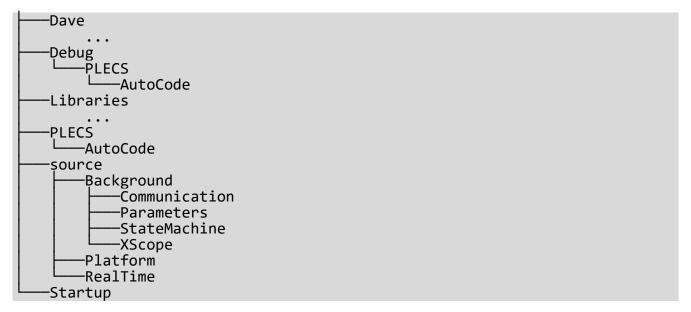

The structure of the software for the R-CPU is depicted in Figure 10 as a layered structure. The software is divided into three main parts or domains. The Real-time Domain takes care of all relevant functions that require real-time performance such as closed-loop control or system protection. The Background Domain handles all other functions like communication or the main state machine of the system. These layers are implemented ideally as completely abstract and platform independent code.

#### Reference design for motor general purpose drives

#### Software structure

The third layer therefore provides an abstract application programming interface (API) to the other layers and implements the platform specific code. This *Hardware Abstraction* layer is mostly provided by the toolchain DAVE.

The connection between the layers is achieved by program flow, by signals and by parameters.

Program flow defines which component executes what part of the software at a given time. Execution is passed at program start to the initialization code which organizes how the runtime is distributed between the components. Mostly tasks of a real-time operating system (RTOS) and interrupts (IRQs) are used to structure the available runtime.

Signals are implemented as a globally available structure of variables which can be accessed by all code parts and reflect the overall state of the software and are thus volatile in nature.

Parameters on the other hand are used to store quantities which are non-volatile and parameterize the behavior of the software.

The subsequent sections give more detail for each layer of the software and the folder structure of the code base.

Figure 10 Structural representation of the implemented software

#### 3.2.1 Real-time Domain

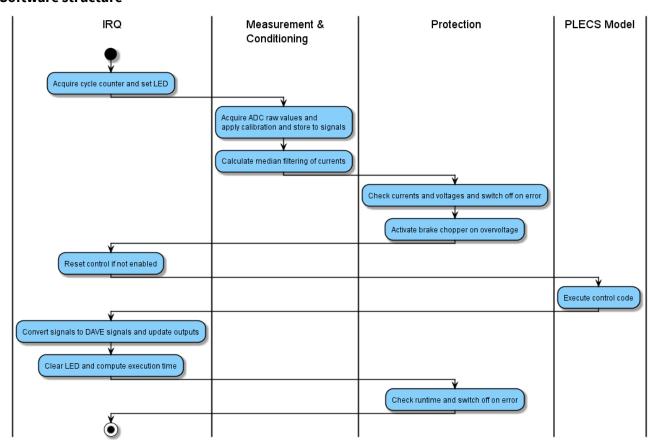

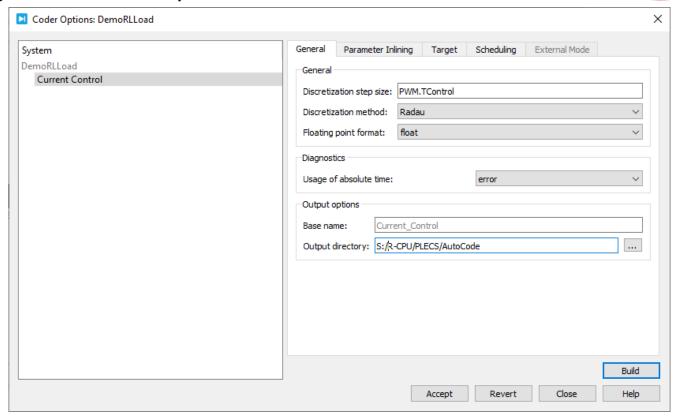

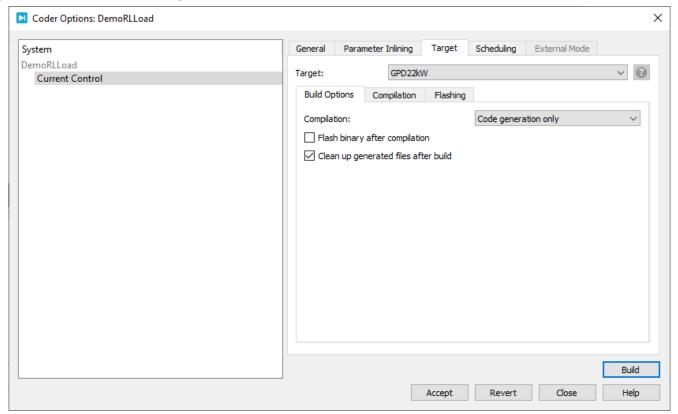

The *Real-time Domain* contains all components which are required for the real-time functions of the software. The main functions are being realized by model-based development within the simulation tool PLECS and exported as generated C code. The code generation is controlled by the target support package *GPDTarget* within PLECS which connects the code to the control framework of the software structure. This framework integrates the generated code into the overall code structure in terms of program flow and signal flow.

Figure 11 depicts the program flow of the *Real-time Domain*. The swim lanes describe which part of the real-time domain is responsible for the processing of the involved steps.

The real-time behavior is entirely realized within an interrupt handler which is triggered by the signal generation of the hardware platform, e.g. the space vector modulator (SVM) or – used here – the analog-to-digital conversion (ADC). The execution rate is an integer divider of the SVM carrier frequency. The IRQ handler therefore is the first part of the code that is being executed and starts the processing. The step *Measurement & Conditioning* acquires and pre-processes inputs required for *Protection* and *PLECS model*, mostly analog and digital inputs to the hardware. The step *Protection* realizes the safe operation of the system by checking measurements and internal quantities against trip levels. The control code is executed as part of the step *PLECS Model* and yields output signals which are then being distributed to the respective destinations, mainly the SVM generator. Part of the *Protection* is to supervise the calculation time of the real-time IRQ.

#### Reference design for motor general purpose drives

#### **Software structure**

Figure 11 Program flow of the real-time control framework

The following sections describe details of the structural components as shown in Figure 11.

### 3.2.1.1 Auto-generated Code

The auto-generated code is compiled as part of the complete project. It consists of one main code block (.h/.c file) representing the top-level PLECS model, possibly additional model files of subcomponents, and additional files which make sure that the model-based code can be seamlessly integrated into the framework. Table 12 lists the files of the sensorless Field Oriented Control (FOC) as an example for the generated files.

Table 12 Auto-generated files of the GPDTarget

| File                    | Description                                                                       |

|-------------------------|-----------------------------------------------------------------------------------|

| VfControl (.h/.c),      | Main file of the control model; name and content are model specific               |

| parameterentry.h        | Declaration of the C struct of a parameter entry                                  |

| parameterlist (.h/.c)   | List of parameters which can be manipulated; This list is being sent to the C-CPU |

|                         | and made available in the parameter database.                                     |

| realtime (.h/.c)        | Main interface and entry point of control flow; Name and content are model-       |

|                         | agnostic and offer a fixed interface to the remaining code.                       |

| debugsignallist (.h/.c) | Signals made available by the Debug Blocks of the model; These signals are        |

|                         | available within the XScope software scope.                                       |

#### 3.2.1.2 Control-Framework

The purpose of the *Control Framework* is to connect the auto-generated code of the PLECS model to the other software components. It contains the code which sets up the real-time IRQ handler based on the ADC module, the handler itself and other required functions.

### Reference design for motor general purpose drives

#### **Software structure**

The main interfaces to the auto-generated code of the PLECS model are program flow, signals and parameters. The *GPDTarget* itself is able to directly generate access to the global *Signals* and to provide a list of *Parameters*. The program flow, however, is explicitly provided by the integration of function calls to the IRQ handler as part of the *Control Framework*.

### 3.2.1.3 Measurement and Conditioning

The component *Measurement* is responsible for acquiring all required digital and analog input signals of the system. Upon execution, it reads all inputs from the hardware via the *Hardware Abstraction layer (DAVE)* and applies a two-point calibration in form of a gain and an offset parameter to convert the raw signals from the analog-to-digital conversion to SI-based quantities like currents in Ampere or voltages in Volt. Optionally, the component *Conditioning* provides filters to incoming signals such as low-pass filtering of noisy measurements.

Table 13 List of measurements

| Input | Signal name                      | Description                                                                          |

|-------|----------------------------------|--------------------------------------------------------------------------------------|

|       | Signals.Measurement.Iph_U        | Pseudo-differentially(1) determined phase                                            |

|       |                                  | current in Ampere.                                                                   |

|       | Signals.Measurement.Iph_V        | Pseudo-differentially(1) determined phase                                            |

|       |                                  | current in Ampere.                                                                   |

|       | Signals.Measurement.Iph_W        | Current of phase W is determined by Kirchhoff's                                      |

|       |                                  | law: IW=-IU-IV.                                                                      |

|       | Signals.Measurement.IDC          | Pseudo-differentially(1) determined DC-link                                          |

|       |                                  | current in Ampere.                                                                   |

|       | Signals.Measurement.VDC          | DC-link voltage in Volts.                                                            |

|       | Signals.Measurement.VACR         | Voltage after Full Bridge Rectifier (before Relay) in                                |

|       |                                  | Volts.                                                                               |

|       | Signals.Measurement.VOUT_U       | Phase voltage of the AC output in Volts. This is a                                   |

|       | C' LM LVOUT V                    | slow(3) measurement.                                                                 |

|       | Signals.Measurement.VOUT_V       | Phase voltage of the AC output in Volts.                                             |

|       | Signals.Measurement.VOUT_W       | Phase voltage of the AC output in Volts.                                             |

|       | Signals.Measurement.offsetI      | Average of the three reference voltages of the                                       |

|       | Circula Management NTC1          | phase current sensors.                                                               |

|       | Signals Massurement NTC1         | Placeholder(2) for NTC1 temperature reading.                                         |

|       | Signals.Measurement.NTC2         | Temperature measurement in °C of sensor NTC2.                                        |

|       |                                  | Gain and offset calculated at approx. 25°C and 80 °C. This is a slow(3) measurement. |

|       | Signals.Measurement.NTC3         | Temperature measurement in °C of sensor NTC3.                                        |

|       | Signals.Measurement.NTCS         | Gain and offset calculated at approx. 25 °C and                                      |

|       |                                  | 80 °C. This is a slow(3) measurement.                                                |

|       | Signals.Measurement.NTC_cool     | Placeholder(2) for NTC_cool temperature                                              |

|       | orginate.ineasarement.ivi o_coot | reading.                                                                             |

|       | Signals.Measurement.V15          | Measurement of the 15 V supply rail in Volts. This                                   |

|       |                                  | is a slow(3) measurement.                                                            |

|       | Signals.Measurement.V5           | Placeholder(2) for 5 V supply rail in Volts.                                         |

|       | Signals.Measurement.NTC_ambient  | Temperature measurement in °C of sensor                                              |

|       | _                                | NTC_ambient. Gain and offset calculated at                                           |

|       |                                  | approx. 25 °C and 80 °C. This is a slow(3)                                           |

|       |                                  | measurement.                                                                         |

|       |                                  |                                                                                      |

| Software structure                  |                                                                                          |  |  |  |  |

|-------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|

| Signals.Measurement.NTC_dirty       | Temperature measurement in °C of sensor NTC_dirty for hardware revision 0 or gate driver |  |  |  |  |

|                                     | supply readback in Volts for hardware revision 2.                                        |  |  |  |  |

| Signals.Measurement.NTC_IGBT        | Temperature measurement in °C of sensor                                                  |  |  |  |  |

|                                     | NTC_IGBT. Gain and offset calculated at approx.                                          |  |  |  |  |

|                                     | 80 °C and 120 °C. This is a slow(3) measurement. A                                       |  |  |  |  |

|                                     | low-pass filter is being applied to this value.                                          |  |  |  |  |

| Signals.Measurement.Fil_Iph_U       | Median3-filtered version of the unfiltered,                                              |  |  |  |  |

|                                     | calibrated signal.                                                                       |  |  |  |  |

| Signals.Measurement.Fil_Iph_V       | Median3-filtered version of the unfiltered,                                              |  |  |  |  |

| Signats.medsurement.rit_ipii_v      | calibrated signal.                                                                       |  |  |  |  |

| Signals.Measurement.Fil_Iph_W       | Median3-filtered version of the unfiltered,                                              |  |  |  |  |

|                                     | calibrated signal.                                                                       |  |  |  |  |

| Signals.Measurement.Fil_IDC         | Median3-filtered version of the unfiltered,                                              |  |  |  |  |

| Signatis.incusurement.i N_15 C      | calibrated signal.                                                                       |  |  |  |  |

| Signals.Measurement.Fil_VDC         | Median3-filtered version of the unfiltered,                                              |  |  |  |  |

|                                     | calibrated signal.                                                                       |  |  |  |  |

| Signals.Measurement.Fil_VACR        | Median3-filtered version of the unfiltered,                                              |  |  |  |  |

| Sibilationica di cilicitat it_vvoit | calibrated signal.                                                                       |  |  |  |  |

|                                     |                                                                                          |  |  |  |  |

<sup>(1)</sup> Pseudo-differential means: both terminal voltages (current signal and reference voltage) of the current sensor are acquired and the difference is being calculated in software.

#### 3.2.1.4 Protection

The component *Protection* provides a safety mechanism (in terms of intrinsic safety, not functional safety) by checking if all relevant quantities are within the specified boundaries. If a quantity crosses a predefined and parameterizable threshold, an error is raised which results in executing an emergency shutoff and storing the cause for the error. Additionally, the main state machine is triggered to change state into the error state. The emergency shutoff forces all power electronic switching signals to their inactive state and opens the precharge relay as fast as possible to protect the system from overvoltages and overcurrents. Table 14 lists all protective measures, the respective signals and parameters.

Table 14 List of protective measures

| Measures against     | Signal name(s)                         | Parameter                      | Display in GUI            |

|----------------------|----------------------------------------|--------------------------------|---------------------------|

| IRQ calculation time | Signals.Status.<br>IRQTimeTotal        | Parameters.Protection.IRQMax   | ADC_BIST                  |

| Overcurrent phases   | Signals.Measurement. Fil_Iph_{U, V, W} | Parameters.Protection.IOut     | offset_Isensor{U,V,<br>W} |

| Overcurrent DC link  | Signals.Measurement.<br>Fil_IDC        | Parameters.Protection.IDC      | offset_IsensorDC          |

| Overvoltage DC link  | Signals.Measurement.<br>Fil_VDC        | Parameters.Protection.VLinkMax | VDCL_OV(1)                |

| Undervoltage DC link | Signals.Measurement.<br>Fil_VDC        | Parameters.Protection.VLinkMin | VDCL_UV                   |

|                      |                                        |                                |                           |

<sup>(2)</sup> Not all physical sensors are available in the software due to ADC sampling restrictions of the underlying low-level driver and peripheral units of the controller.

<sup>(3)</sup> Due to the sampling structure of the peripheral modules, some values are not sampled for each control event.

### Reference design for motor general purpose drives

| Software structure                 |                                                             |                                            |           |

|------------------------------------|-------------------------------------------------------------|--------------------------------------------|-----------|

| Overvoltage Grid                   | Signals.Measurement.<br>Fil_VACR                            | Parameters.Protection.VGrid                | ERROR(2)  |

| Overvoltage phases                 | Signals.Measurement.VO<br>UT_{U, V, W}                      | Parameters.Protection.VOut                 | ERROR(2)  |

| Unbalance between<br>VGrid and VDC | Signals.Measurement. Fil_VDC, Signals.Measurement. Fil_VACR | Parameters.Protection.VLinkUnb alance      | VACR_Diff |

| Overtemperature(3)                 | Signals.Measurement.NT<br>C2                                | Parameters.Protection.NTC2_Trip            | TSENS_OOR |

| Overtemperature(3)                 | Signals.Measurement.<br>NTC3                                | Parameters.Protection.NTC3_Tri<br>p        | TSENS_OOR |

| Overtemperature(3)                 | Signals.Measurement.NT<br>C_ambient                         | Parameters.Protection.NTC_ambient<br>_Trip | TSENS_OOR |

| Overtemperature(3)                 | Signals.Measurement.<br>NTC_IGBT                            | Parameters.Protection.NTC_IGBT _Trip       | OVT_IGBT  |

| Overtemperature(3)                 | Signals.Measurement.NT<br>C_IGBT                            | Parameters.Protection.NTC_IGBT_W arning    | TW_IGBT   |

| Supply failure(3)                  | Signals.Measurement.<br>V15                                 | Parameters.Protection.V15OV                | V15_OV    |

| Supply failure(3)                  | Signals.Measurement.V1<br>5                                 | Parameters.Protection.V15UV                | V15_UV    |

| Communication timeout(3)           | Signals.Status.UARTPa<br>cketTimeout                        | N/A                                        | ERROR(2)  |

| OCD(4)                             | N/A                                                         | N/A                                        | OCD1      |

- (1) This error activates the brake chopper.

- (2) ERROR represents a collective error, i.e. this indicator is active if any error occurs.

- (3) These checks are being processed in the *Background Domain*, i.e. in a task.

- (4) This check is realized by an interrupt handler, acting upon a digital input.

#### **Background Domain** 3.2.1.5

User Guide

The Background Domain contains all code parts which are not time critical. The code is structured in tasks as provided by the underlying real-time operating system (RTOS, here FreeRTOS). This way, a blocking

#### Reference design for motor general purpose drives

#### **Software structure**

programming paradigm can be used which leads to small and portable code fragments. The main components of the background processing are described in the subsequent sections.

#### 3.2.1.6 Tasks

Tasks are the main building blocks of the application. Each task handles a specific part of the software. Since tasks can be blocked, the programming paradigm of synchronous operation can easily be used to control all required functions with a small code base. Table 15 lists the tasks of the R-CPU software and explains their purpose.

Table 15 Tasks of the R-CPU software

| Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          | Priority |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| StateMachineTask  | The statemachine task handles the main control flow on system level. The main states are Initialization, Configuration, Precharge, Active an Error. The state transitions are mainly controlled by events and timing. Events are detected by Boolean flags stored as Signal.                                                                                                                                                                         | 5        |

| UARTInterfaceTask | This task handles high-level functionality of the communication interface. It is implemented as a state machine as well and handles the phases synchronization, parameter exchange, error handling and the actual operation. State transitions are triggered by reception of a data packet or by Boolean flags stored as Signals. Data packet reception is realized by a queue. Data packet transmission is done directly.                           | 4        |

| UARTLowLevelTask  | This task takes care of the low-level data reception. Packet parsing and checksum calculation as well as verification is done here. The chosen approach utilizes an IRQ-less implementation where the physical reception rate and the built-in FIFO depth of the hardware unit is carefully balanced to prevent data overflows even without IRQs. Once a data packet is correctly received it is handed over to the UARTInterfaceTask using a queue. | 5        |

| XScopeTask        | The XScopeTask is used to send the accumulated data of the XScope during control IRQs to the connected computer using the WinUSB driver of the hardware abstraction.                                                                                                                                                                                                                                                                                 | 4        |

(Priority: high numbers mean high priority)

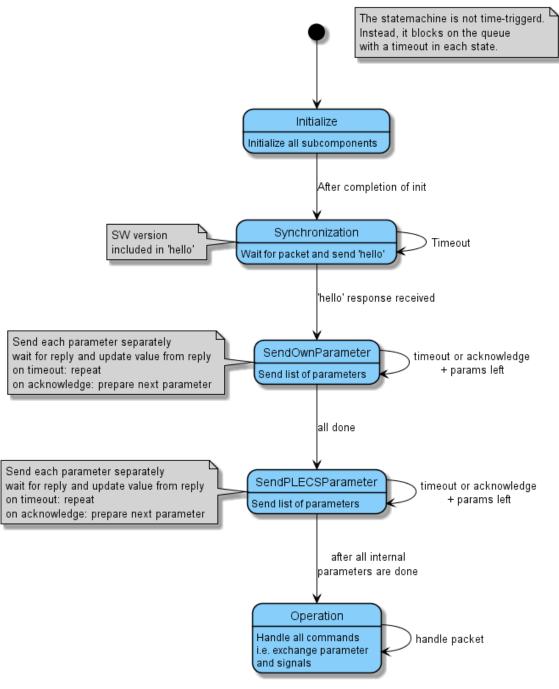

### 3.2.1.7 Main State Machine

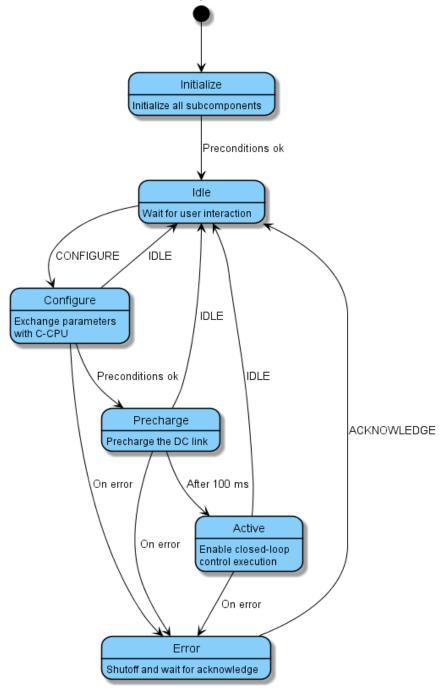

The main state machine determines the behavior of the software and therefore the whole setup on system level

Usually, after starting from reset, multiple steps are required in a specific order to reach the operational state. Additionally, certain inputs to the system might be required before operation is possible. The state machine handles all this on a structured, much more abstract level than pure program flow does. Figure 12 depicts the main state machine in the R-CPU software and thus describes the high-level software functions. It is mainly controlled by the user via the graphical user interface, sending commands to the C-CPU to forward them finally to the R-CPU and the state machine. Although the states themselves execute on the CPU in a cyclic fashion to allow both asynchronous and synchronous programming paradigms, they usually are written in a way that the program flow stays in the current state until the conditions are met for a transition. These self-transitions are not depicted.

The implemented state machine is rather simple and intended as a framework for future extensions. It operates as shown in Figure 12:

After reset, the state machine starts in the state Initialize where all subcomponents are brought into operational state. Once everything has been set up, the state machine transitions to the state Idle.

#### Reference design for motor general purpose drives

#### **Software structure**

Idle waits for user interaction. The command CONFIGURE, sent by the GUI, takes the system out of the waiting state and triggers the transition to the state Configure.

In Configure, all parameters are exchanged between the two CPUs. After that, all relevant data is present in the R-CPU to actually proceed to preparing the power electronics by transitioning to the state Precharge. Precharge takes care of a precharged DC link and controlling the relevant contactors. After the precharging preconditions are met, the system transits to the state Active.

The state Active finally releases the control code from reset and allows switching patterns to be forwarded to the hardware. If requested to stop by the command IDLE, the state machine transits to the state Idle again to wait for the next phase of operation.

Nearly all states transition to the state Error upon erroneous behavior of any supervised subcomponent. Here, the system is being brought into a safe state by disabling switching signals and taking care of the proper position of all contactors.

At any time, the state and error information are being transmitted to the C-CPU and thus to the GUI.

Figure 12 Main state machine

Reference design for motor general purpose drives

#### **Software structure**

#### 3.2.1.8 UART Communication

Another part of the *Background Domain* are all the parts involved in the communication to the C-CPU. Since the communication channel is used for multiple purposes, a layered and packetized approach has been implemented. There is a low-level layer taking care of the platform specifics of sending and receiving packets as well as checking the packet integrity by checksum verification. A high-level layer provides the actual packet handling.

In this system setup, two independent systems are talking to each other, which might be in a non-synchronized state. This occurs, if the systems are being started at different times (e.g. by restarting the R-CPU after a program download). The high-level layer takes care of this by implementing a state machine of its own which detects and corrects synchronization losses. This high-level layer finally distributed commands and data received and controls data sent back.

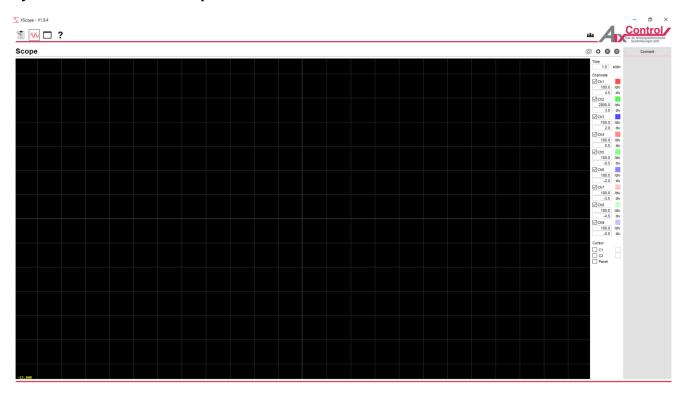

### 3.2.1.9 XScope

The final component present in the *Background Domain* is the *XScope* functionality which enables a live view of internal variables of the software or the model-based components. Two parts work together to allow a non-intrusive data transfer out of the *Real-time Domain*. Within the main program flow of the real-time code, the first part is usually realized as a simple function call and reads a set of channels and transfers the data to a buffer structure with fixed timing (i.e. once every n samples). The second part is implemented as a task and processes a large chunk of sampled channels at once in the *Background Domain* and transfers it to the accompanying *XScope* graphical user interface by whatever data channel is present on the system. The channels to display are either hard-coded or – if appropriately programmed – can be selected by the user at run-time.

Here, the data channel in use is provided by the *Hardware Abstraction* and uses a WinUSB connection over the USB port of the R-CPU.

## 3.2.2 Hardware Abstraction (DAVE)

The Hardware Abstraction is typically realized by low-level code or libraries or more complex frameworks provided by the silicon vendor. Here, DAVE is being used to provide access to the underlying microcontroller hardware. The main parts provided by DAVE are the space vector modulator (SVM) for switching signal and timing event generation, timers to generate events at lower rates, digital inputs and outputs, the analog subsystem to sample analog quantities and the WinUSB code layer as well as the low-level hardware functions.

The important aspect of the Hardware Abstraction is the configuration of the hardware at run-time (opposed to the configuration at compile-time) and the interfacing between the software and hardware components during control operation. Since part of the data for that comes from the model-based code, interfacing functions have been added to connect DAVE-based code to the automatically generated code from model-based development. The relevant files are listed in Section 0.

## 3.2.3 Signals and Parameters

The signals of the R-CPU software are listed in Table 16 for reference. The index of each entry is used to configure the XScope channels, see Section 3.2.1.9

Table 16 Signals of the R-CPU software

| Index | Signal                            | Type   | Description                            |

|-------|-----------------------------------|--------|----------------------------------------|

| 100   | Signals.Status.Command            | uint32 | Command for the main state machine     |

| 101   | Signals.Status.UartCommand        | uint32 | Command for the inter-processor        |

|       | 516 Hats. Status. Saite Sillinana | annesz | communication                          |

| 102   | Signals.Status.UARTPacketTimeout  | bool   | Boolean indicator for a packet timeout |

## User Guide for Ref\_22k\_GPD-INV\_Easy3B Reference design for motor general purpose drives

| Softwa | re structure                          |        |                                                      |

|--------|---------------------------------------|--------|------------------------------------------------------|

| 103    | Signals.Status.UARTErrorCode          | uint32 | Error code: 0: no error. See UARTHighLevelTask.c     |

| 104    | Signals.Status.UARTPacketLengthErrors | uint32 | Counter for packets with wrong or exceeding length   |

| 105    | Signals.Status.UARTPacketENDErrors    | uint32 | Counter for enqueueing errors                        |

| 106    | Signals.Status.CurrentState           | uint32 | Current state of the state machine, see<br>Table 11  |

| 107    | Signals.Status.Prech_stat             | uint32 | Boolean state of the precharge contactor             |

| 108    | Signals.Status.Brake_stat             | uint32 | Boolean state of the activation of the brake chopper |

| 109    | Signals.Status.Output_stat            | uint32 | Not used                                             |

| 110    | Signals.Status.IRQTimeTotal           | float  | Total IRQ calculation time as float in μs            |

| 111    | Signals.Status.IRQTimeBetween         | float  | Time between two consecutive control IRQ calls       |

| 112    | Signals.Status.BrakePWM               | float  | PWM dutycycle for the brake chopper PWM              |

| 113    | Signals.Status.OverVoltage            | bool   | Boolean state of the overvoltage detection           |

| 114    | Signals.Status.RealtimeError          | bool   | Emergency switch-off active (protection)             |

| 115    | Signals.Status.EnablePWM              | bool   | Boolean PWM enable from state machine to IRQ         |

| 116    | Signals.Status.EnableINF              | Bool   | Not used                                             |

| 117    | Signals.Status.SELV_Sync              | Bool   | Boolean state of UART synchronization                |

| 118    | Signals.Status.PARAM_Sync             | Bool   | Boolean state of parameter synchronization           |

| 0      | Signals.Measurement.Iph_U             | float  | Measurement of the phase current U                   |

| 1      | Signals.Measurement.Iph_V             | float  | Measurement of the phase current V                   |

| 2      | Signals.Measurement.Iph_W             | float  | Measurement of the phase current W                   |

| 3      | Signals.Measurement.IDC               | float  | Measurement of DC link current                       |

| 4      | Signals.Measurement.VDC               | float  | Measurement of DC voltage                            |

| 5      | Signals.Measurement.VACR              | float  | Measurement of AC voltage                            |

| 6      | Signals.Measurement.VOUT_U            | float  | Measurement of the phase voltage U                   |

| 7      | Signals.Measurement.VOUT_V            | float  | Measurement of the phase voltage V                   |

| 8      | Signals.Measurement.VOUT_W            | float  | Measurement of the phase voltage W                   |

| 9      | Signals.Measurement.offsetI           | float  | Average offset voltage of the current measurement    |

| 10     | Signals.Measurement.NTC1              | float  | Measurement of temperature of NTC1                   |

## User Guide for Ref\_22k\_GPD-INV\_Easy3B Reference design for motor general purpose drives

#### Software structure

| Softwa | re structure                            |        |                                                      |

|--------|-----------------------------------------|--------|------------------------------------------------------|

| 11     | Signals.Measurement.NTC2                | float  | Measurement of temperature of NTC2                   |

| 12     | Signals.Measurement.NTC3                | float  | Measurement of temperature of NTC3                   |

| 13     | Signals.Measurement.NTC_cool            | float  | Measurement of temperature of NTC_cool               |

| 14     | Signals.Measurement.V15                 | float  | Measurement of the 15 V supply                       |

| 15     | Signals.Measurement.V5                  | float  | Measurement of the 5 V supply                        |

| 16     | Signals.Measurement.NTC_ambient         | float  | Measurement of temperature of NTC_ambient            |

| 17     | Signals.Measurement.NTC_dirty           | float  | Measurement of temperature of NTC_dirty              |

| 18     | Signals.Measurement.NTC_IGBT            | float  | Measurement of temperature of NTC_IGBT               |

| 19     | Signals.Measurement.AINSpare            | float  | Measurement of temperature of AINSpare               |

| 20     | Signals.Measurement.DACSpare            | float  | Measurement of temperature of DACSpare               |

| 21     | Signals.Measurement.Fil_Iph_U           | float  | Median-filtered current of phase U                   |

| 22     | Signals.Measurement.Fil_Iph_V           | float  | Median-filtered current of phase V                   |

| 23     | Signals.Measurement.Fil_Iph_W           | float  | Median-filtered current of phase U                   |

| 24     | Signals.Measurement.Fil_IDC             | float  | Median-filtered DC current                           |

| 25     | Signals.Measurement.Fil_VDC             | float  | Median-filtered DC voltage                           |

| 26     | Signals.Measurement.Fil_VACR            | float  | Median-filtered AC voltage                           |

| 200    | Signals.Control.Enable                  | bool   | Command for the main state machine                   |

| 201    | Signals.Control.ControlFrequency        | float  | Command for the inter-processor communication        |

| N/A    | Signals.Control.SampleTimeInNanoSeconds | float  | Boolean indicator for a packet timeout               |

| 202    | Signals.Control.Setpoint                | float  | Error code: 0: no error. See UARTHighLevelTask.c     |

| 203    | Signals.Control.CurrentValue            | float  | Counter for packets with wrong or exceeding length   |

| 204    | Signals.Control.AmplitudeClamp          | float  | Counter for enqueueing errors                        |

| 205    | Signals.Control.Amplitude               | float  | Current state of the state machine, see Table 11     |

| 206    | Signals.Control.Angle                   | float  | Boolean state of the precharge contactor             |

| 207    | Signals.Control.svmAmplitude            | uint32 | Boolean state of the activation of the brake chopper |

| 208    | Signals.Control.svmAngle                | uint32 | Not used                                             |

| N/A    | Signals.Control.PARAM_Sync              | bool   | Total IRQ calculation time as float in μs            |

|        |                                         |        |                                                      |

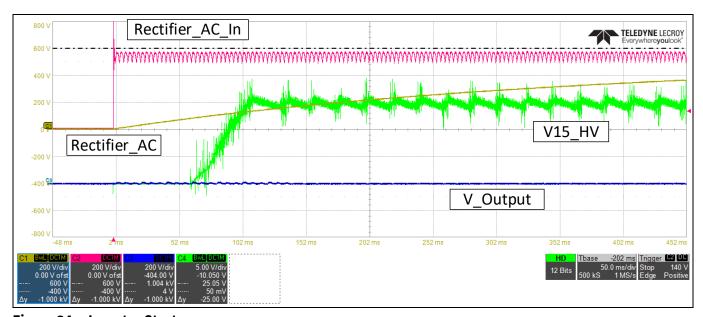

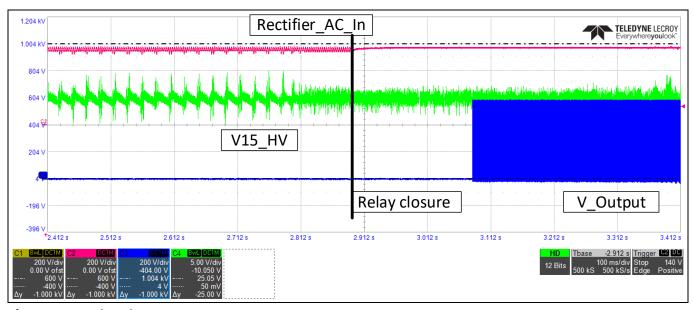

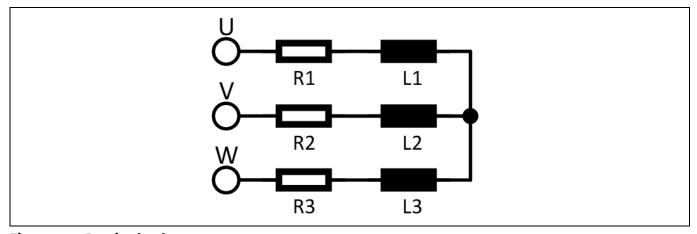

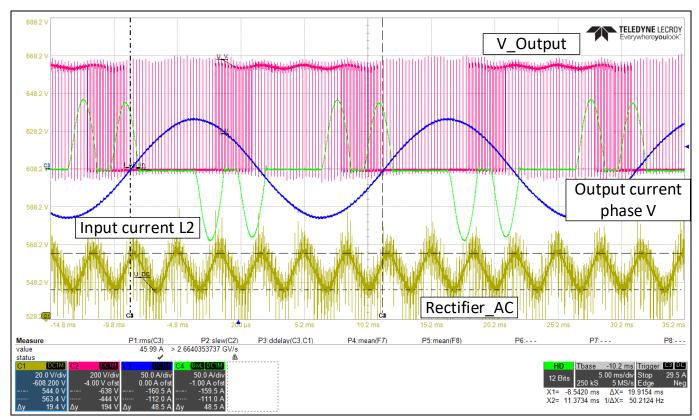

## User Guide for Ref\_22k\_GPD-INV\_Easy3B Reference design for motor general purpose drives