## **Smart Low-Side Power Switch**

## 1 Overview

#### **Features**

- Single channel device

- 3.3V and 5V compatible logic input

- PWM switching capability 20kHz for 10-90% duty cycle

- Electrostatic discharge protection (ESD)

- Adjustable switching speed

- Digital latch feedback signal

- Very low power DMOS leakage current in OFF state

- · DMOS turn on capability in inverse current situation

- Green Product (RoHS compliant)

## **Potential applications**

- Suitable for resistive, inductive and capacitive loads

- Replaces electromechanical relays, fuses and discrete circuits

- Allows high inrush currents and active freewheeling

#### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100/101.

## **Description**

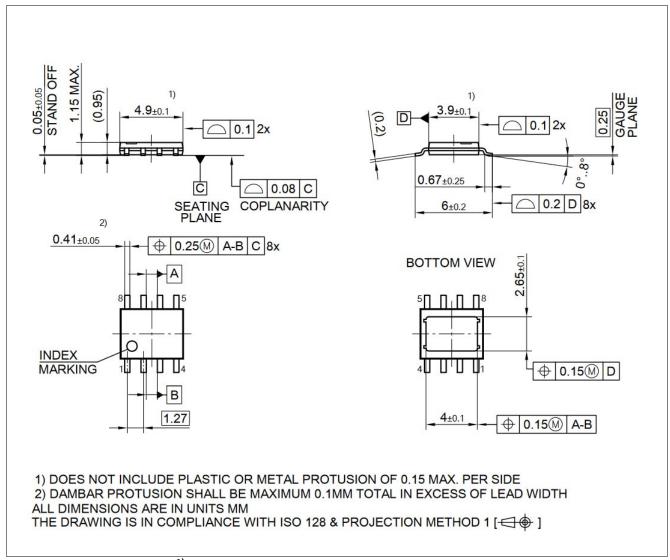

The BTF3035EJ is a 35 m $\Omega$  single channel Smart Low-Side Power Switch with in a PG-TDSO-8-31 package providing embedded protective functions. The power transistor is built by an N-channel vertical power MOSFET.

The device is monolithically integrated. The BTF3035EJ is automotive qualified and is optimized for 12V automotive and industrial applications.

#### Table 1 Product Summary

| Operating voltage range                                                       | $V_{OUT}$           | 3 28 V    |

|-------------------------------------------------------------------------------|---------------------|-----------|

| Maximum battery voltage                                                       | $V_{\rm BAT(LD)}$   | 40 V      |

| Operating supply voltage range                                                | $V_{DD}$            | 3.0 5.5 V |

| Maximum input voltage                                                         | V <sub>IN</sub>     | 5.5 V     |

| Maximum On-State resistance at $T_j = 150$ °C, $V_{DD} = 5$ V, $V_{IN} = 5$ V | R <sub>DS(ON)</sub> | 70 mΩ     |

## **Smart Low-Side Power Switch**

#### **Overview**

## **Table 1** Product Summary (cont'd)

| Nominal load current                                          | I <sub>L(NOM)</sub>        | 5 A    |

|---------------------------------------------------------------|----------------------------|--------|

| Minimum current limitation                                    | I <sub>L(LIM)</sub>        | 14 A   |

| Minimum current limitation trigger level                      | I <sub>L(LIM)TRIGGER</sub> | 41 A   |

| Maximum OFF state load current at T <sub>J</sub> ≤ 85°C       | $I_{L(OFF)}$               | 4.5 μΑ |

| Maximum stand-by supply current at $T_J = 25^{\circ}\text{C}$ | I <sub>DD(OFF)</sub>       | 6 μΑ   |

| Туре      | Package      | Marking |

|-----------|--------------|---------|

| BTF3035EJ | PG-TDSO-8-31 | F3035EJ |

## **Diagnostic Functions**

- · Short circuit to battery

- Over temperature shut down

- Stable latching diagnostic signal

#### **Protection Functions**

- Over temperature shutdown with auto-restart

- Active clamp over voltage protection of the output (OUT, cooling tab)

- · Current limitation

- Enhanced short circuit protection

### **Detailed Description**

The device is able to switch all kind of resistive, inductive and capacitive loads, limited by maximum clamping energy and maximum current capabilities.

The BTF3035EJ offers dedicated ESD protection on the IN, V<sub>DD</sub>, ENABLE, STATUS and SRP pin which refers to the GND ground pin, as well as an over voltage clamping of the OUT to Source/GND.

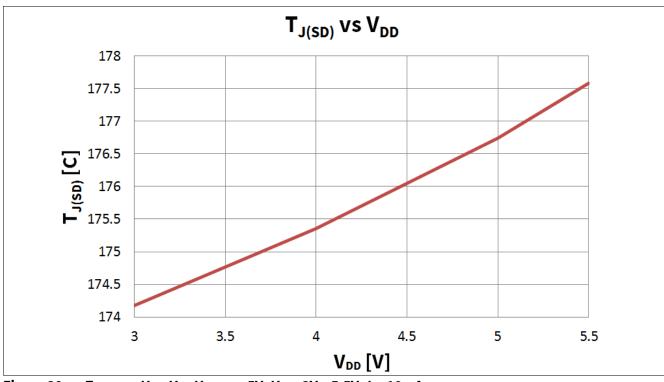

The over voltage protection gets activated during inductive turn off conditions or other over voltage events (like load dump). The power MOSFET is limiting the drain-source voltage, if it rises above the  $V_{\text{OUT}(CLAMP)}$ .

The over temperature protection prevents the device from overheating due to overload and/or bad cooling conditions.

The BTF3035EJ has an auto-restart thermal shutdown function. The device will turn on again, if input is still high, after the measured temperature has dropped below the thermal hysteresis.

## **Smart Low-Side Power Switch**

# **Table of Contents**

| 1                                                                                                              | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                | Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2                                                                                                              | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.1<br>3.2<br>3.3                                                                                              | Pin Assignment          Pin Configuration          Pin Definitions and Functions          Voltage and Current Definition                                                                                                                                                                                                                                                                                                                         | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4                                                                                                              | General Product Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2                                                                            | Absolute Maximum Ratings Functional Range Thermal Resistance PCB set up Transient Thermal Impedance                                                                                                                                                                                                                                                                                                                                              | . 10<br>. 11<br>. 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5                                                                                                              | Power Stage                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.5.1<br>5.5.2<br>5.6<br>5.7<br>5.8<br><b>6</b><br>6.1<br>6.2<br>6.3<br>6.4 | Output On-state Resistance Functional description of ENABLE pin Functional description of IN pin Resistive Load Output Timing Inductive Load Output Clamping Maximum Load Inductance Adjustable Switching Speed / Slew Rate Inverse Current Capability Characteristics  Protection Functions Over Voltage Clamping on OUT Over Temperature Protection with Latched Fault Signal Overcurrent Limitation / Short Circuit Behavior Reset conditions | . 15 16 16 17 18 19 20 20 21 21 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22 22. |

| <b>7</b><br>7.1<br>7.2                                                                                         | Diagnostics          Functional Description of the STATUS pin          Characteristics                                                                                                                                                                                                                                                                                                                                                           | . 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5                                                                           | Supply and Input Stage Supply Circuit Undervoltage Shutdown Input/Enable Circuit Functional Description of the SRP Pin Characteristics                                                                                                                                                                                                                                                                                                           | . 27<br>. 27<br>. 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9<br>9.1<br>9.2<br>9.3<br>9.4                                                                                  | Electrical Characteristics  Power Stage  Protection  Diagnostics  Supply and Input Stage                                                                                                                                                                                                                                                                                                                                                         | . 30<br>. 32<br>. 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## **Smart Low-Side Power Switch**

| 37 |

|----|

| 49 |

| 51 |

| 52 |

| JZ |

| 52 |

|    |

| 55 |

| •  |

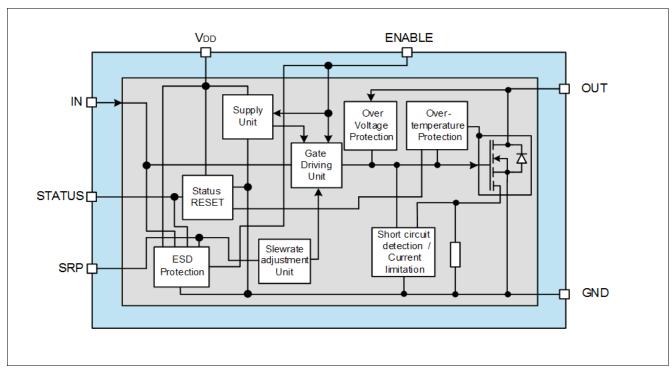

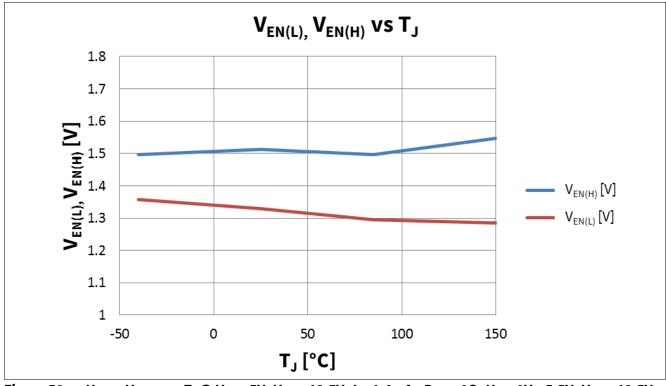

**Block Diagram**

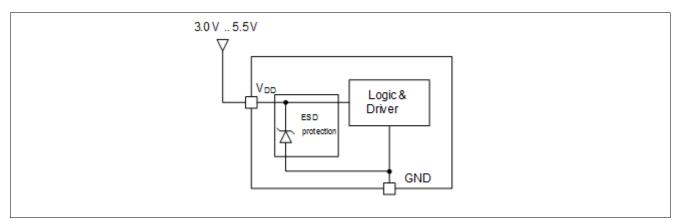

# 2 Block Diagram

Figure 1 Block Diagram

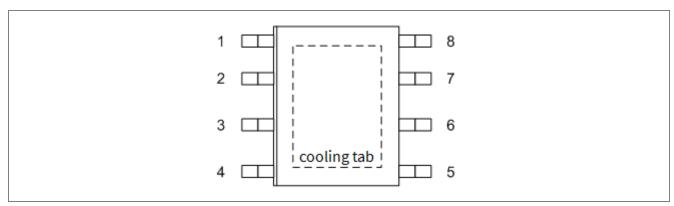

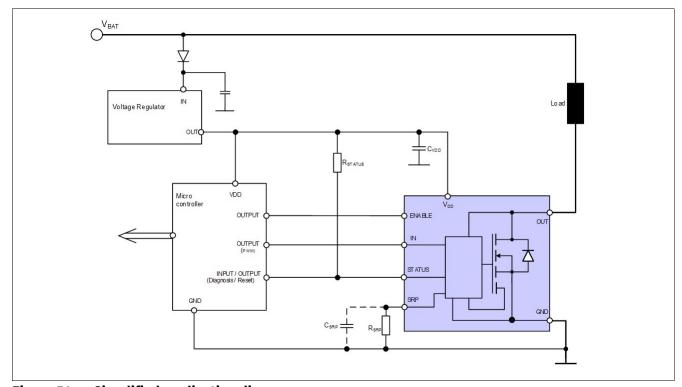

**Pin Assignment**

# 3 Pin Assignment

# 3.1 Pin Configuration

Figure 2 Pin configuration

## 3.2 Pin Definitions and Functions

| Pin         | Symbol   | I/O    | Function                                                            |

|-------------|----------|--------|---------------------------------------------------------------------|

| 1           | IN       | Input  | If IN logic is high, switches ON the Power DMOS                     |

|             |          |        | If IN logic is low, switches OFF the Power DMOS                     |

|             |          |        | only if pin ENABLE is logic high                                    |

| 2           | $V_{DD}$ | Input  | Logic supply voltage, 3V to 5.5V                                    |

| 3           | STATUS   | Input  | Reset of latches by microcontroller pull-up                         |

|             |          | Output | If STATUS logic is high, device is under normal operation           |

|             |          |        | If STATUS logic is low, device is in over temperature condition     |

| 4           | SRP      | Input  | Slewrate control with external resistor                             |

| 5           | ENABLE   | Input  | If ENABLE logic is high, IN pin is enabled                          |

|             |          |        | If ENABLE logic is low, IN pin is disabled and leakages are minimum |

| 6,7,8       | GND      | I/O    | SOURCE of power DMOS and Logic, GND pins must be connected          |

|             |          |        | together                                                            |

| Cooling tab | OUT      | I/O    | DRAIN of power DMOS. Connected to Load.                             |

**Pin Assignment**

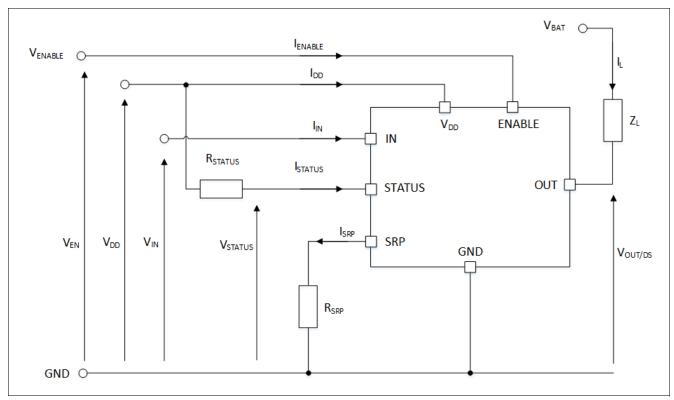

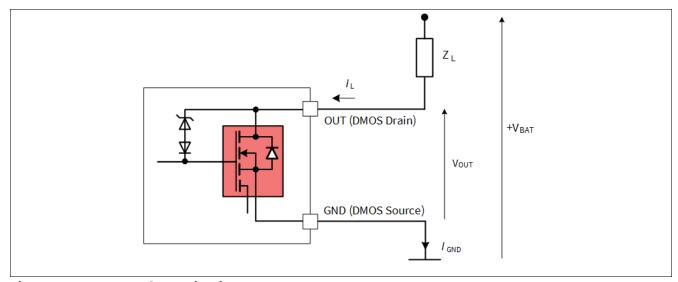

# 3.3 Voltage and Current Definition

Figure 3 shows all external terms used in this data sheet, with associated convention for positive values.

Figure 3 Naming Definition of electrical parameters

# infineon

#### **General Product Characteristics**

## 4 General Product Characteristics

## 4.1 Absolute Maximum Ratings

# Table 2 Absolute Maximum Ratings<sup>1)</sup>

$T_J$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                                                      | Symbol               | Values |      |                     | Unit | <b>Note or Test Condition</b>                                                                                                                                                                                                                  | Number   |  |

|------------------------------------------------------------------------------------------------|----------------------|--------|------|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

|                                                                                                |                      | Min.   | Тур. | Max.                |      |                                                                                                                                                                                                                                                |          |  |

| Voltages                                                                                       |                      |        |      |                     |      |                                                                                                                                                                                                                                                |          |  |

| Supply voltage                                                                                 | $V_{DD}$             | -0.3   | _    | 5.5                 | V    |                                                                                                                                                                                                                                                | P_4.1.1  |  |

| Output voltage                                                                                 | V <sub>OUT</sub>     | _      | _    | 40                  | ٧    |                                                                                                                                                                                                                                                | P_4.1.2  |  |

| Battery voltage for short circuit protection                                                   | V <sub>BAT(SC)</sub> | -      | _    | 31                  | V    | $^{1)}l = 0$ or 5m<br>$R_{SC} = 30 \text{ m}\Omega + R_{Cable}$<br>$R_{Cable} = l * 16 \text{ m}\Omega/\text{m}$<br>$L_{SC} = 5 \text{ \muH} + L_{Cable}$<br>$L_{Cable} = l * 1 \text{ \muH/m V}_{DD} = 5V;$<br>$V_{IN} = 5V; V_{ENABLE} = 5V$ | P_4.1.3  |  |

| Battery voltage for load dump protection $(V_{BAT(LD)} = V_A + V_S \text{ with } V_A = 13.5V)$ | V <sub>BAT(LD)</sub> | _      | -    | 40                  | V    | $^{2)}R_{i} = 2 \Omega$ , $R_{L} = 2.2\Omega$ , $t_{d} = 400 \text{ ms}$ , suppressed pulse                                                                                                                                                    | P_4.1.4  |  |

| Control pins voltages                                                                          |                      |        |      |                     |      |                                                                                                                                                                                                                                                |          |  |

| Input Voltage                                                                                  | $V_{\rm IN}$         | -0.3   | _    | 5.5                 | V    | -                                                                                                                                                                                                                                              | P_4.1.8  |  |

| SRP pin Voltage                                                                                | $V_{SRP}$            | -0.3   | _    | 5.5                 | ٧    | $V_{\rm SRP} \leq V_{\rm DD}$                                                                                                                                                                                                                  | P_4.1.9  |  |

| STATUS pin Voltage                                                                             | V <sub>STATUS</sub>  | -0.3   | -    | 5.5                 | V    |                                                                                                                                                                                                                                                | P_4.1.10 |  |

| ENABLE pin Voltage                                                                             | $V_{ENABLE}$         | -0.3   | _    | 5.5                 | ٧    |                                                                                                                                                                                                                                                | P_4.1.11 |  |

| Power Stage                                                                                    |                      |        |      |                     |      |                                                                                                                                                                                                                                                |          |  |

| Load current                                                                                   | / <sub>L</sub>       | _      | -    | I <sub>L(LIM)</sub> |      | T <sub>J</sub> < 150°C                                                                                                                                                                                                                         | P_4.1.12 |  |

| Power Dissipation                                                                              | $P_{TOT}$            | -      | -    | 1.75                | W    | DC operation, $T_A = 85^{\circ}\text{C}$ , $T_J < 150^{\circ}\text{C}$ , $I_L = I_{NOM}$                                                                                                                                                       | P_4.1.48 |  |

| Energies                                                                                       |                      |        |      |                     |      |                                                                                                                                                                                                                                                |          |  |

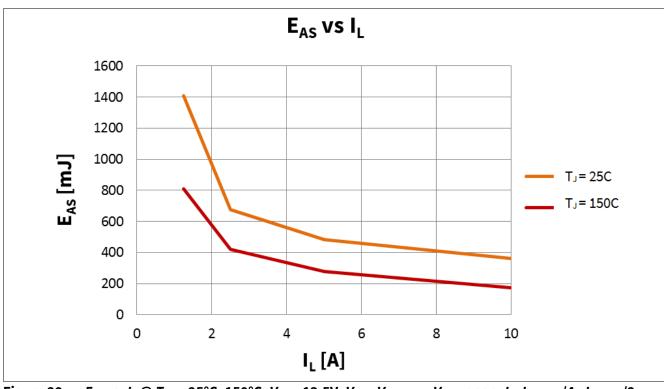

| Unclamped single inductive energy single pulse                                                 | E <sub>AS</sub>      | _      | _    | 138                 | mJ   | $I_{L(0)} = I_{L(NOM)}$<br>$V_{BAT} = 13.5 \text{ V}$<br>$T_{J(0)} = 150^{\circ}\text{C}$                                                                                                                                                      | P_4.1.17 |  |

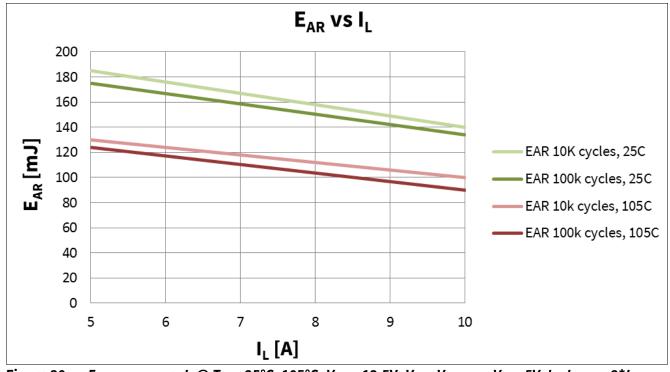

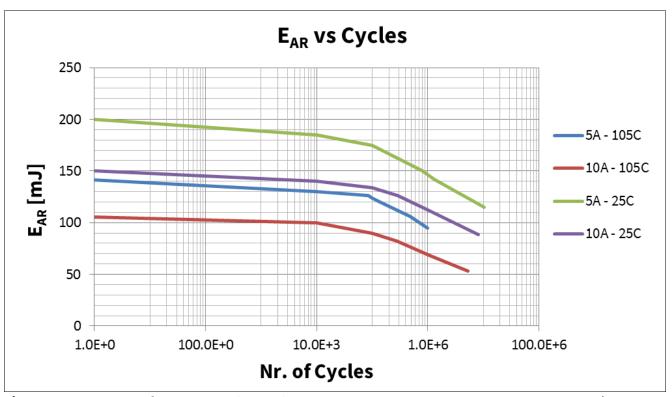

| Unclamped repetitive inductive energy pulse with 10k cycles                                    | E <sub>AR(10k)</sub> | _      | _    | 130                 | mJ   | $I_{L(0)} = I_{L(NOM)}$<br>$V_{BAT} = 13.5 \text{ V}$<br>$T_{J(0)} = 85 \text{ °C}$                                                                                                                                                            | P_4.1.27 |  |

#### **Smart Low-Side Power Switch**

#### **General Product Characteristics**

## Table 2 Absolute Maximum Ratings<sup>1)</sup> (cont'd)

$T_J$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                    | Symbol                | Values |      |      | Unit | Note or Test Condition                                                              | Number   |  |

|--------------------------------------------------------------|-----------------------|--------|------|------|------|-------------------------------------------------------------------------------------|----------|--|

|                                                              |                       | Min.   | Тур. | Max. |      |                                                                                     |          |  |

| Unclamped repetitive inductive energy pulse with 100k cycles | E <sub>AR(100k)</sub> | _      | _    | 124  | mJ   | $I_{L(0)} = I_{L(NOM)}$<br>$V_{BAT} = 13.5 \text{ V}$<br>$T_{j(0)} = 85 \text{ °C}$ | P_4.1.32 |  |

| Temperatures                                                 | ,                     |        |      | •    |      |                                                                                     | <u> </u> |  |

| Operating temperature                                        | $T_{i}$               | -40    | -    | +150 | °C   | _                                                                                   | P_4.1.39 |  |

| Storage temperature                                          | $T_{\rm stg}$         | -55    | -    | +150 | °C   | -                                                                                   |          |  |

| ESD robustness                                               | , ,                   |        |      | •    |      |                                                                                     |          |  |

| ESD robustness (all pins)                                    | $V_{ESD}$             | -2     | _    | 2    | kV   | HBM <sup>3)</sup>                                                                   | P_4.1.41 |  |

| ESD robustness OUT pin vs. GND                               | $V_{ESD}$             | -4     | _    | 4    | kV   | HBM <sup>3)</sup>                                                                   | P_4.1.42 |  |

| ESD robustness                                               | $V_{ESD}$             | -500   | _    | 500  | ٧    | CDM <sup>4)</sup>                                                                   | P_4.1.43 |  |

| ESD robustness corner pins                                   | $V_{ESD}$             | -750   | _    | 750  | ٧    | CDM <sup>5)</sup>                                                                   | P_4.1.44 |  |

- 1) Not subject to production test, specified by design.

- 2)  $V_{\text{BAT(LD)}}$  is setup without the DUT connected to the generator per ISO7637-1;  $R_{\text{i}}$  is the internal resistance of the load dump test pulse generator;  $t_{\text{d}}$  is the pulse duration time for load dump pulse (pulse 5) according ISO 7637-1, -2.

- 3) ESD robustness, HBM according to ANSI/ESDA/JEDEC JS-001 (1.5 k $\Omega$ , 100 pF)

- 4) ESD robustness, Charged Device Model "CDM" ESDA STM5.3.1 or JESD22-C101

- 5) ESD robustness, Charged Device Model "CDM" ESDA STM5.3.1 or JESD22-C101

#### Note:

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation

## **Smart Low-Side Power Switch**

#### **General Product Characteristics**

## 4.2 Functional Range

Table 3 Functional Range

| Parameter                                      | Symbol                     |      | Value | S    | Unit | Note or                                                                                                                         | Number   |  |

|------------------------------------------------|----------------------------|------|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------|----------|--|

|                                                |                            | Min. | Тур.  | Max. |      | Test Condition                                                                                                                  |          |  |

| Supply Voltage Range for<br>Nominal Operation  | $V_{\rm DD(NOR)}$          | 3.0  | 5.0   | 5.5  | V    |                                                                                                                                 | P_4.2.1  |  |

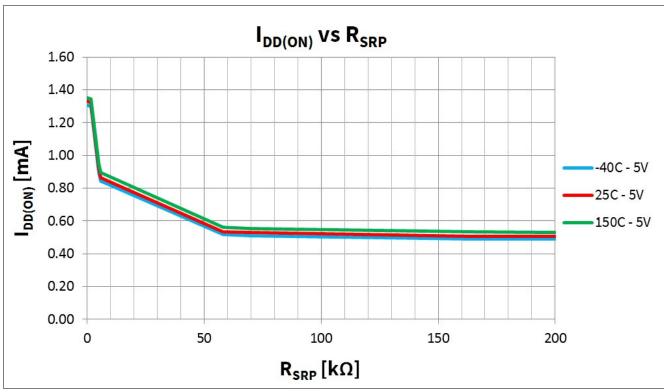

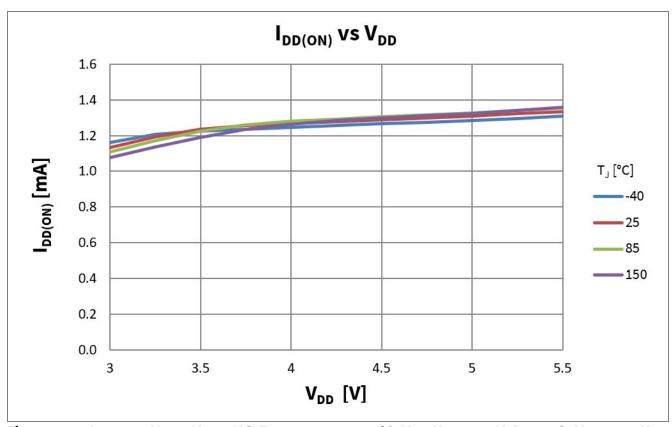

| Supply current continuous ON operation         | $I_{\rm DD(ON)}$           | -    | 1.3   | 2.5  | mA   | Supply current continuous ON operation is specified for R <sub>SRP</sub> =0. It is lower (0.7mA typ) for R <sub>SRP</sub> =5.8k | P_4.2.5  |  |

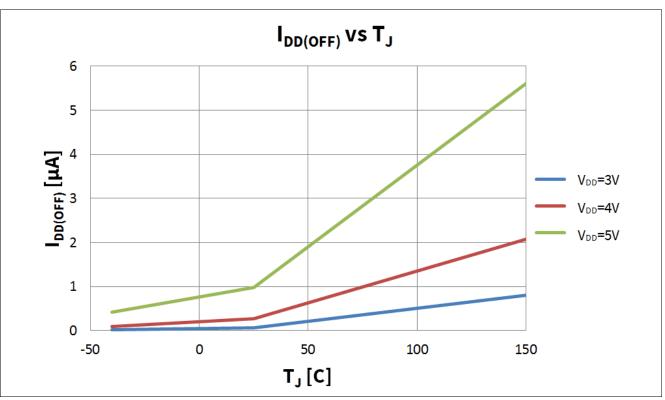

| Standby supply current<br>(ambient)            | I <sub>DD(OFF)</sub>       | -    | 1.5   | 6    | μΑ   | T <sub>J</sub> = 25°C                                                                                                           | P_4.2.8  |  |

| Maximum standby supply current (hot)           | I <sub>DD(OFF)_150</sub>   | -    | 6     | 14   | μΑ   | T <sub>J</sub> = 150°C                                                                                                          | P_4.2.9  |  |

| Battery Voltage Range for<br>Nominal Operation | $V_{\rm BAT(NOR)}$         | 6    | 13.5  | 18   | V    | 1)                                                                                                                              | P_4.2.10 |  |

| Extended Battery Voltage Range for Operation   | $V_{BAT(EXT)}$             | 0    | _     | 29   | V    | parameter deviations possible                                                                                                   | P_4.2.11 |  |

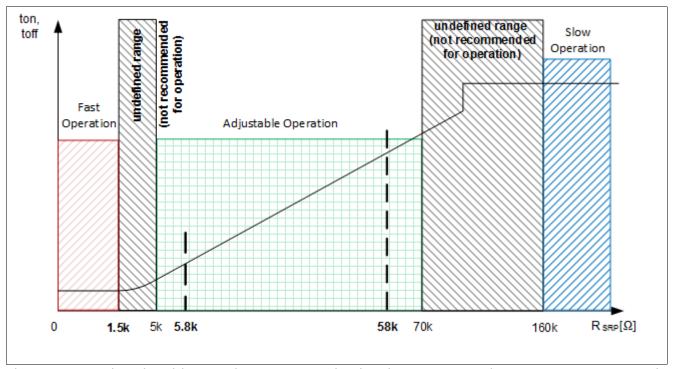

| SRP pin resistor for adjustable operation      | R <sub>SRP(NOR)</sub>      | 5    | _     | 70   | kΩ   | refer to graphic Figure 16 1)                                                                                                   | P_4.2.12 |  |

| SRP pin resistor for fast operation            | R <sub>SRP(EXTF)</sub>     | 0    | _     | 1.5  | kΩ   | 1)                                                                                                                              | P_4.2.13 |  |

| SRP pin resistor for slow operation            | R <sub>SRP(EXTS)</sub>     | >160 | -     | -    | kΩ   | Pin can be left open                                                                                                            | P_4.2.14 |  |

| DIAGNOSIS                                      | •                          | •    |       |      | •    | •                                                                                                                               | •        |  |

| STATUS Pin voltage operation range             | V <sub>STATUS</sub>        | -0.3 | _     | 5.5  | V    | normal and reset<br>mode                                                                                                        | P_4.2.15 |  |

| STATUS Pin Leakage current                     | I <sub>STATUS</sub>        | -    | 1.5   | 12   | μΑ   | $V_{\text{STATUS}} \leq 5V$                                                                                                     | P_4.2.17 |  |

| STATUS Pin voltage drop Fault                  | V <sub>STATUS(FAULT)</sub> |      | 0.5   | 0.8  | ٧    | I <sub>STATUS(FAULT)</sub> =1mA                                                                                                 | P_4.2.18 |  |

| STATUS Current Reset                           | I <sub>STATUS(RESET)</sub> | 5    | _     | 7    | mA   |                                                                                                                                 | P_4.2.19 |  |

Note:

Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

## **Smart Low-Side Power Switch**

#### **General Product Characteristics**

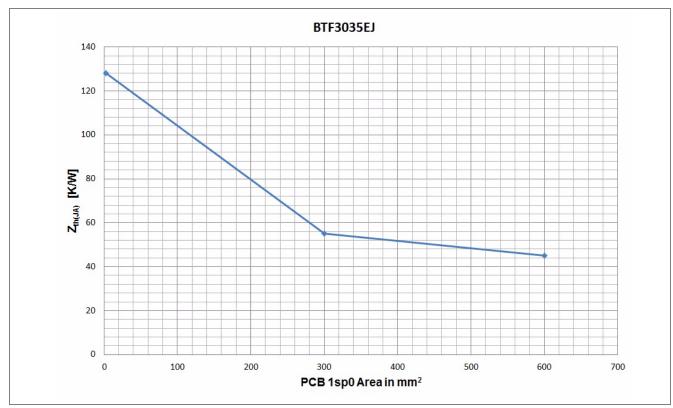

### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards.

For more information, go to www.jedec.org.

Table 4  $T_J = -40^{\circ}\text{C to} + 150^{\circ}\text{CV}_{DD} = 3.0 \text{ V to} 5.5 \text{ VV}_{BAT} = 6 \text{ V to} 18 \text{ Vall voltages with respect to ground,}$ positive current flowing into pin (unless otherwise specified)

| Parameter                            | Symbol                  | Values |      |      | Unit | Note or               | Number   |

|--------------------------------------|-------------------------|--------|------|------|------|-----------------------|----------|

|                                      |                         | Min.   | Тур. | Max. |      | <b>Test Condition</b> |          |

| Junction to Case                     | $R_{thJC}$              | -      | 2    | -    | K/W  | 1) 2)                 | P_4.3.4  |

| Junction to Ambient (2s2p)           | R <sub>thJA(2s2p)</sub> | _      | 34   | _    | K/W  | 1) 3)                 | P_4.3.10 |

| Junction to Ambient (1s0p+600mm² Cu) | R <sub>thJA(1s0p)</sub> | -      | 45   | _    | K/W  | 1) 4)                 | P_4.3.15 |

- 1) Not subject to production test, specified by design

- 2) Specified  $R_{thJC}$  value is simulated at natural convection on a cold plate setup (bottom of package is fixed to ambient temperature).

- $T_c = 85$ °C. Device is loaded with 1W power.

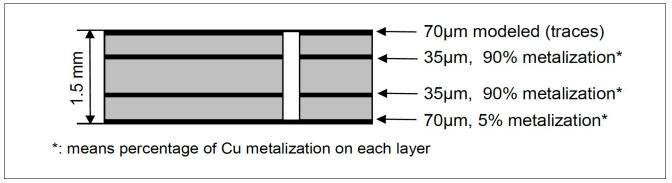

- 3) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 $\mu$ m Cu, 2 x 35 $\mu$ m Cu). Where applicable a thermal via array under the ex posed pad contacted the first inner copper layer.  $T_a$  = 85°C, Device is loaded with 1W power.

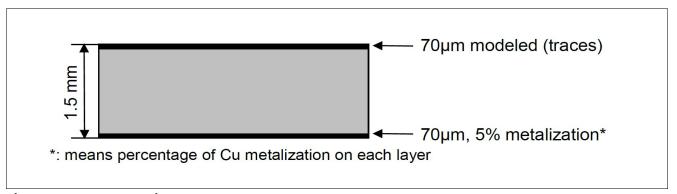

- 4) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 1s0p board; The product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with additional heatspreading copper area of 600mm<sup>2</sup> and 70 mm thickness.  $T_a$  = 85°C, Device is loaded with 1W power.

#### **General Product Characteristics**

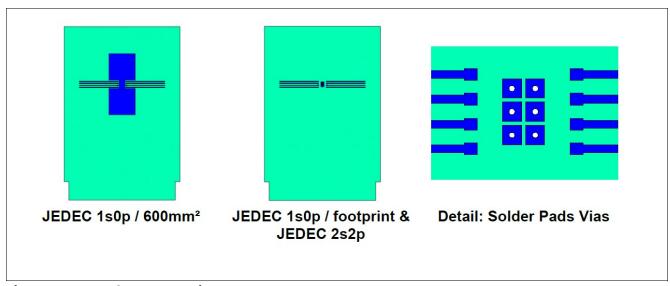

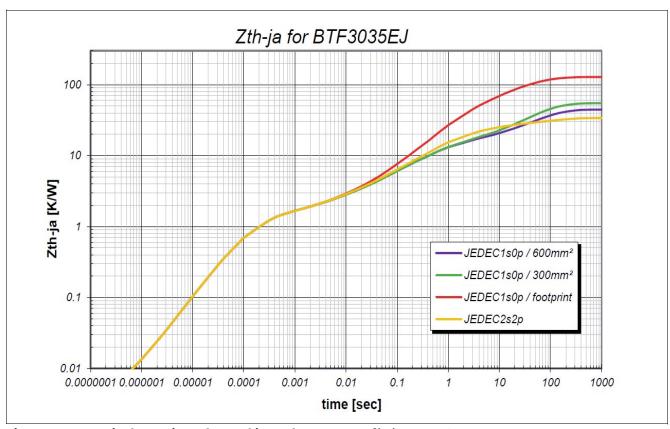

## **4.3.1** PCB set up

The following PCB setup was implemented to determine the transient thermal impedance. The setup is according to JEDEC standard JESD51-2A and related.

Figure 4 Cross-section JEDEC2s2p

Figure 5 Cross-section JEDEC1s0p

Figure 6 PCB layout, top view

# **(infineon**

**General Product Characteristics**

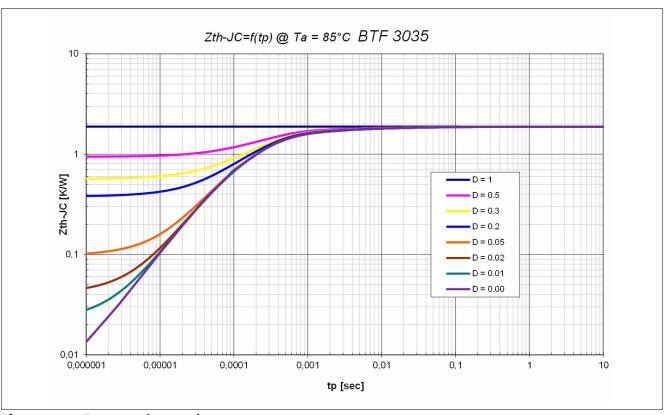

## 4.3.2 Transient Thermal Impedance

Figure 7 Typical transient thermal impedance  $Z_{\rm thJA} = f(t_{\rm p})$ ,  $T_{\rm a} = 85\,^{\circ}{\rm C}$  Value is according to Jedec JESD51-2,-7 at natural convection on FR4 boards; The product (Chip+Package) was simulated with the respective PCB setups, according to the JEDEC standard. Where applicable a thermal via array under the ex posed pad contacted the first inner copper layer. Device is dissipating 1 W power.

# **(infineon**

## **General Product Characteristics**

Figure 8 Z<sub>th(JC)</sub> vs. duty cycle

Figure 9 PCB 1sp0 - R<sub>thja</sub> vs. cooling areas

# **(infineon**

**Power Stage**

## 5 Power Stage

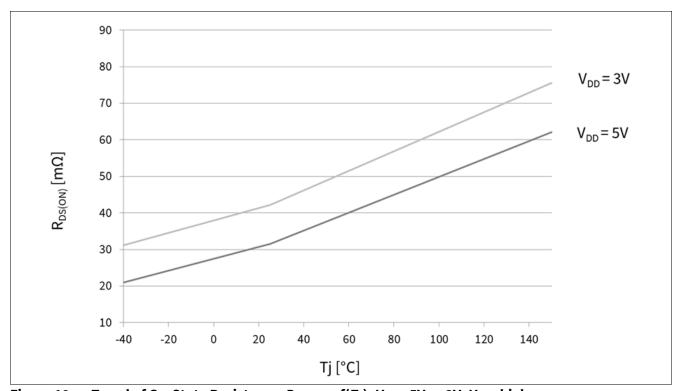

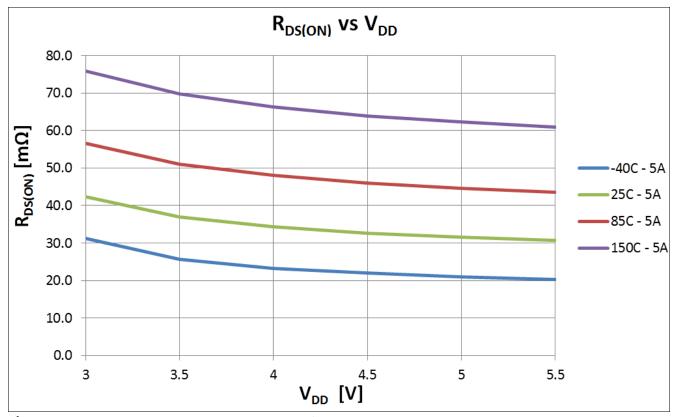

## 5.1 Output On-state Resistance

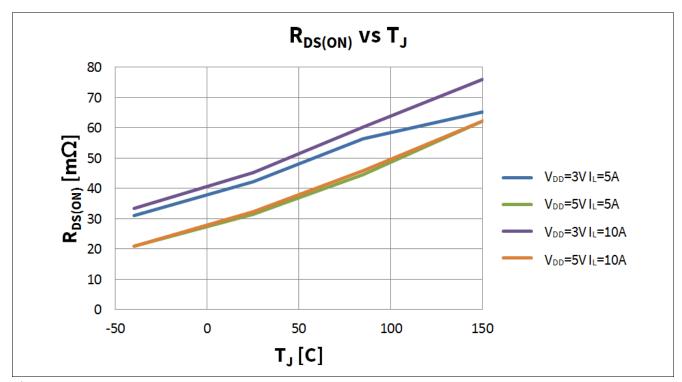

The on-state resistance depends on the supply voltage and on the junction temperature  $T_J$ . **Figure 10** shows this dependencies in terms of temperature and voltage for the typical on-state resistance  $R_{\rm DS(ON)}$ . The behavior in reverse polarity is described in chapter "Inverse Current Capability" on Page 20.

Figure 10 Trend of On-State Resistance  $R_{DS(ON)} = f(T_J)$ ,  $V_{DD} = 5V$  or 3V,  $V_{IN} = high$

At  $V_{IN}$  = high the power DMOS switches ON with a dedicated slope.

To achieve a reasonable  $R_{\rm DS(ON)}$  and the specified switching speed a 5V supply is required.

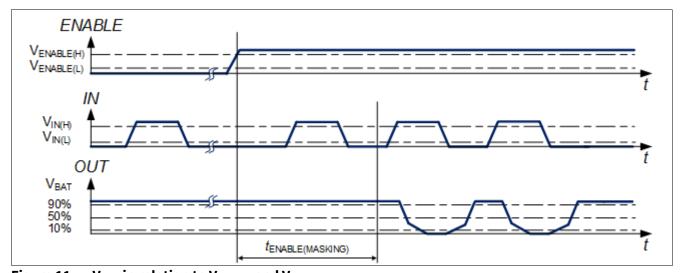

## 5.2 Functional description of ENABLE pin

The physical digital input ENABLE allows power down mode when IN pin toggling is not needed.

When ENABLE is set to logic low, the DMOS is switched off (regardless of the status of the input IN) and the device will be in Power Down mode. It allows the lowest possible leakage current through OUT and  $V_{DD}$  pins.

The STATUS pin will not be available during this stage and the device is reset.

When the ENABLE pin is switched to logic high, the device logic and DMOS are available with full functionalities, after a dead time defined as masking time -  $t_{\text{ENABLE}(\text{MASKING})}$ "(Table "tENABLE(MASKING)" on Page 36), .

Then, depending on the status of the IN pin the DMOS is switched on or off, see **Chapter 5.3** and **Figure 11 "VOUT in relation to VENABLE and VIN" on Page 16**. The STATUS pin will also be available. For the electrical characteristics see **Table 8**, **Page 35**.

# infineon

## **Power Stage**

## 5.3 Functional description of IN pin

The IN pin is a digital input. As described in **Chapter 5.2** using the physical IN pin requires the ENABLE pin to be set to logic high.

If IN is set to logic low, the DMOS is switched off.

If IN is set to logic high, the DMOS is switched on.

In addition, an high frequency PWM signal source can be connected. At a frequency of 20kHz the duty cycle can be selected between 10% and 90%. .

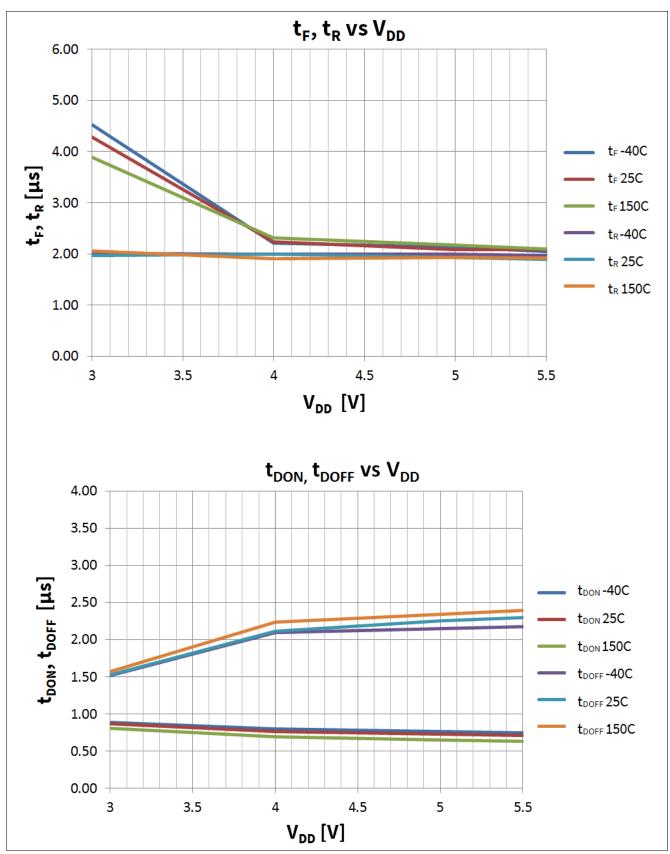

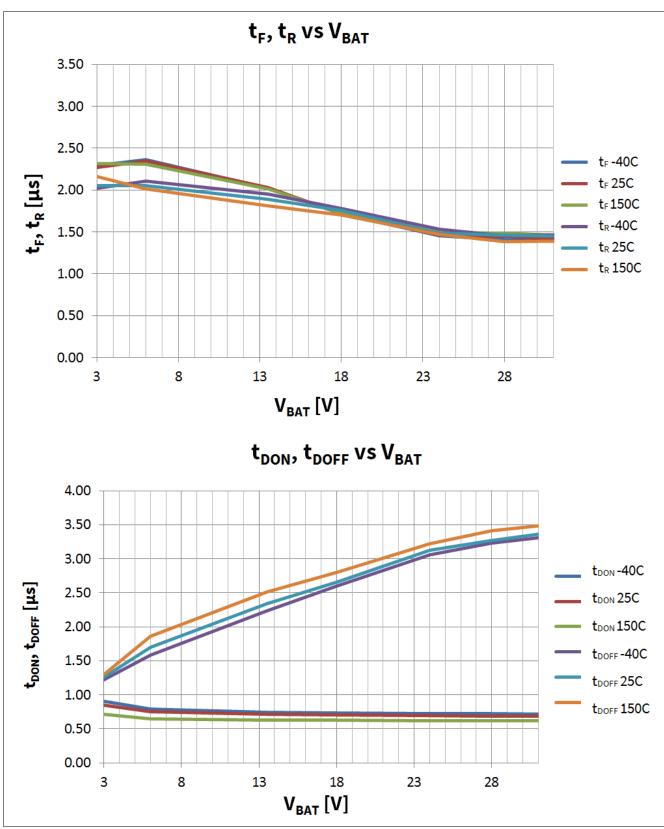

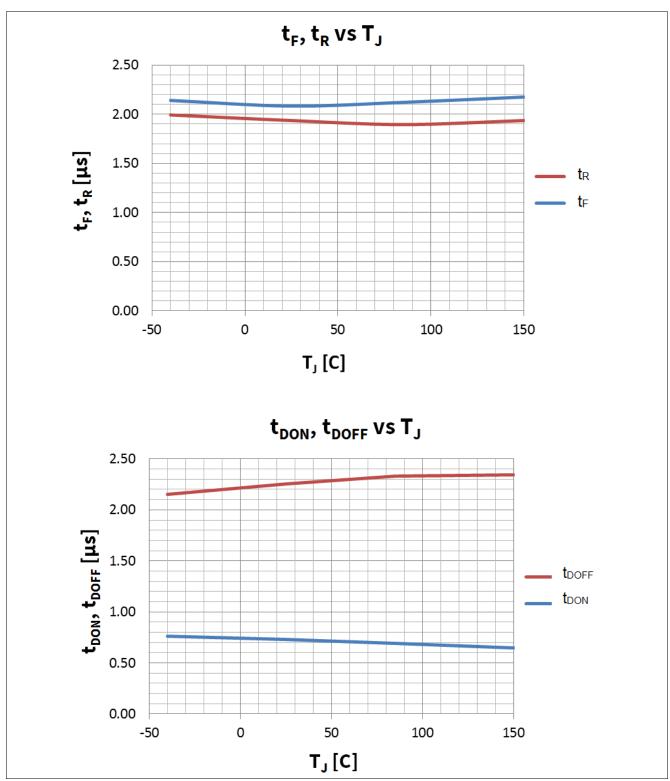

## 5.4 Resistive Load Output Timing

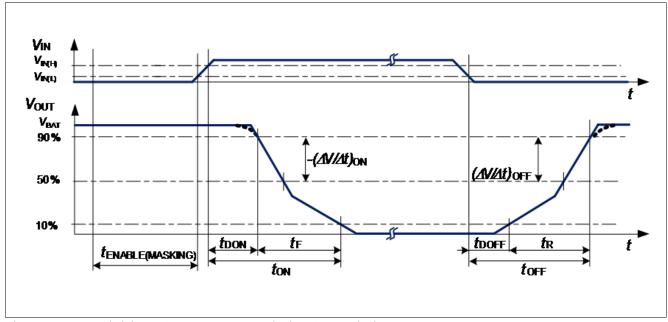

Figure 12 shows the typical timing when switching a resistive load.

Figure 11  $V_{OUT}$  in relation to  $V_{ENABLE}$  and  $V_{IN}$

Figure 12 Definition of Power Output Timing for Resistive Load

**Power Stage**

## 5.5 Inductive Load

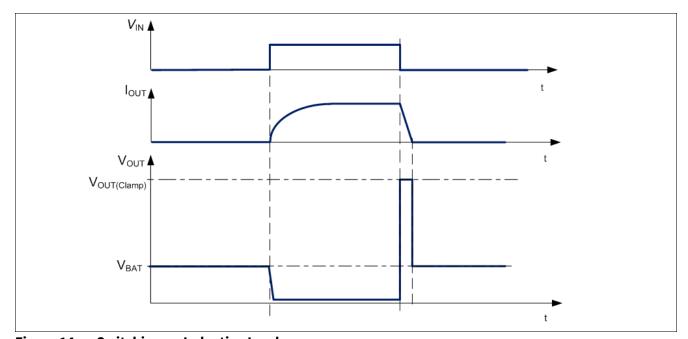

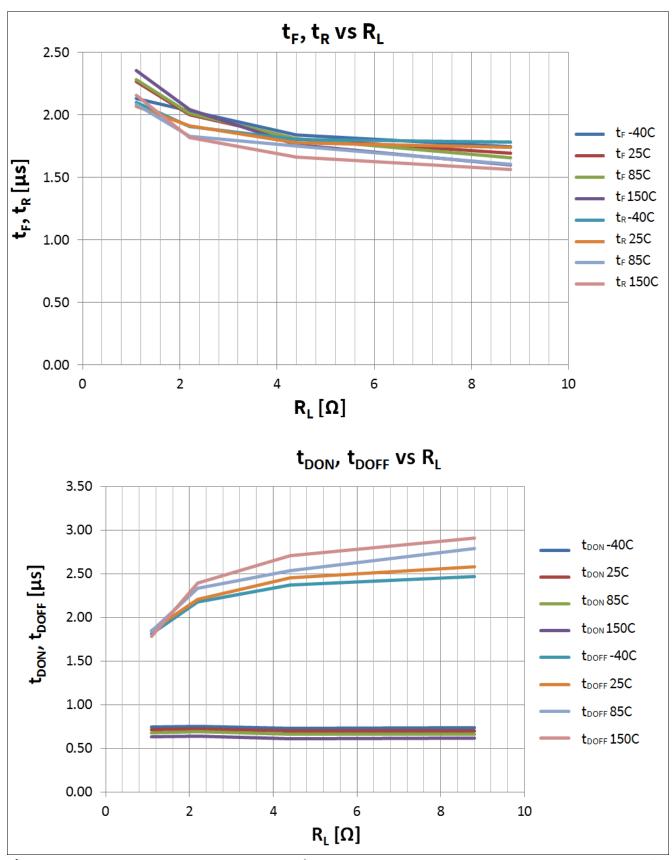

## 5.5.1 Output Clamping

When switching off inductive loads with low side switches, the drain-source voltage  $V_{\rm OUT}$  rises above battery potential, because the inductance intends to continue driving the current. To prevent unwanted high voltages the device has a voltage clamping mechanism to keep the voltage at  $V_{\rm OUT(CLAMP)}$ . During this clamping operation mode the device heats up as it dissipates the energy from the inductance. Therefore the maximum allowed load inductance is limited. See **Figure 13** and **Figure 14** for more details.

Figure 13 Output Clamp Circuitry

Figure 14 Switching an Inductive Load

Note: Repetitive switching of inductive load by VDD instead of using the input is a not recommended operation and may affect the device reliability and reduce the lifetime.

## **Power Stage**

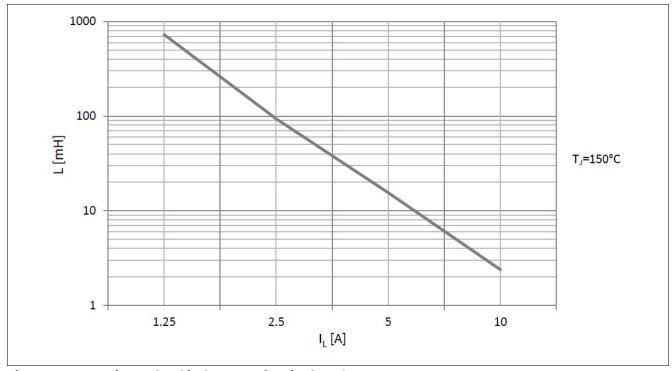

## 5.5.2 Maximum Load Inductance

While demagnetization of inductive loads, energy has to be dissipated in the BTF3035EJ. This energy can be calculated by the following equation:

$$E = V_{OUT(CLAMP)} \times \left[ \frac{V_{BAT} - V_{OUT(CLAMP)}}{R_L} \times \ln \left( 1 - \frac{R_L \times I_L}{V_{BAT} - V_{OUT(CLAMP)}} \right) + I_L \right] \times \frac{L}{R_L}$$

(5.1)

Following equation simplifies under assumption of  $R_L = 0$

$$E = \frac{1}{2}LI_L^2 \times \left(1 - \frac{V_{BAT}}{V_{BAT} - V_{OUT(CLAMP)}}\right)$$

(5.2)

The figure below shows the inductance / current combination the BTF3035EJ can handle. For maximum single avalanche energy refer to EAS value in **Table 2**.

Figure 15 Maximum load inductance for single pulse  $L = f(I_L)$ ,  $T_{J,\text{start}} = 150^{\circ}\text{C}$ ,  $V_{BAT} = 13.5\text{V}$

# infineon

## **Power Stage**

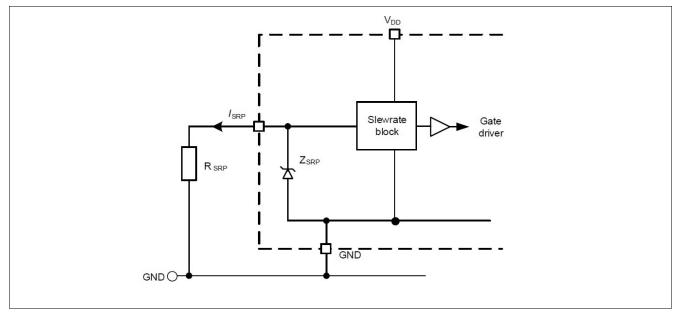

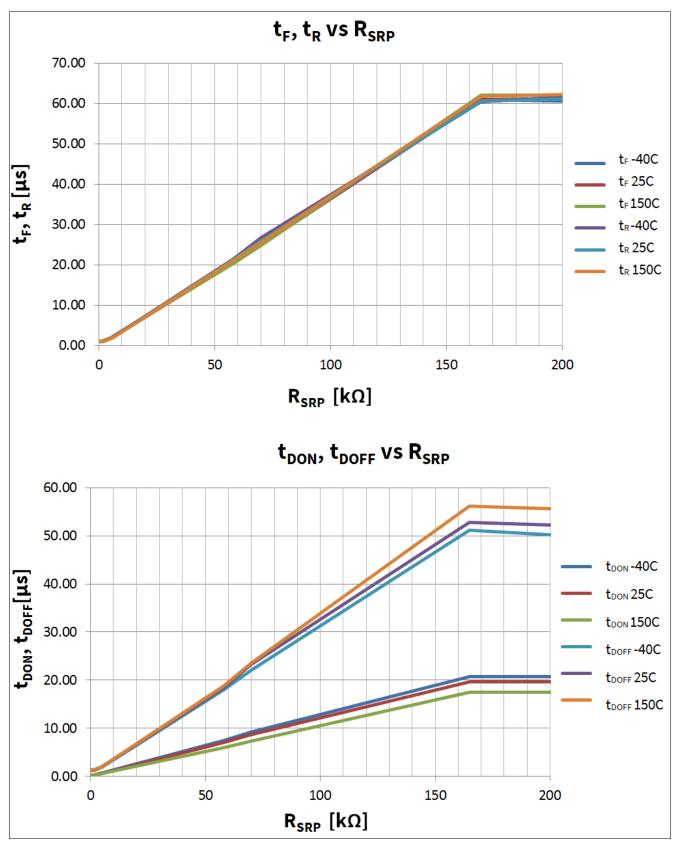

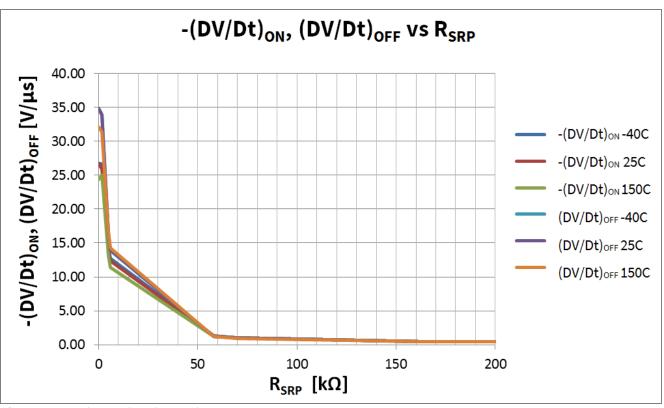

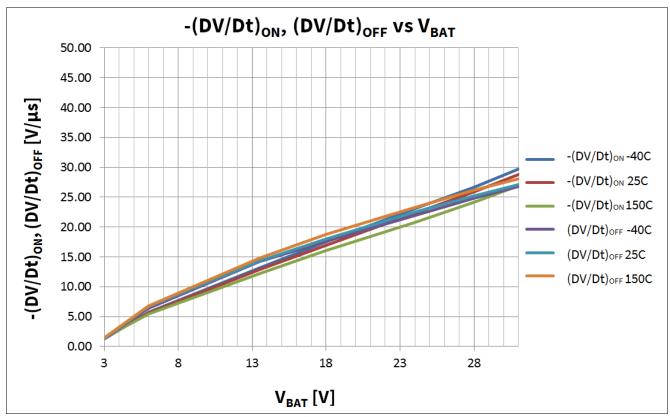

## 5.6 Adjustable Switching Speed / Slew Rate

In order to optimize electromagnetic emission, the switching speed of the MOSFET can be adjusted by connecting an external resistor between SRP pin and GND. This allows for balancing between electromagnetic emissions and power dissipation. Shorting the SRP pin to GND represents the fastest switching speed. Open pin represents the slowest switching speed.

The accuracy of the switching speed adjustment is dependent on the precision of the external resistor used and on the parasitic capacitance on the SRP pin. It is recommended to use accurate resistors and place them as close as possible to the SRP pin with the shortest way possible to the GND of the device.

Figure 16 shows the simplified relation between the resistor value and the switching times

Figure 16 Typical simplified relation between switching time and  $R_{SRP}$  resistor values used on SRP pin

It is not recommended to change the slew rate resistance during switching (supplied device,  $V_{DD} > V_{DD(UV\_ON)}$ . Undefined switching times can result.

If the SRP pin is externally pulled up above the normal SRP pin voltage  $V_{\text{SRP}}$  (e.g. to  $V_{\text{DD}}$ ) the slowest slew rate settings apply.

#### **Smart Low-Side Power Switch**

## **Power Stage**

## 5.7 Inverse Current Capability

An inverse situation means the OUT pin is pulled below GND potential via the load and current flows in the Power DMOS intrinsic body diode.

In certain application cases (for example in use in a bridge or half-bridge configuration) the body diode is used for freewheeling of an inductive load. In this case the device is still supplied but the inverse current is flowing from GND to OUT(drain).

In inverse operation the body diode is dissipating power, which is defined by the driven current times the voltage drop on the body diode -V<sub>DS</sub>.

In order to dissipate less power in inverse situation, a dedicated circuit has been implemented.

The BTF3035EJ includes an inverse current detection circuit that allows to turn ON the Power DMOS while inverse current is present (active freewheeling) and disables all protections, e.g. current limitation, temperature shutdown or over voltage clamping. To do active freewheeling, both ENABLE and IN pin must be set to logic high.

The timings are set to slow mode (open SRP pin), regardless of the SRP pin configuration.

During inverse current condition the quiescent current of the circuit is the same as in normal operation if ENABLE=high (see **Chapter 9.4**). If ENABLE=low and the device is still supplied, the standby supply current in inverse increases compared to standby supply current in normal output current condition (see **Table 8 "Electrical Characteristics: Supply and Input" on Page 35**).

The maximum admissible inverse current is  $-I_{L(NOM)}$ .

## 5.8 Characteristics

See Table 9.1 "Power Stage" on Page 30 for electrical characteristics.

#### **Smart Low-Side Power Switch**

#### **Protection Functions**

## 6 Protection Functions

The device provides embedded protection functions. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operation. Protection functions are not to be used for continuous or repetitive operation. Over temperature is indicated by a low active signal on the STATUS pin.

## 6.1 Over Voltage Clamping on OUT

The BTF3035EJ is equipped with a voltage clamp circuitry that keeps the drain-source voltage  $V_{\rm DS}$  at a certain level  $V_{\rm OUT(CLAMP)}$ . The over voltage clamping is overruling the other protection functions. Power dissipation has to be limited not to exceed the maximum allowed junction temperature.

This function is also used in terms of inductive clamping. See also "Output Clamping" on Page 17 for more details.

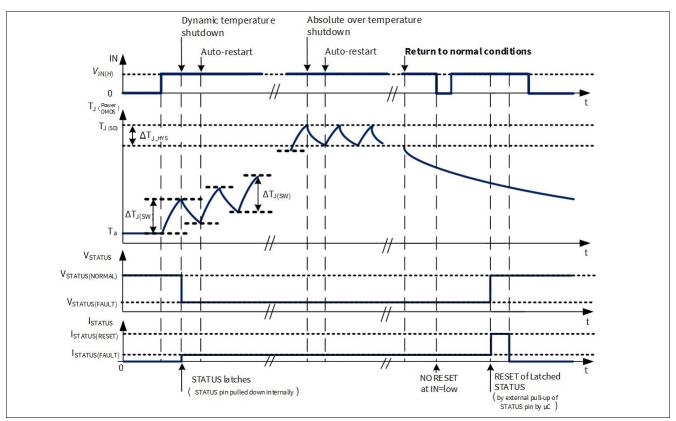

## 6.2 Over Temperature Protection with Latched Fault Signal

The device is protected against over temperature due to overload and/or bad cooling conditions by an integrated temperature sensor. The over temperature protection is available if the device is active, i.e. IN=high and ENABLE=high.

The device incorporates an absolute  $(T_{J(SD)})$  and a dynamic temperature limitation  $(\Delta T_{J(SW)})$ . Triggering one of them will cause the output to switch off. The dynamic temperature limitation principle is developed in a separated Application Note for HITFET+.

The switch off will be done with the fastest possible slew rate. The BTF3035EJ has a thermal-restart function. If IN pin is still high the device will turn on again after the junction temperature has dropped below the thermal hysteresis ( $\Delta T_{\rm J-HYS}$ ).

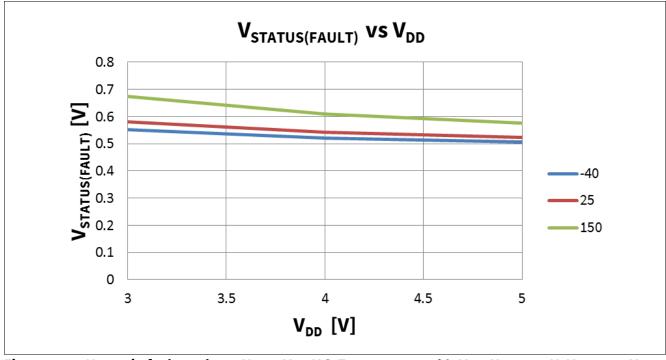

In case of detected overtemperature the fault signal will be set and the STATUS pin will be internally pulled down to  $V_{\text{STATUS}(\text{FAULT})}$ .

This  $V_{\text{STATUS}}$  is independent from the IN signal, providing a stable fault signal (Logic "low") to be read out by a micro controller.

The latched fault signal needs to be reset by a pull-up signal ( $V_{\text{STATUS}} \ge V_{\text{STATUS}(\text{RESET})}$ ) at the STATUS pin for a minimum duration of  $t_{\text{RESET}}$ , provided that the junction temperature has decreased at least from the thermal hysteresis in the meantime.

The latched fault signal can also be reset by setting ENABLE=low. See **Chapter 6.4** for an overview of reset conditions.

See "Diagnostics" on Page 26 for details on the feedback and reset function.

# infineon

#### **Protection Functions**

Figure 17 Thermal protective switch OFF scenario for case of overload or short circuit

Note: For better understanding, the time scale is not linear. The real timing of this drawing is application dependant and cannot be described.

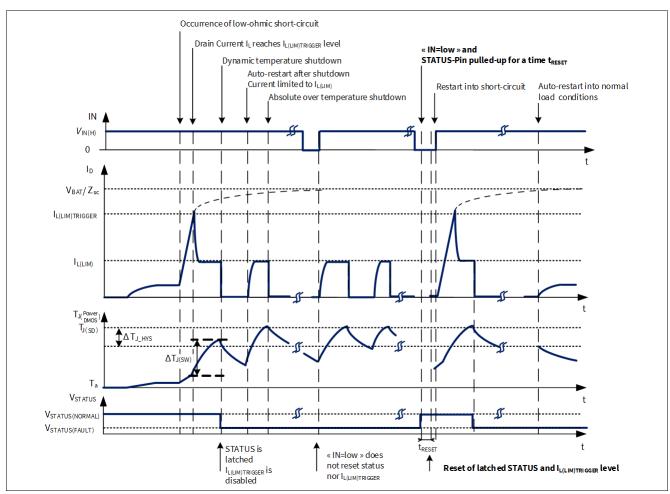

## 6.3 Overcurrent Limitation / Short Circuit Behavior

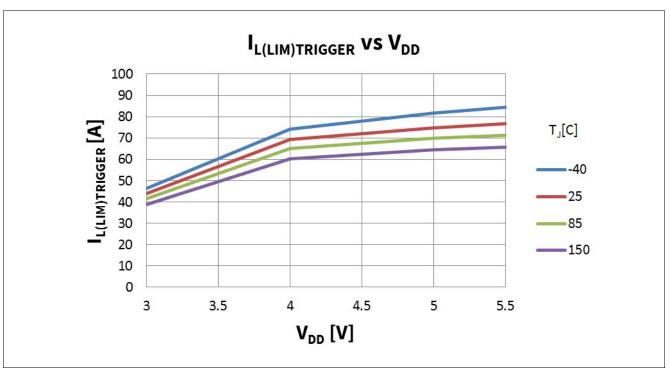

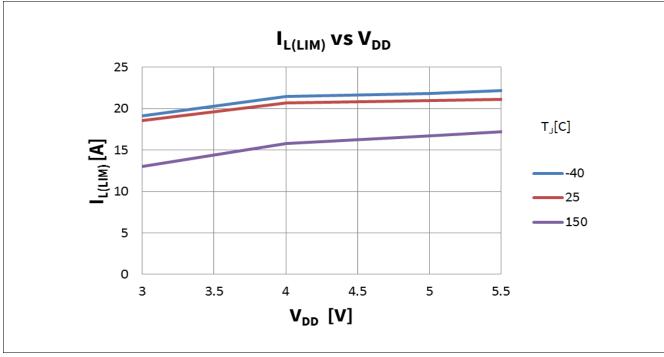

BTF3035EJ provides a smart overcurrent limitation intended to protect against short circuit conditions while allowing also load inrush currents higher than the current limitation level. It has a current limitation level  $I_{L(LIM)}$  which is triggered by a higher trigger level  $I_{L(LIM)}$ TRIGGER.

If the load current  $I_L$  reaches the current limitation trigger level  $I_{L(LIM)TRIGGER}$ , the internal current limitation will be activated and the device limits the current to a lower value  $I_{L(LIM)}$ .

The  $I_{L(LIM)TRIGGER}$  function has a latch behaviour, it happens once and is disabled until it is reset.

Then, BTF3035EJ behaves as a normal auto-restart, current limiting device: It keeps heating up at  $I_{L(LIM)}$  until the thermal shutdown temperature  $T_{J(SD)}$  is reached, then it turns off.

Due to autorestart feature, the MOSFET turns on again after it drops in temperature below thermal hysteresis ( $\Delta T_{\rm J\_HYS}$ ). If fault situation is still present, the current will be limited to  $I_{\rm L(LIM)}$  as the trigger feature is now disabled. The time to over temperature switch off strongly depends on the cooling conditions.

To reset the  $I_{\text{L(LIM)TRIGGER}}$  level feature, two conditions are necessary. The STATUS pin needs a pull-up signal  $(V_{\text{STATUS}} \ge V_{\text{STATUS}(\text{RESET})})$  for a minimum duration of  $t_{\text{RESET}}$ , and the IN pin must be in low state  $(V_{\text{IN}} \le V_{\text{IN(L)}})$  at the same time

The  $I_{L(LIM)TRIGGER}$  level feature can also be reset by setting ENABLE=low. See **Chapter 6.4** for an overview of reset conditions.

Figure 18 "Short circuit protection via current limitation and thermal switch off, with latched fault signal on STATUS" on Page 23 shows this behavior.

#### **Protection Functions**

Figure 18 Short circuit protection via current limitation and thermal switch off, with latched fault signal on STATUS

Note: For better understanding, the time scale is not linear. The real timing of this drawing is application dependant and cannot be described.

## **Smart Low-Side Power Switch**

#### **Protection Functions**

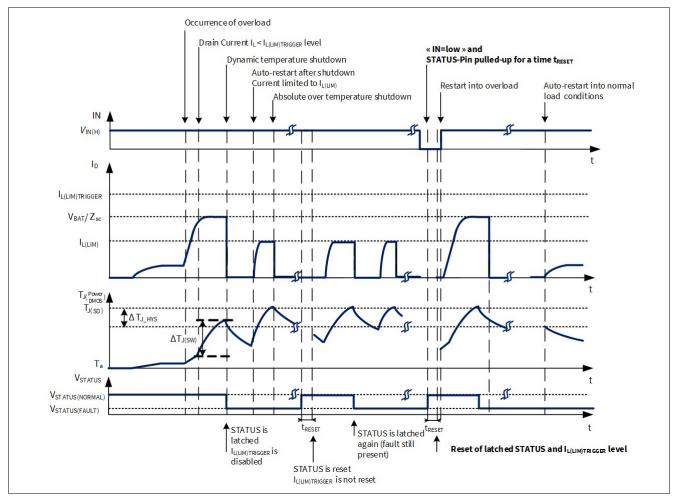

## Behavior with overload current below current limitation trigger level

The lower current limitation level  $I_{L(LIM)}$  is also triggered by any thermal shutdown. It can be the case when a still current, below the overcurrent limitation trigger level ( $I_L < I_{L(LIM)TRIGGER}$ ), provokes an over temperature shutdown. Any over temperature shutdown disables the  $I_{L(LIM)TRIGGER}$  function.

Figure 19 Example of overload behavior with thermal shutdown

Note: For better understanding, the time scale is not linear. The real timing of this drawing is application dependant and cannot be described.

## **Smart Low-Side Power Switch**

#### **Protection Functions**

## **6.4** Reset conditions

The following table gives the reset conditions of the latched STATUS signal and the  $I_{L(LIM)TRIGGER}$  function. Additionally, both functions are reset when ENABLE=low, regardless of STATUS and IN pin states.

|                                                                                                                                    | STATUS pin for a minimum time $t_{\scriptsize{\sf RESET}}$ | IN pin                                           |

|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------|

| Reset of Latched STATUS <sup>1)</sup>                                                                                              | Pull-up to V <sub>DD</sub>                                 | X <sup>2)</sup>                                  |

| Reset of I <sub>(LIM)TRIGGER</sub> level <sup>3)</sup>                                                                             | Pull-up to V <sub>DD</sub>                                 | low                                              |

| $^{1)}$ Does not reset $I_{(LIM)TRKGGER}$ level if I $^{2)}$ Regardless of IN pin state, latched $^{3)}$ Also reset latched STATUS |                                                            | p for a minimum time $t_{	t 	extsf{	iny RESET}}$ |

Figure 20 Reset conditions of latched STATUS signal and  $I_{L(LIM)TRIGGER}$  function.

#### **Smart Low-Side Power Switch**

## **Diagnostics**

# 7 Diagnostics

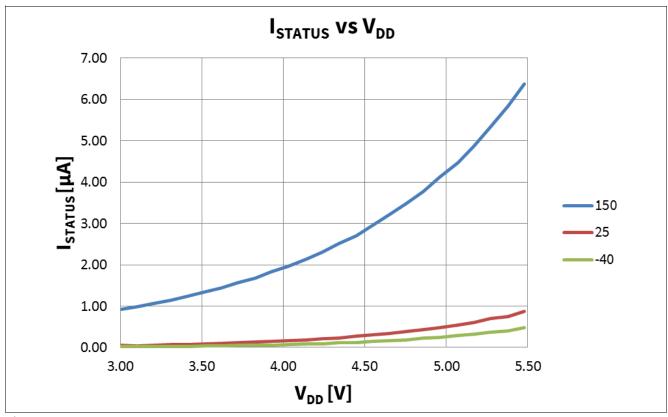

The BTF3035EJ provides a latched digital fault feedback signal on the STATUS pin triggered by an over temperature or dynamic temperature shutdown.

## 7.1 Functional Description of the STATUS pin

The BTF3xxxEJ series provides digital status information via the STATUS pin to give an alarm feedback to a possible connected micro controller. See Figure 17 "Thermal protective switch OFF scenario for case of overload or short circuit" on Page 22.

## Normal operation mode

In normal operation (no fault is detected) the STATUS pin is logic "high". It is pulled up via an external Resistor with a recommended value of  $4.7k\Omega$ . Internally it is connected to an open drain MOSFET via an internal Resistor.

#### **Fault operation**

In case of a temperature shutdown the internal MOSFET of the BTF3xxxEJ series pulls the STATUS pin down to approx 0.5V, which a connected microcontroller would accept as logic "low" level signal for a  $4.7k\Omega$  pull-up resistor. This mode stays active independent from the input pin state or internal auto-restarts until it is reset.

#### Reset Latch (external pull up)

To reset the latched STATUS signal, the STATUS pin has to be pulled-up to  $V_{DD}$ , for a minimum time of  $t_{RESET}$ . The IN pin state does not matter to reset the latched STATUS signal. See **Chapter 11** for an example of basic circuitry to use this digital feedback function.

## Reset I<sub>L(LIM)TRIGGER</sub>

See **Chapter 6.3** for detailed explanation on the function and **Chapter 6.4** for a quick overview of reset mechanism.

### 7.2 Characteristics

See Table 9.3 "Diagnostics" on Page 34 for electrical characteristics.

**Supply and Input Stage**

#### 8 **Supply and Input Stage**

#### 8.1 **Supply Circuit**

The supply pin  $V_{\rm DD}$  is protected against ESD pulses as shown in **Figure 21**.

The device supply is not internally regulated but directly taken from a external supply. Therefore a reverse polarity protected and buffered (3.0V..5.5V) voltage supply is required. To achieve a reasonable  $R_{DS(ON)}$  and the specified switching speed a 5V supply is required.

**Supply Circuit** Figure 21

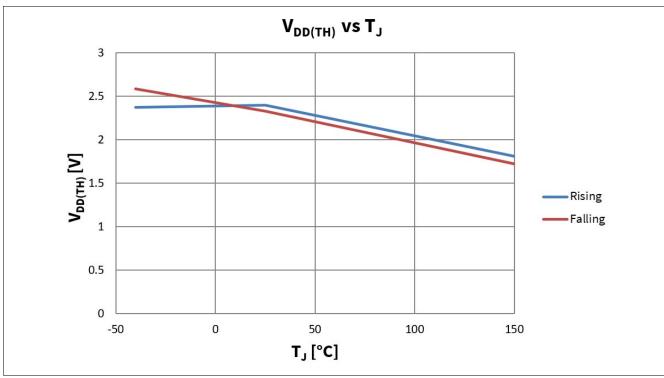

#### 8.2 **Undervoltage Shutdown**

In order to ensure a stable and defined device behavior under all allowed conditions the supply voltage  $V_{\rm DD}$  is monitored.

If the supply voltage  $V_{\rm DD}$  drops below the switch-off threshold  $V_{\rm DD(TH)}$ , the power DMOS switches off. In this case ENABLE pin is pulled to low state and both latched STATUS and  $I_{L(LIM)TRIGGER}$  level are reset (See Chapter 6.4, Reset conditions). All device functions are only specified for supply voltages above the supply voltage threshold  $V_{\rm DD(TH)MAX}$ . There is no fault feedback ensured for  $V_{\rm DD} < V_{\rm DD(TH)}$ .

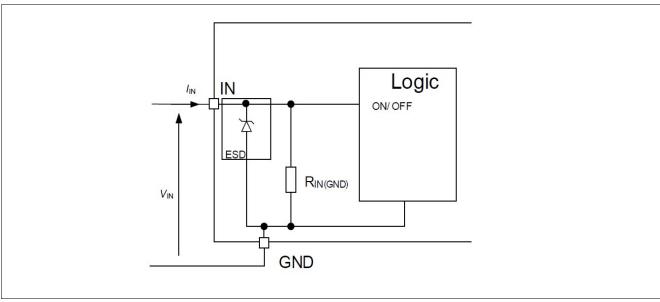

#### 8.3 Input/Enable Circuit

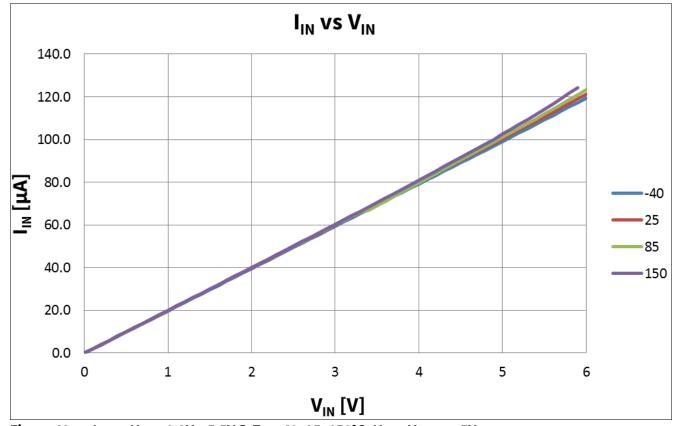

Figure 22 shows the IN pin circuit of the BTF3035EJ. Due to an internal pull-down it is ensured that the device switches off in case of open IN pin. A Zener structure protects the input circuit against ESD pulses.

This structure is also valid for ENABLE pin.

## **Supply and Input Stage**

Figure 22 Simplified IN/ENABLE pin circuitry

## 8.4 Functional Description of the SRP Pin

The BTF3035EJ provides the possibility to adjust slewrate with an external resistor connected to the Slew-Rate-Preset pin (SRP). It defines the strength of the gate driver stage used to switch the power DMOS. The greater the resistor the lesser the current driven by the slew rate logic block to the gate driver block, which will result in a slower turn-on and turn-off. For details on this function please refer to "Adjustable Switching Speed / Slew Rate" on Page 19.

Figure 23 Simplified functional block diagram of SRP pin

## **Smart Low-Side Power Switch**

**Supply and Input Stage**

## 8.5 Characteristics

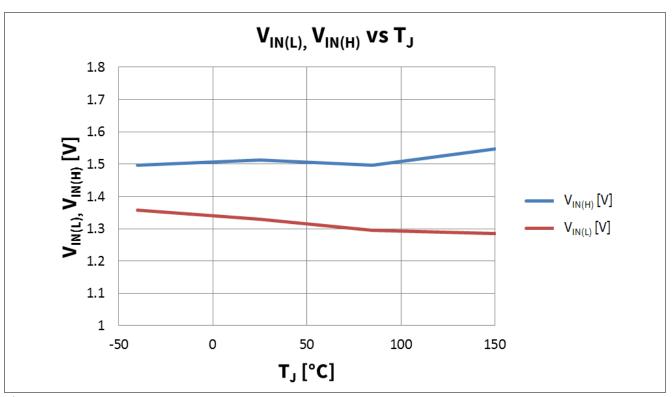

Please see **Table "INPUT" on Page 36**, **Table "ENABLE" on Page 36** for INPUT and ENABLE electrical characteristics.

The timings **Table** shows slew rate for specific resistor values, for the SRP pin electrical characteristics please see **Table "SRP" on Page 36**.

## **Smart Low-Side Power Switch**

#### **Electrical Characteristics**

## 9 Electrical Characteristics

Note:

Characteristics show the deviation of parameter at given input voltage and junction temperature. Typical values show the typical parameters expected from manufacturing and in typical application condition.

All voltages and currents naming and polarity in accordance to Figure 3 "Naming Definition of electrical parameters" on Page 7

## 9.1 Power Stage

See Chapter "Power Stage" on Page 15 for parameters description and further details.

## Table 5 Electrical Characteristics: Power Stage

$T_J$  = -40°C to +150°C,  $V_{DD}$  = 3.0 V to 5.5 V,  $V_{BAT}$  = 6 V to 18 V, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                         | Symbol                 |      | Value | S    | Unit | Note or<br>Test Condition                                                                                                                     | Number   |

|---------------------------------------------------|------------------------|------|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                   |                        | Min. | Тур.  | Max. |      |                                                                                                                                               |          |

| Power Stage - Static Characteris                  | stics                  |      | 1     |      | 1    |                                                                                                                                               | 1        |

| On-State resistance                               | R <sub>DS(ON)</sub>    | -    | 32    | _    | mΩ   | $I_{L} = I_{L(NOM)};$<br>$V_{DD} = 5V;$<br>$T_{J} = 25^{\circ}C$                                                                              | P_9.1.4  |

| On-State resistance                               | $R_{\mathrm{DS(ON)}}$  | -    | 60    | 70   | mΩ   | $I_L = I_{L(NOM)};$<br>$V_{DD} = 5V;$<br>$T_J = 150$ °C                                                                                       | P_9.1.9  |

| Nominal load current                              | I <sub>L(NOM)</sub>    | -    | 5     | _    | A    | $^{1)}T_{J} < 150^{\circ}C;$<br>$V_{DD} = 5 V;$                                                                                               | P_9.1.34 |

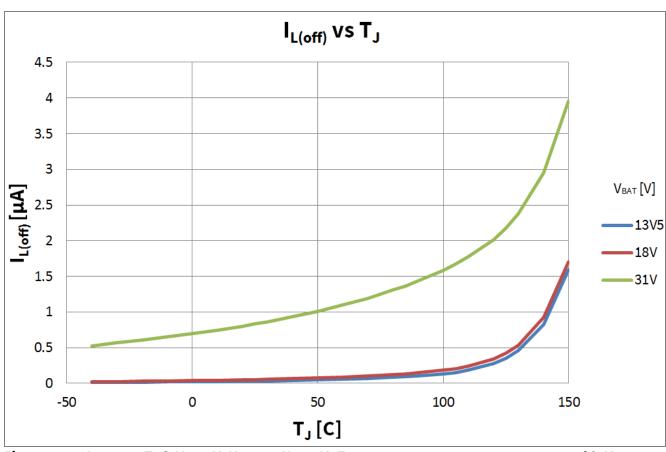

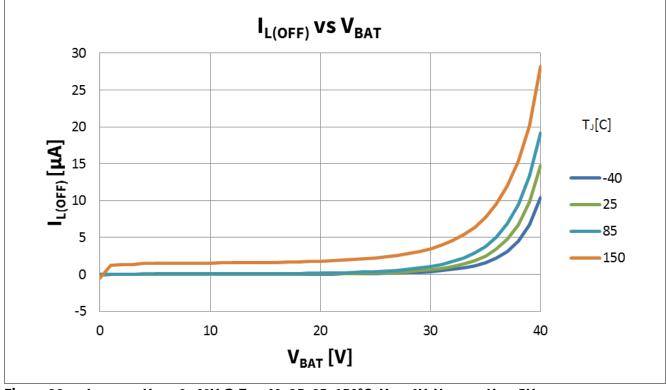

| OFF state load current, Output leakage current    | I <sub>L(OFF)25</sub>  | -    | 2     | 4.5  | μА   | $V_{BAT} = 13.5 \text{ V};$<br>$V_{IN} = 0 \text{ V};$<br>$V_{DD} = 5 \text{ V};$<br>$T_{J} \le 85^{\circ}\text{C}$                           | P_9.1.39 |

| OFF state load current, Output<br>leakage current | / <sub>L(OFF)150</sub> | -    | 3     | 9    | μΑ   | $V_{\text{BAT}} = 18 \text{ V};$<br>$V_{\text{IN}} = 0 \text{ V};$<br>$V_{\text{DD}} = 5 \text{ V};$<br>$T_{\text{J}} = 150 ^{\circ}\text{C}$ | P_9.1.44 |

| Reverse Diode                                     |                        |      |       |      |      |                                                                                                                                               |          |

| Reverse diode forward voltage                     | -V <sub>DS</sub>       | -    | 0.8   | 1.5  | V    | $I_D = -I_{L(NOM)};$ $V_{IN} = 0 \text{ V}$                                                                                                   | P_9.1.50 |

Power Stage - Dynamic characteristics - switching time adjustment  $V_{\rm BAT}$  = 13.5V,  $V_{\rm DD}$  = 5 V; resistive load:  $R_{\rm L}$  = 2.2 $\Omega$ ;  $C_{\rm SRP-GND}$  < 100 pF;

see also Figure 12 "Definition of Power Output Timing for Resistive Load" on Page 16

|               | -                   | _    |      |     |    | •                          |          |

|---------------|---------------------|------|------|-----|----|----------------------------|----------|

| Turn-on time  | $t_{ON(0)}$         | 0.45 | 1.35 | 2.8 | μs | $R_{\text{SRP}} = 0\Omega$ | P_9.1.51 |

| Turn-off time | t <sub>OFF(0)</sub> | 8.0  | 2    | 4   | μs | $R_{\text{SRP}} = 0\Omega$ | P_9.1.55 |

## **Smart Low-Side Power Switch**

## **Electrical Characteristics**

## **Table 5 Electrical Characteristics: Power Stage** (cont'd)

$T_{\rm J}$  = -40°C to +150°C,  $V_{\rm DD}$  = 3.0 V to 5.5 V,  $V_{\rm BAT}$  = 6 V to 18 V, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                 | Symbol                      | Values |      |      | Unit | Note or                                              | Number   |

|---------------------------|-----------------------------|--------|------|------|------|------------------------------------------------------|----------|

|                           |                             | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                |          |

| Turn-on delay time        | $t_{DON(0)}$                | 0.15   | 0.35 | 0.8  | μs   | $R_{\rm SRP} = 0\Omega$                              | P_9.1.59 |

| Turn-off delay time       | t <sub>DOFF(0)</sub>        | 0.5    | 1    | 2    | μs   | $R_{\rm SRP} = 0\Omega$                              | P_9.1.63 |

| Turn-on output fall time  | t <sub>F(0)</sub>           | 0.3    | 1    | 2    | μs   | $R_{\rm SRP} = 0\Omega$                              | P_9.1.67 |

| Turn-off output rise time | $t_{R(0)}$                  | 0.3    | 1    | 2    | μs   | $R_{\rm SRP} = 0\Omega$                              | P_9.1.71 |

| Turn-on Slew rate 5)      | -(DV/Dt) <sub>ON(0)</sub>   | 15     | 27   | 45   | V/µs | $R_{SRP} = 0\Omega$                                  | P_9.1.75 |

| Turn-off Slew rate        | (DV/Dt) <sub>OFF(0)</sub>   | 15     | 27   | 45   | V/µs | $R_{SRP} = 0\Omega$                                  | P_9.1.79 |

| Turn-on time              | t <sub>ON(5k8)</sub>        | 1.3    | 2.7  | 4.5  | μs   | $R_{SRP} = 5.8 \text{k}\Omega$                       | P_9.1.52 |

| Turn-off time             | t <sub>OFF(5k8)</sub>       | 2      | 4    | 6    | μs   | $R_{\text{SRP}} = 5.8 \text{k}\Omega$                | P_9.1.56 |

| Turn-on delay time        | t <sub>DON(5k8)</sub>       | 0.3    | 0.75 | 1.5  | μs   | $R_{\rm SRP} = 5.8 {\rm k}\Omega$                    | P_9.1.60 |

| Turn-off delay time       | t <sub>DOFF(5k8)</sub>      | 1      | 2    | 3    | μs   | $R_{\rm SRP} = 5.8 \mathrm{k}\Omega$                 | P_9.1.64 |

| Turn-on output fall time  | t <sub>F(5k8)</sub>         | 1      | 2    | 3    | μs   | $R_{\rm SRP} = 5.8 \mathrm{k}\Omega$                 | P_9.1.68 |

| Turn-off output rise time | t <sub>R(5k8)</sub>         | 1      | 2    | 3    | μs   | $R_{\rm SRP} = 5.8 \mathrm{k}\Omega$                 | P_9.1.72 |

| Turn-on Slew rate         | -(DV/Dt) <sub>ON(5k8)</sub> | 7      | 13   | 21   | V/µs | $R_{\text{SRP}} = 5.8 \text{k}\Omega$                | P_9.1.76 |

| Turn-off Slew rate        | (DV/Dt) <sub>OFF(5k8)</sub> | 7      | 13   | 21   | V/µs | $R_{\text{SRP}} = 5.8 \text{k}\Omega$                | P_9.1.80 |

| Turn-on time              | t <sub>ON(58k)</sub>        | 13     | 26   | 40   | μs   | $R_{SRP} = 58k\Omega$                                | P_9.1.53 |

| Turn-off time             | t <sub>OFF(58k)</sub>       | 23     | 35   | 70   | μs   | $R_{\text{SRP}} = 58 \text{k}\Omega$ <sup>4)</sup>   | P_9.1.57 |

| Turn-on delay time        | t <sub>DON(58k)</sub>       | 3      | 6    | 10   | μs   | $R_{\rm SRP} = 58 \mathrm{k}\Omega$                  | P_9.1.61 |

| Turn-off delay time       | t <sub>DOFF(58k)</sub>      | 7      | 15   | 35   | μs   | $R_{\rm SRP} = 58 \mathrm{k}\Omega$                  | P_9.1.65 |

| Turn-on output fall time  | t <sub>F(58k)</sub>         | 10     | 20   | 30   | μs   | $R_{\rm SRP} = 58 \mathrm{k}\Omega$                  | P_9.1.69 |

| Turn-off output rise time | t <sub>R(58k)</sub>         | 10     | 20   | 30   | μs   | $R_{\rm SRP} = 58 \mathrm{k}\Omega$                  | P_9.1.73 |

| Turn-on Slew rate         | -(DV/Dt) <sub>ON(58k)</sub> | 0.7    | 1.4  | 2.1  | V/µs | $R_{\text{SRP}} = 58k\Omega$                         | P_9.1.77 |

| Turn-off Slew rate        | (DV/Dt) <sub>OFF(58k)</sub> | 0.7    | 1.4  | 2.1  | V/µs | $R_{\text{SRP}} = 58k\Omega$                         | P_9.1.81 |

| Turn-on time              | t <sub>ON(open)</sub>       | 40     | 80   | 130  | μs   | $R_{SRP} = 200k\Omega(open)$                         | P_9.1.54 |

| Turn-off time             | t <sub>OFF(open)</sub>      | 55     | 110  | 190  | μs   | $R_{SRP} = 200 k\Omega(open)$                        | P_9.1.58 |

| Turn-on delay time        | t <sub>DON(open)</sub>      | 10     | 20   | 40   | μs   | $R_{\rm SRP} = 200  \mathrm{k}\Omega(\mathrm{open})$ | P_9.1.62 |

## **Smart Low-Side Power Switch**

#### **Electrical Characteristics**

#### **Table 5 Electrical Characteristics: Power Stage (cont'd)**

$T_J$  = -40°C to +150°C,  $V_{DD}$  = 3.0 V to 5.5 V,  $V_{BAT}$  = 6 V to 18 V, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| arameter Symbol           |                              |      | Value | s    | Unit | Note or                                             | Number   |

|---------------------------|------------------------------|------|-------|------|------|-----------------------------------------------------|----------|

|                           |                              | Min. | Тур.  | Max. |      | <b>Test Condition</b>                               |          |

| Turn-off delay time       | t <sub>DOFF(open)</sub>      | 25   | 50    | 100  | μs   | $R_{\rm SRP} = 200 \mathrm{k}\Omega(\mathrm{open})$ | P_9.1.66 |

| Turn-on output fall time  | t <sub>F(open)</sub>         | 30   | 60    | 90   | μs   | $R_{\rm SRP} = 200 {\rm k}\Omega({\rm open})$       | P_9.1.70 |

| Turn-off output rise time | $t_{R(open)}$                | 30   | 60    | 90   | μs   | $R_{\rm SRP} = 200 {\rm k}\Omega({\rm open})$       | P_9.1.74 |

| Turn-on Slew rate         | -(DV/Dt) <sub>ON(open)</sub> | 0.25 | 0.5   | 0.7  | V/µs | $R_{\text{SRP}} = 200 \text{k}\Omega(\text{open})$  | P_9.1.78 |

| Turn-off Slew rate        | (DV/Dt) <sub>OFF(open)</sub> | 0.25 | 0.5   | 0.7  | V/µs | $R_{\text{SRP}} = 200 \text{k}\Omega(\text{open})$  | P_9.1.82 |

- 1) Not subject to production test, calculated by R<sub>th,IA</sub> and R<sub>DS(ON)</sub>. (JEDEC2S2P)

- 2) Not subject to production test, specified by design

- 3) Not subject to production test, calculated by  $(t_{DON+}t_{F})$

- 4) Not subject to production test, calculated by  $(t_{DOFF}, t_{R})$

- 5) Not subject to production test, calculated slew rate between 90% and 50%; see **Figure 12 "Definition of Power Output Timing for Resistive Load" on Page 16**

## 9.2 Protection

See Chapter "Protection Functions" on Page 21 for parameter description and further details.

Note:

Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation

#### **Table 6 Electrical characteristics: Protection**

$T_J$  = -40°C to +150°C,  $V_{DD}$  = 3.0 V to 5.5 V;  $V_{BAT}$  = 6 V to 18 V, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                              | Symbol               |          | Values |      | Unit | Note or                                | Number  |

|----------------------------------------|----------------------|----------|--------|------|------|----------------------------------------|---------|

|                                        |                      | Min.     | Тур.   | Max. |      | <b>Test Condition</b>                  |         |

| Thermal shut down 1)                   |                      | <b>"</b> |        | 1    |      |                                        |         |

| Thermal shut down junction temperature | $T_{J(SD)}$          | 150      | 175    | 200  | °C   | 1)                                     | P_9.2.1 |

| Thermal hysteresis                     | $\Delta T_{J-HYS}$   | _        | 15     | _    | K    | 1)                                     | P_9.2.3 |

| Dynamic temperature limitation         | $\Delta T_{J(SW)}$   | _        | 70     | _    | K    | 1)                                     | P_9.2.4 |

| Over Voltage Protection / Clamp        | ing                  | <u>"</u> |        |      |      |                                        |         |

| Drain clamp voltage                    | $V_{\rm OUT(CLAMP)}$ | 40       | _      | _    | V    | $V_{IN} = 0 \text{ V}; I_{L} = 14$ mA; | P_9.2.7 |

## **Smart Low-Side Power Switch**

## **Electrical Characteristics**

## **Table 6 Electrical characteristics: Protection** (cont'd)

$T_{\rm J}$  = -40°C to +150°C,  $V_{\rm DD}$  = 3.0 V to 5.5 V;  $V_{\rm BAT}$  = 6 V to 18 V, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                          | Symbol                     | Values |      |      | Unit | Note or                                                                      | Number   |

|------------------------------------|----------------------------|--------|------|------|------|------------------------------------------------------------------------------|----------|