#### **Features**

- Operating voltage: 2.4V~5.5V

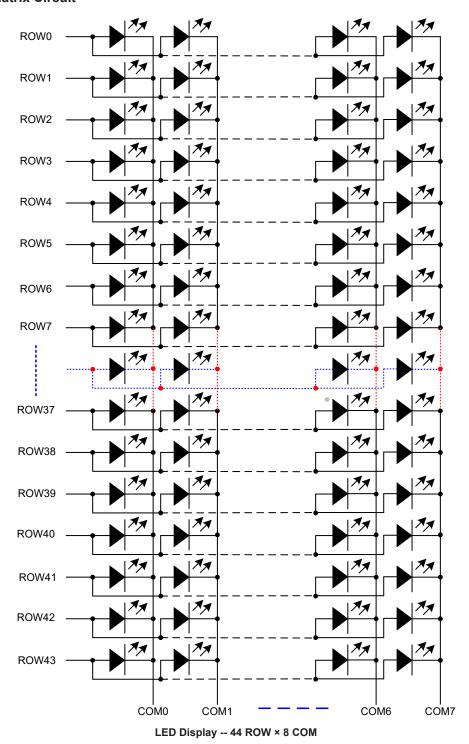

- LED display -- 44 row and 8 Columns

- 88×4 bit RAM display data storage

- 16-level PWM brightness control

- Integrated 256kHz RC oscillator

- I<sup>2</sup>C-bus or 4-wire serial interface

- Data mode & command mode instructions

- Cascade function for extend applications

- Selectable NMOS open drain output driver and PMOS open drain output driver for COM lines

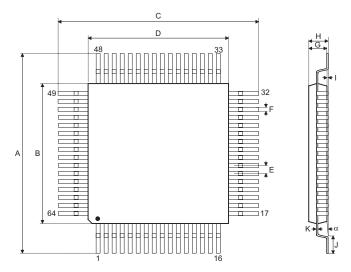

- 64-pin LQFP package

# **Applications**

- · Industrial control displays

- Digital clocks, thermometers, counters, electronic meters

- Instrumentation readouts

- Other consumer applications

- · LED displays

# **General Description**

The HT1635C/HT1635D series is a memory mapping LED display controller/driver. The maximum display capacity of the device is 352 patterns composed of 44 rows and 8 commons. The devices can generate 16 LED illumination levels using software controlled PWM circuitry. A serial interface is provided to allow the device to receive instructions for its command mode and data mode. Only two or four lines are required to interface the device to a host controller. The display capacity can be easily extended by cascading the devices thus expanding its application possibilities. The device is compatible with most microcontrollers offering easy interfacing via its two serial interfaces, an I<sup>2</sup>C bus or a 4-wire serial bus.

## **Selection Table**

Most features are common to these devices and the main feature distinguishing them is communication interface. In real applications, the recommended operating voltage ranges from 4.5V to 5.5V. The following table summarises the main features of each device.

| Part No | V <sub>DD</sub> | Max. Resolution Row×Common | Row Source<br>Current (Min.) | Row Sink<br>Current (Min.) | Com Source<br>Current (Min.) |

|---------|-----------------|----------------------------|------------------------------|----------------------------|------------------------------|

| HT1635C | 4.5V~5.5V       | 44x8                       | 50mA                         | 10mA                       | 45mA                         |

| HT1635D |                 |                            |                              |                            |                              |

| Part No | Com Sink Current (Min.) | PWM Gray Scale      | Interface        | Package |

|---------|-------------------------|---------------------|------------------|---------|

| HT1635C | 250mA                   | 16-Level for Global | 4-Wire           | 64LQFP  |

| HT1635D |                         |                     | I <sup>2</sup> C |         |

Rev. 1.00 1 July 09, 2021

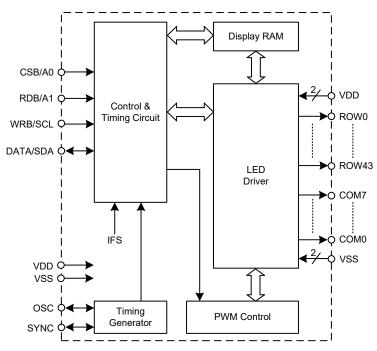

# **Block Diagram**

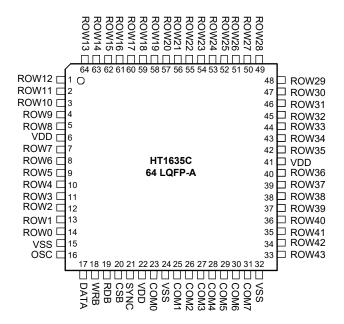

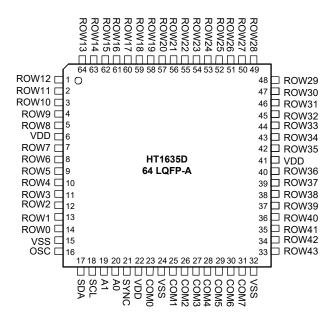

# **Pin Assignment**

Rev. 1.00 2 July 09, 2021

# **Pin Description**

| Pin Name   | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COM0~COM7  | 0   | LED common output lines.                                                                                                                                                                                                                                                                                                                                                                                |

| ROW0~ROW43 | 0   | LED row output lines.                                                                                                                                                                                                                                                                                                                                                                                   |

| VDD        | _   | Positive power supply. In PCB Layout that must connect all of the VDD pins to the power plane.                                                                                                                                                                                                                                                                                                          |

| vss        | _   | Negative power supply. In PCB Layout that must connect all of the VSS pins to the GND plane.                                                                                                                                                                                                                                                                                                            |

| DATA/SDA   | I/O | Serial data input/output pin. Data is input to / comes out from the shift register at rising edge of the clock.  I'C interface serial data (SDA) Input/Output. NMOS open-drain output  4-wire serial interface serial data input/output. Input has pull-high resistor and output is CMOS type.                                                                                                          |

| WRB/SCL    | I   | Serial clock input pin.  I'C interface serial clock SCL input.  4-wire serial interface WRITE Clock (CLK) input. Connected to pull-high resistor. Data on the DATA line is latched into the device on the rising edge of the WRB signal.                                                                                                                                                                |

| RDB/A1     | I   | I <sup>2</sup> C interface device address data input pin.     4-wire serial interface READ clock input. Connected to pull-high resistor. The device RAM data is clocked out on the falling edge of RDB. The clocked out data will appear on the DATA line. The host controller can use the next rising edge to latch the clocked out data.                                                              |

| CSB/A0     | I   | <ul> <li>I<sup>2</sup>C interface device address data input pin.</li> <li>Chip select input. Connected to pull-high resistor. When CSB is high, a data and command instruction read from or written to the device is disabled and the serial interface circuit is also reset. If CSB is low data and command instruction transmission between the host controller and the device is enabled.</li> </ul> |

| osc        | I/O | If the RC MASTER MODE command is programmed, the system clock is sourced from the internal RC oscillator and the system clock is output on the OSC pin.     If the SLAVE MODE or EXT CLK MASTER MODE command is programmed, the system clock is sourced from an external clock on the OSC pin.                                                                                                          |

| SYNC       | I/O | If the RC MASTER MODE or EXT CLK MASTER MODE command is programmed, the synchronous signal is output on the SYNC pin.     If the SLAVE MODE command is programmed, the synchronous signal is input on the SYNC pin.                                                                                                                                                                                     |

Rev. 1.00 3 July 09, 2021

# **Absolute Maximum Ratings**

| Supply Voltage                | . $V_{SS}$ -0.3V to $V_{SS}$ +6.0V |

|-------------------------------|------------------------------------|

| Max junction Temperature (Tj) | 125°C                              |

| Storage Temperature           | 50°C to 125°C                      |

| Power Dissipation (PD)  | (@Ta=25°C)               | 2.5W                    |

|-------------------------|--------------------------|-------------------------|

| (                       | (@Ta=85°C)               | 1.0W                    |

| Input Voltage           | V <sub>SS</sub> -0.3V to | 0 V <sub>DD</sub> +0.3V |

| Thermal Resistance (Rtl | h)                       | 40°C/W                  |

| Operating Temperature   | 40                       | 0°C to 85°C             |

- Note: 1. These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

- 2. For the actual usage, please refer to the PD-Ta characteristics diagram in the package specification, follow the power supply voltage, load and ambient temperature conditions to ensure that there is enough margin and the thermal design does not exceed the allowable value.

# **D.C. Characteristics**

V<sub>DD</sub>=2.4V~5.5V; Ta=25°C

| Comple al        | Parameter                                 |                 | Test Conditions                             | Min                | True | Mari               | 11   |

|------------------|-------------------------------------------|-----------------|---------------------------------------------|--------------------|------|--------------------|------|

| Symbol           | Parameter                                 | V <sub>DD</sub> | Conditions                                  | Min.               | Тур. | Max.               | Unit |

| $V_{DD}$         | Operating Voltage                         | <b> </b> —      | _                                           | 2.4                | 5    | 5.5                | V    |

| I <sub>DD</sub>  | Operating Current                         | 5V              | No load, LED on,<br>On-chip RC oscillator   | _                  | 0.3  | 0.6                | mA   |

| I <sub>STB</sub> | Standby Current                           | 5V              | No load, Power down mode                    | _                  | 1    | 2                  | μΑ   |

| V <sub>IL</sub>  | Input Low Voltage                         | 5V              | DATA, WRB, RDB, SDA, SCL,<br>CSB, OSC, SYNC | 0                  | _    | 0.3V <sub>DD</sub> | V    |

| V <sub>IH</sub>  | Input High Voltage                        | 5V              | DATA, WRB, RDB, SDA, SCL,<br>CSB, OSC, SYNC | 0.7V <sub>DD</sub> | _    | 5                  | V    |

| I <sub>OL1</sub> | OSC, SYNC, DATA, SDA<br>Pins Sink Current | 5V              | V <sub>OL</sub> =0.5V                       | 18                 | 25   | _                  | mA   |

| I <sub>ОН1</sub> | OSC, SYNC, DATA<br>Pins Source Current    | 5V              | V <sub>OH</sub> =4.5V                       | -10                | -13  | _                  | mA   |

| I <sub>OL2</sub> | ROW Sink Current                          | 5V              | V <sub>OL</sub> =0.5V                       | 10                 | 13   | _                  | mA   |

| I <sub>OH2</sub> | ROW Source Current                        | 5V              | V <sub>OH</sub> =4.5V                       | -50                | -70  | _                  | mA   |

| I <sub>OL3</sub> | COM Sink Current                          | 5V              | V <sub>OL</sub> =0.5V                       | 250                | 400  | _                  | mA   |

| I <sub>ОН3</sub> | COM Source Current                        | 5V              | V <sub>OH</sub> =4.5V                       | -45                | -60  | _                  | mA   |

| R <sub>PH</sub>  | Pull-high Resistor                        | 5V              | DATA, WRB, RDB, CSB                         | 18                 | 27   | 40                 | kΩ   |

Rev. 1.00 4 July 09, 2021

# A.C. Characteristics

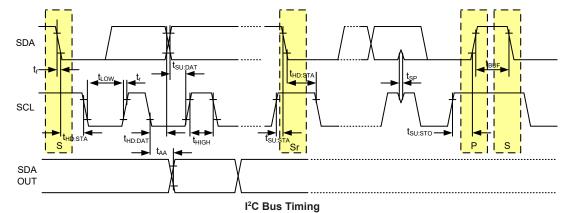

# I<sup>2</sup>C Serial Bus

V<sub>DD</sub>=2.4V~5.5V, Ta=25°C

| Complete             | Domenton                                      | Condition                                                                    | V <sub>DD</sub> =2.4 | V to 5.5V | V <sub>DD</sub> =3.0\ | / to 5.5V | Unit |

|----------------------|-----------------------------------------------|------------------------------------------------------------------------------|----------------------|-----------|-----------------------|-----------|------|

| Symbol               | Parameter                                     | Condition                                                                    | Min.                 | Max.      | Min.                  | Max.      | Unit |

| f <sub>SCL</sub>     | Clock Frequency                               | _                                                                            | _                    | 100       | _                     | 400       | kHz  |

| t <sub>BUF</sub>     | Bus Free Time                                 | Time in which the bus<br>must be free before a new<br>transmission can start | 4.7                  | _         | 1.3                   |           | μs   |

| t <sub>HD: STA</sub> | Start Condition Hold Time                     | After this period, the first clock pulse is generated                        | 4                    | _         | 0.6                   | _         | μs   |

| t <sub>LOW</sub>     | SCL Low Time                                  | _                                                                            | 4.7                  | _         | 1.3                   | _         | μs   |

| t <sub>HIGH</sub>    | SCL High Time                                 | _                                                                            | 4                    | _         | 0.6                   | _         | μs   |

| t <sub>SU: STA</sub> | Start Condition Setup Time                    | Only relevant for repeated START condition                                   | 4.7                  | _         | 0.6                   | _         | μs   |

| t <sub>HD: DAT</sub> | Data Hold Time                                | _                                                                            | 0                    | _         | 0                     | _         | ns   |

| t <sub>SU: DAT</sub> | Data Setup Time                               | _                                                                            | 250                  | _         | 100                   | _         | ns   |

| t <sub>R</sub>       | SDA and SCL Rise Time                         | Note                                                                         | _                    | 1         | _                     | 0.3       | μs   |

| t <sub>F</sub>       | SDA and SCL Fall Time                         | Note                                                                         | _                    | 0.3       | _                     | 0.3       | μs   |

| t <sub>SU: STO</sub> | Stop Condition Setup Time                     | _                                                                            | 4                    | _         | 0.6                   | _         | μs   |

| t <sub>AA</sub>      | Output Valid from Clock                       | _                                                                            | _                    | 3.5       | _                     | 0.9       | μs   |

| t <sub>SP</sub>      | Input Filter Time Constant (SDA and SCL Pins) | Noise suppression time                                                       | _                    | 20        | _                     | 20        | ns   |

Note: These parameters are periodically sampled but not 100% tested.

Rev. 1.00 5 July 09, 2021

### 4-wire Serial Bus

V<sub>DD</sub>=2.4V~5.5V; Ta=25°C

| Cumbal                          | Dovemeter                                                | Parameter Test Conditions |                       | Min.    | Tren                   | May  | Unit |

|---------------------------------|----------------------------------------------------------|---------------------------|-----------------------|---------|------------------------|------|------|

| Symbol                          | Parameter                                                | V <sub>DD</sub>           | Conditions            | IVIIII. | Тур.                   | Max. | Unit |

| f <sub>sys</sub>                | System Clock                                             | 5V                        | On-chip RC oscillator | 230     | 256                    | 282  | kHz  |

| f <sub>LED</sub>                | LED Frame Rate                                           | 5V                        | 1/8 duty              | _       | f <sub>SYS</sub> /2624 | _    | Hz   |

| f <sub>clk1</sub>               | Serial Data Clock (WRB Pin)                              | 5V                        | Duty cycle 50%        | _       | _                      | 1    | MHz  |

| f <sub>clk2</sub>               | Serial Data Clock (RDB Pin)                              | 5V                        | Duty cycle 50%        | _       | _                      | 500  | kHz  |

| t <sub>cs</sub>                 | Serial Interface Reset Pulse Width                       | _                         | CSB                   | 250     | _                      | _    | ns   |

|                                 | W/DD DDD Input Dulco Width                               | 5V                        | Write mode            | 0.5     | _                      | _    |      |

| t <sub>clk</sub>                | WRB, RDB Input Pulse Width                               | 3 V                       | Read mode             | 1       | _                      | _    | μs   |

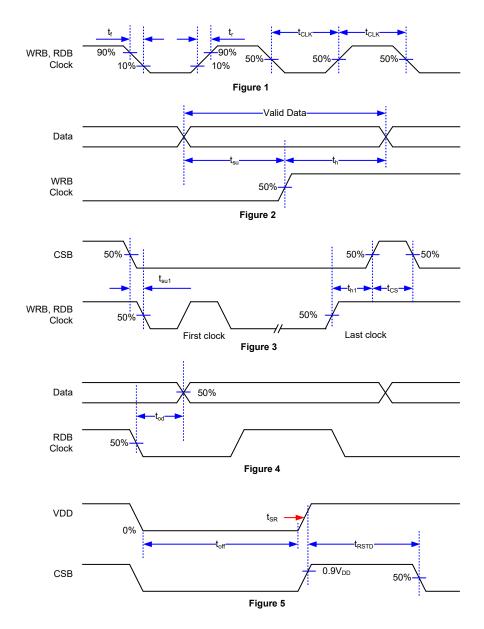

| t <sub>r</sub> , t <sub>f</sub> | Rise/Fall Time for WRB, RDB Signal (Figure 1)            | _                         | _                     | _       | 50                     | 100  | ns   |

| t <sub>su</sub>                 | Setup Time for DATA to WRB Clock Width (Figure 2)        | _                         | _                     | 50      | 100                    | _    | ns   |

| t <sub>h</sub>                  | Hold Time for DATA to WRB Clock Width (Figure 2)         | _                         | _                     | 100     | 200                    | _    | ns   |

| t <sub>su1</sub>                | Setup Time for CSB to WRB, RDB<br>Clock Width (Figure 3) | _                         | _                     | 200     | 300                    | _    | ns   |

| t <sub>h1</sub>                 | Hold Time for CSB to WRB, RDB<br>Clock Width (Figure 3)  | _                         | _                     | 100     | 200                    | _    | ns   |

| tod                             | Data Output Delay Time (Figure 4)                        | _                         | _                     | _       | 100                    | 200  | ns   |

| toff                            | V <sub>DD</sub> Off Times (Figure 5)                     | _                         | VDD drop down to 0V   | 10      | _                      |      | ms   |

| t <sub>SR</sub>                 | V <sub>DD</sub> Rising Slew Rate (Figure 5)              | _                         | _                     | 0.1     |                        | 0.8  | V/ms |

| t <sub>RSTD</sub>               | Delay Time After Reset (Figure 5)                        | _                         | _                     | 1       | _                      | _    | ms   |

Note: 1. If the conditions of the Power on Reset timing are not satisfied during power ON/OFF, the internal Power on Reset (POR) circuit will not operate normally.

- 2. During normal operation, if the  $V_{DD}$  drops below the minimum voltage as defined in the operating voltage spec, then the conditions for the Power on Reset timing must also be satisfied. This means that VDD must drop to 0V and remain there for 20ms (min.) before rising to the normal operating voltage.

- 3. Data transfers on the I<sup>2</sup>C-bus or 4-wire serial bus should be avoided for 1 ms following a power-on to allow the reset sequence to complete

# **Functional Description**

#### **Power-on Reset**

After power is applied, the devices will be initialised by an internal power-on reset circuit. The status of the internal circuits after initialisation is as follows:

- · System Oscillator will be off

- COM0~COM7 outputs status is high impedance.

- The row CMOS outputs will all be low

- The LED display will be in an off state

- Dimming is set to 16/16duty

- The Blinking function will be in an off state.

Data transfers on the I<sup>2</sup>C-bus or 4-wire serial bus should be avoided for 1 ms following a power-on to allow the reset initialisation operation to complete.

### **System Oscillator**

The system clock is used to generate the time base clock frequency LED-driving clock. The clock may be sourced from an on-chip 256kHz RC oscillator or from an external clock using software setups. After the SYS DIS command is executed, the system clock will stop and the LED duty cycle generator will turn off. This command is however available only for the on-chip RC oscillator. Once the system clock stops the LED display will become blank and the time base will also stop functioning. The LED OFF command is used to turn the LED duty cycle generator off. After the LED duty cycle generator switches off by issuing the LED OFF command, using the SYS DIS command will reduce the power consumption, allowing it to operate as a system power down command. However if the external clock source is chosen as the system

clock, using the SYS DIS command can neither turn the oscillator off nor execute the power down mode. The crystal oscillator option can also be used where an external frequency source is connected to the OSC pin. In this case, the system will fail to enter the power down mode, similar to the case for the external clock source operation. After an initial system power on, the device will be in the SYS DIS state.

**System Oscillator Configuration**

### **Display Data Address Pointer**

The address mechanism for the display RAM is implemented using the address pointer. This allows the loading of an individual display data byte, or a series of display data bytes, into any location of the display RAM. The sequence commences with the initialisation of the address pointer by the address pointer command.

#### Blinker

The device contains a versatile blinking function. The whole display can be made to flash at frequencies selected by the Blink command. The blinking frequencies are integer multiples of the system frequency. The ratios between the system oscillator and the blinking frequencies depend upon the mode in which the device is operating, as follows:

• Blinking frequency = 2Hz

Example of Waveform for Blinker

#### **Display Memory - RAM Structure**

- The display RAM is a static 88×4-bit RAM which stores the LED data. Logic "1" in the RAM bit-map indicates an "on" state of the corresponding LED Row. Similarly, a logic 0 indicates the "off" state.

- There is a one-to-one correspondence between the RAM addresses and the Row outputs, and between the individual bits of a RAM word and the column outputs. The following shows the mapping from the RAM to the LED pattern:

|      | COM7 | COM6 | COM5 | COM4 |     | COM3 | COM2 | COM1 | COM0 |     |

|------|------|------|------|------|-----|------|------|------|------|-----|

| ROW0 |      |      |      |      | 01H |      |      |      |      | 00H |

| ROW1 |      |      |      |      | 03H |      |      |      |      | 02H |

| ROW2 |      |      |      |      | 05H |      |      |      |      | 04H |

Rev. 1.00 8 July 09, 2021

|       | COM7 | СОМ6      | COM5 | COM4 |      | сомз | COM2 | COM1 | СОМО |      |

|-------|------|-----------|------|------|------|------|------|------|------|------|

| ROW3  |      |           |      |      | 07H  |      |      |      |      | 06H  |

| ROW4  |      |           |      |      | 09H  |      |      |      |      | 08H  |

| ROW5  |      |           |      |      | 0BH  |      |      |      |      | 0AH  |

| ROW6  |      |           |      |      | 0DH  |      |      |      |      | 0CH  |

| ROW7  |      |           |      |      | 0FH  |      |      |      |      | 0EH  |

| ROW8  |      |           |      |      | 11H  |      |      |      |      | 10H  |

| ROW9  |      |           |      |      | 13H  |      |      |      |      | 12H  |

| ROW10 |      |           |      |      | 15H  |      |      |      |      | 14H  |

| ROW11 |      |           |      |      | 17H  |      |      |      |      | 16H  |

| ROW12 |      |           |      |      | 19H  |      |      |      |      | 18H  |

| ROW13 |      |           |      |      | 1BH  |      |      |      |      | 1AH  |

| ROW14 |      |           |      |      | 1DH  |      |      |      |      | 1CH  |

| ROW15 |      |           |      |      | 1FH  |      |      |      |      | 1EH  |

| ROW16 |      |           |      |      | 21H  |      |      |      |      | 20H  |

| ROW17 |      |           |      |      | 23H  |      |      |      |      | 22H  |

| ROW18 |      |           |      |      | 25H  |      |      |      |      | 24H  |

| ROW19 |      |           |      |      | 27H  |      |      |      |      | 26H  |

| ROW20 |      |           |      |      | 29H  |      |      |      |      | 28H  |

| ROW21 |      |           |      |      | 2BH  |      |      |      |      | 2AH  |

| ROW22 |      |           |      |      | 2DH  |      |      |      |      | 2CH  |

| ROW23 |      |           |      |      | 2FH  |      |      |      |      | 2EH  |

| ROW24 |      |           |      |      | 31H  |      |      |      |      | 30H  |

| ROW25 |      |           |      |      | 33H  |      |      |      |      | 32H  |

| ROW26 |      |           |      |      | 35H  |      |      |      |      | 34H  |

| ROW27 |      |           |      |      | 37H  |      |      |      |      | 36H  |

| ROW28 |      |           |      |      | 39H  |      |      |      |      | 38H  |

| ROW29 |      |           |      |      | 3BH  |      |      |      |      | 3AH  |

| ROW30 |      |           |      |      | 3DH  |      |      |      |      | 3CH  |

| ROW31 |      |           |      |      | 3FH  |      |      |      |      | 3EH  |

| ROW32 |      |           |      |      | 41H  |      |      |      |      | 40H  |

| ROW33 |      |           |      |      | 43H  |      |      |      |      | 42H  |

| ROW34 |      |           |      |      | 45H  |      |      |      |      | 44H  |

| ROW35 |      |           |      |      | 47H  |      |      |      |      | 46H  |

| ROW36 |      |           |      |      | 49H  |      |      |      |      | 48H  |

| ROW37 |      |           |      |      | 4BH  |      |      |      |      | 4AH  |

| ROW38 |      |           |      |      | 4DH  |      |      |      |      | 4CH  |

| ROW39 |      |           |      |      | 4FH  |      |      |      |      | 4EH  |

| ROW40 |      |           |      |      | 51H  |      |      |      |      | 50H  |

| ROW41 |      |           |      |      | 53H  |      |      |      |      | 52H  |

| ROW42 |      |           |      |      | 55H  |      |      |      |      | 54H  |

| ROW43 |      |           |      |      | 57H  |      |      |      |      | 56H  |

|       | D3   | D2        | D1   | D0   | Addr | D3   | D2   | D1   | D0   | Addr |

|       | ■    | <i>D2</i> | D I  |      | Data | ■    | D2   |      |      | Data |

44ROW & 8COM for 88 × 4 Display RAM

Note: 1.The LED display RAM address is specified by the Address Set command. The address will be automatically incremented by one after the 4-bit data is shifted in.

2. It is recommended to initialize the display RAM data by clearing all RAM data before the LED display function is activated. If the RAM data is not initialized before enabling the LED display function, it may result in abnormal LED display effect after executing the LED ON command.

Rev. 1.00 9 July 09, 2021

### **LED Driver**

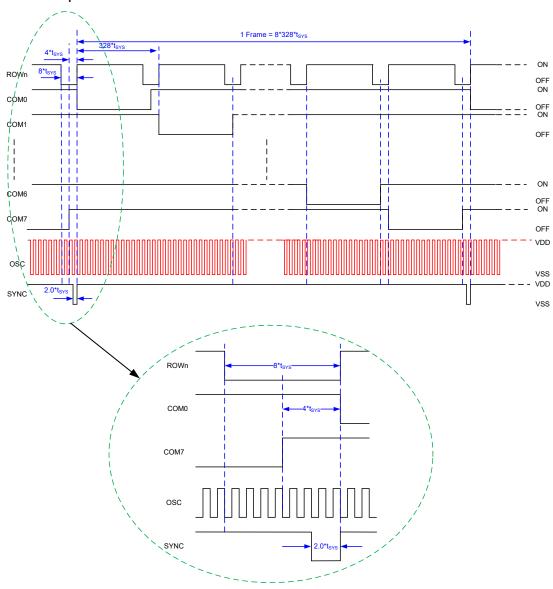

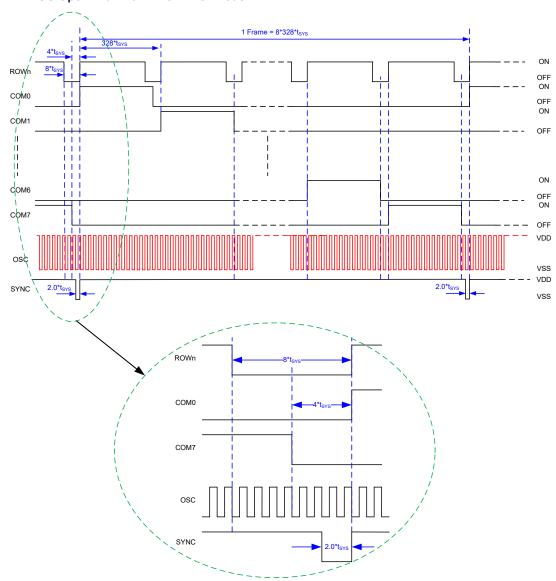

The devices include a 352  $(44\times8)$  pattern LED driver. This can be setup in a 44x8 format where the COM outputs can be configured as N-MOS open drain outputs or as P-MOS open drain outputs using software setups. This feature allows the device to be used in multiple LED applications. The LED drive mode waveforms and scanning is as follows:

# 1. N-MOS Open Drain for 44×8 Driver Mode

Note:  $t_{SYS}=1/f_{SYS}$

# 2. P-MOS Open Drain for 44×8 Driver Mode

Note:  $t_{SYS}=1/f_{SYS}$

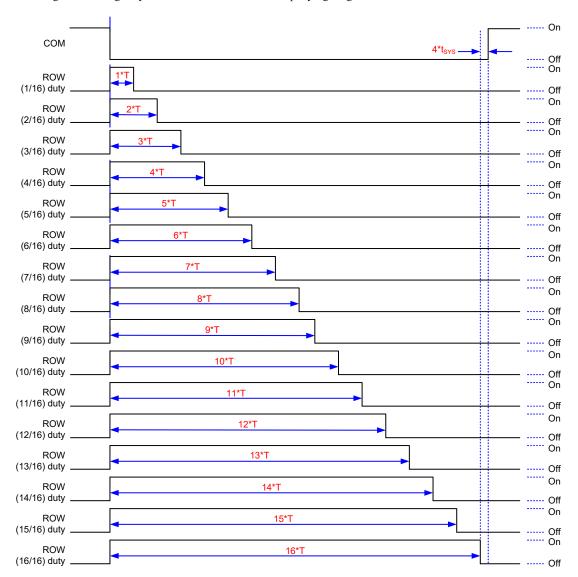

### **Digital Dimming**

The devices contain versatile dimming functions. The complete display can be dimmed using pulse width modulation techniques for the ROW driver with the Dimming command. The relationship between the ROW and COM digital dimming duty times are shown in the accompanying diagram.

Note:  $T=20 \times t_{SYS}$  $t_{SYS}=1/f_{SYS}$

# 4-wire Serial Interface

#### **Command Format**

Software setups are used to configure the devices. There are two mode commands to configure the device resources and to transfer the LED display data. The configurations are setup using the command mode which has a command mode ID of 100. The command mode consists of a system configuration command, a system frequency selection command, an LED configuration command and an operating command. The data mode includes READ, WRITE, and READ-MODIFY-WRITE operations.

The accompanying table shows the data and command mode IDs.

| Operation         | Mode    | ID  |

|-------------------|---------|-----|

| Read              | Data    | 110 |

| Write             | Data    | 101 |

| Read-Modify-Write | Data    | 101 |

| Command           | Command | 100 |

The mode command should be issued before any data or other commands are transferred. If successive commands have been issued, the command mode ID, namely 100, can be omitted. While the system is operating in the non-successive command or the non-successive address data mode, the CSB pin should be set to "1" and the previous operation mode will be reset also. Once the CSB pin returns to "0", a new operation mode ID should be issued first.

### Interfacing

Only four lines are required to interface to the HT1635C. The CSB line is used to initialise the serial interface circuit and to terminate the communication between the host controller and the device. If the CSB pin is set high, the data and command issued between the host controller and the device are first disabled and then initialised. Before issuing a mode command or before mode switching, a high level pulse is required to initialise the device serial interface. The DATA line is the serial data input/output line. Data to be read or written or commands to be written have to be transferred on the DATA line. The RDB line is the READ clock input. Data in the RAM is clocked out on the falling edge of the RDB signal and will appear on the DATA line. It is recommended that the host controller read in the correct data during the interval between the rising edge and the next falling edge of the RDB signal. The WRB line is the WRITE clock input. The data, address, and command on the DATA line are all clocked into the device on the rising edge of the WRB signal.

### 4-Wire Timing Diagram

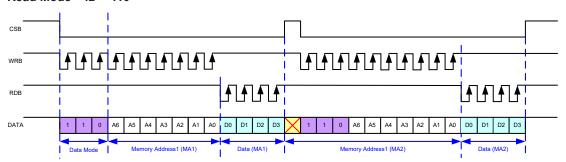

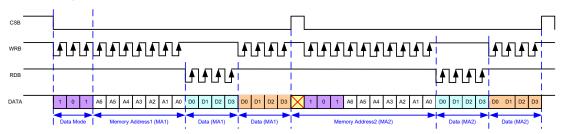

#### Read Mode - ID = 110

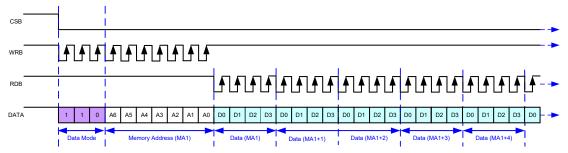

### Read Mode - Successive Address Reading

Note: After reaching the display memory location 0X57H the pointer will reset to 0X00H.

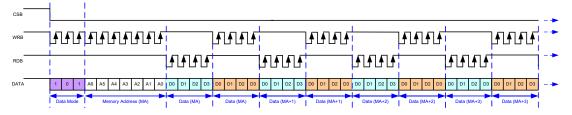

#### Write Mode - ID = 101

### Write Mode - Successive Address Writing

Note: After reaching the display memory location 0X57H the pointer will reset to 0X00H.

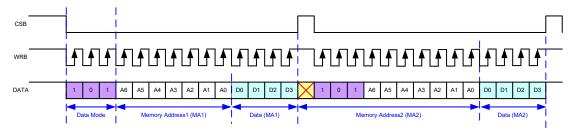

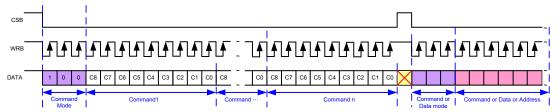

#### Read-Modify-Write Mode - ID = 101

### Read-Modify-Write Mode - Successive Address Accessing

Rev. 1.00 14 July 09, 2021

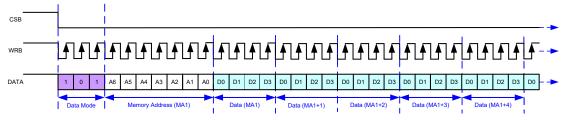

#### Command Mode - ID = 100

# Mode - Data and Command Mode

# 4-wire Serial Bus Command Summary

| Name                    | ID  | Command code           | D/C | Function                                                                                                                                                                                   | Def. |

|-------------------------|-----|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Read                    | 110 | A6A5A4A3A2A1A0D0D1D2D3 | D   | Read data from the RAM                                                                                                                                                                     |      |

| Write                   | 101 | A6A5A4A3A2A1A0D0D1D2D3 | D   | Write data to the RAM                                                                                                                                                                      |      |

| Read-Modify-Write       | 101 | A6A5A4A3A2A1A0D0D1D2D3 | D   | READ and WRITE to the RAM                                                                                                                                                                  |      |

| SYS DIS                 | 100 | 0000-0000-X            | С   | Turn off both system oscillator and LED duty cycle generator                                                                                                                               | Yes  |

| SYS EN                  | 100 | 0000-0001-X            | С   | Turn on system oscillator                                                                                                                                                                  |      |

| LED OFF                 | 100 | 0000-0010-X            | С   | Turn off LED duty cycle generator                                                                                                                                                          | Yes  |

| LED ON                  | 100 | 0000-0011-X            | С   | Turn on LED duty cycle generator                                                                                                                                                           |      |

| Blink OFF               | 100 | 0000-1000-X            | С   | Turn off blinking function                                                                                                                                                                 | Yes  |

| Blink_ON_2Hz            | 100 | 0000-1001-X            | С   | Turn on 2Hz blinking function                                                                                                                                                              |      |

| Blink_ON_1Hz            | 100 | 0000-1010-X            | С   | Turn on 1Hz blinking function                                                                                                                                                              |      |

| Blink_ON_0.5Hz          | 100 | 0000-1011-X            | С   | Turn on 0.5Hz blinking function                                                                                                                                                            |      |

| Slave Mode              | 100 | 0001-0XXX-X            | С   | Slave mode     Clock source from external clock     System clock input is on the OSC pin     Synchronous signal input is on the SYNC pin                                                   |      |

| RC<br>Master Mode0      | 100 | 0001-100X-X            | С   | Master mode     Clock source from on-chip RC oscillator     OSC pin remains low     SYNC pin remains high     Single chip application only                                                 | Yes  |

| RC<br>Master Mode1      | 100 | 0001-101X-X            | С   | Master mode     Clock source from on-chip RC oscillator     System clock output on the OSC pin     Synchronous signal output on the SYNC pin                                               |      |

| EXT CLK<br>Master Mode0 | 100 | 0001-110X-X            | С   | <ul> <li>Master mode</li> <li>Clock source from external clock,</li> <li>System clock input on the OSC pin</li> <li>SYNC pin remains high</li> <li>Single chip application only</li> </ul> |      |

| EXT CLK<br>MASTER MODE1 | 100 | 0001-111X-X            | С   | Master mode     Clock source from external clock     System clock input on the OSC pin     Synchronous signal output on the SYNC pin                                                       |      |

Note: It is not recommended to change between MASTER and SLAVE mode after system enable (SYS\_EN=1).

| Name          | ID  | Command code | D/C | Function                                                        | Def. |

|---------------|-----|--------------|-----|-----------------------------------------------------------------|------|

| COM OPTION    | 100 | 0010-aXXX-X  | С   | Bit "a" : Open drain type selection<br>a=0: N-MOS<br>a=1: P-MOS | a=0  |

|               | 100 | 101X-0000-X  | С   | PWM 1/16 Duty                                                   |      |

|               | 100 | 101X-0001-X  | С   | PWM 2/16 Duty                                                   |      |

|               | 100 | 101X-0010-X  | С   | PWM 3/16 Duty                                                   |      |

|               | 100 | 101X-0011-X  | С   | PWM 4/16 Duty                                                   |      |

|               | 100 | 101X-0100-X  | С   | PWM 5/16 Duty                                                   |      |

|               | 100 | 101X-0101-X  | С   | PWM 6/16 Duty                                                   |      |

|               | 100 | 101X-0110-X  | С   | PWM 7/16 Duty                                                   |      |

| DIA/NA Dustra | 100 | 101X-0111-X  | С   | PWM 8/16 Duty                                                   |      |

| PWM Duty      | 100 | 101X-1000-X  | С   | PWM 9/16 Duty                                                   |      |

|               | 100 | 101X-1001-X  | С   | PWM 10/16 Duty                                                  |      |

|               | 100 | 101X-1010-X  | С   | PWM 11/16 Duty                                                  |      |

|               | 100 | 101X-1011-X  | С   | PWM 12/16 Duty                                                  |      |

|               | 100 | 101X-1100-X  | С   | PWM 13/16 Duty                                                  |      |

|               | 100 | 101X-1101-X  | С   | PWM 14/16 Duty                                                  |      |

|               | 100 | 101X-1110-X  | С   | PWM 15/16 Duty                                                  |      |

|               | 100 | 101X-1111-X  | С   | PWM 16/16 Duty                                                  | Yes  |

Note: 1. X: Don't care

2. A7~A0: RAM addresses 3. D3~D0: RAM data

4. D/C: Data/command mode5.Def.: Power on reset default

6. All the bold forms, namely 110, 101, and 100, are mode commands. Among these, 100 indicates the command mode ID. If successive commands have been issued, the command mode ID except for the first command will be omitted. The source of the tone frequency and of the time base clock frequency can be derived from an on-chip RC oscillator or an external clock. Calculation of the frequency is based on the system frequency sources as stated above. It is recommended that the host controller should initialise the device after a power on reset, as if the power on reset fails, this will lead to device malfunction.

Rev. 1.00 16 July 09, 2021

### I<sup>2</sup>C Serial Interface

The HT1635D includes an I<sup>2</sup>C serial interface. The I<sup>2</sup>C bus is a bidirectional, two-line communication link between different ICs or modules. The two lines are a serial data line, SDA, and a serial clock line, SCL. Both lines are connected to a positive supply via a pull-up resistor. When the bus is free both lines are high. The output stages of devices connected to the bus must have open-drain or open-collector types in order to implement a wired or function. Data transfer is initiated only when the bus is not busy.

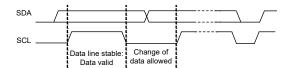

### **Data Validity**

The data on the SDA line must be stable during the high period of the clock. The high or low state of the data line can only change when the clock signal on the SCL line is low as shown in the accompanying diagram.

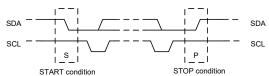

#### **START And STOP Conditions**

- A high to low transition on the SDA line while SCL is high defines a START condition.

- A low to high transition on the SDA line while SCL is high defines a STOP condition.

- START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition.

- The bus stays busy if a repeated START(Sr) is generated instead of a STOP condition. The START(S) and repeated START(Sr) conditions are functionally identical.

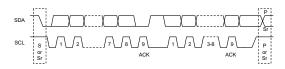

#### Byte Format

Every byte put on the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first.

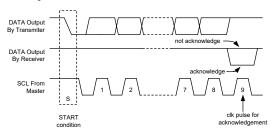

### **Acknowledge**

- Each byte of eight bit length is followed by one acknowledge bit. This acknowledge bit is a low level placed on the bus by the receiver. The master generates an extra acknowledge related clock pulse.

- A slave receiver which is addressed must generate an acknowledge, ACK, after the reception of each byte.

- The device that provides an acknowledge must pull down the SDA line during the acknowledge clock pulse so that it remains at a stable low level during the high period of this clock pulse.

- A master receiver must signal an end of data to the slave by generating a not-acknowledge, NACK, bit on the last byte that has been clocked out of the slave. In this case, the master receiver must leave the data line high during the 9th pulse so as to not acknowledge. The master will generate a STOP or a repeated START condition.

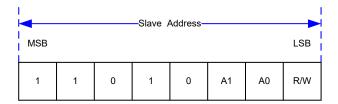

## **Slave Addressing**

- The device requires an 8-bit slave address word following a start condition to enable the chip for a write operation. The device address words consist of a mandatory one, zero sequence for the first four most significant bits. Refer to the diagram showing the slave Address. This is common to all LED devices.

- The slave address byte is the first byte received following the START condition from the master device. The first seven bits of the first byte make up the slave address. The eighth bit defines whether a read or write operation is to be performed. When the R/W bit is "1", then a read operation is selected. A "0" selects a write operation.

- The address bits are "1, 1, 0, 1, 0, A1, A0". When

an address byte is sent, the device compares the

first seven bits after the START condition. If they

match, the device outputs an Acknowledge on the

SDA line.

Rev. 1.00 17 July 09, 2021

# I<sup>2</sup>C Timing Diagram

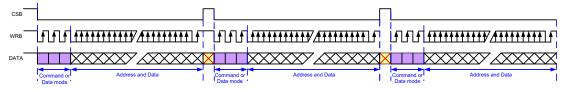

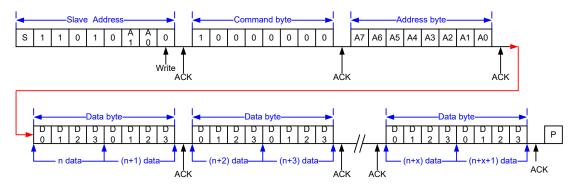

#### Write Operation - Command Byte

Byte write operation requires a START condition, slave address with R/W bit, a command (1st), a register byte command (2nd) and a STOP condition for the command byte.

### Write Operation - Write Display RAM Single Data Byte

A display RAM data byte write operation requires a START condition, a slave address with a write control bit, a valid display data input /output command, Address byte, a Data byte and a STOP condition.

# Write Operation - Page Write Display Data Operation

Following a START condition, the slave address together with the R/W bit is placed on the bus. The addressed device will then be provided with an address, which is the address pointer where the data is to be written. The data to be written then follows after which the internal address pointer is incremented to the next address location on the reception of an acknowledge clock. After reaching the display memory location 0X57H the pointer will reset to 0X00H

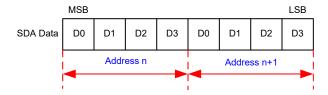

Note: The relationship between the LED Display Input/ Output Data transfer format and the RAM mapping data format is shown below.

Rev. 1.00 18 July 09, 2021

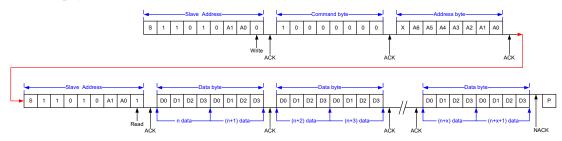

#### Read Operation - Read Display Data Operation

In this mode, the master reads the device data after setting the slave address. Following the R/W bit, which is zero, and the acknowledge bit, then follows the display data address setting command code (1st). After this is the address pointer (An) which is written to the address pointer (2nd). Next comes the START condition and slave address, followed by an R/W bit which is high. The data which was addressed is then transmitted. The address pointer is only incremented on reception of an acknowledge clock. The device will place the data at address An+1 onto the bus. The master reads and acknowledges the new byte and the address pointer is incremented to "An+2".

- If the memory location exceeds the limit value of 0X57H, the memory pointer will return to 00H.

- If only a read command is sent to the I<sup>2</sup>C interface, then dummy data is sent out.

- This cycle for reading consecutive addresses will continue until the master sends a NACK and STOP condition.

- · Read display data format

### I<sup>2</sup>C Bus Command Summary

#### **Display Data Input Command**

This command sends data from the MCU to the device memory map.

| Function                              | Byte | (MSB)<br>Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | (LSB)<br>Bit0 | Note                                          | R/W | Def |

|---------------------------------------|------|---------------|------|------|------|------|------|------|---------------|-----------------------------------------------|-----|-----|

| Display Data Input/<br>output command | 1st  | 1             | 0    | 0    | 0    | 0    | 0    | 0    | 0             |                                               | W   |     |

| Address pointer                       | 2nd  | Х             | A6   | A5   | A4   | A3   | A2   | A1   | A0            | Displays data start address of the memory map | W   | 00H |

#### Note:

- Power on status: the address is set to 00H.

- If the programmed command is not defined the function will not be affected

#### **System Mode Command**

This command controls the system oscillator on/off and display on/off.

| Function                                     | Byte | (MSB)<br>Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | (LSB)<br>Bit0 | Note | R/W | Def |

|----------------------------------------------|------|---------------|------|------|------|------|------|------|---------------|------|-----|-----|

| System mode setting command                  | 1st  | 1             | 0    | 0    | 0    | 0    | 0    | 1    | 0             |      | W   |     |

| System oscillator and display on/off setting | 2nd  | Х             | Х    | Х    | Х    | Х    | Х    | P1   | P0            |      | W   | 00H |

#### Note:

| Name                | В  | Bit | System Ossillator | I ED Dienley |

|---------------------|----|-----|-------------------|--------------|

| Name                | P1 | P0  | System Oscillator | LED Display  |

| SYS DIS and LED off | 0  | X   | Off               | Off          |

| SYS EN and LED off  | 1  | 0   | On                | Off          |

| SYS EN and LED on   | 1  | 1   | On                | On           |

- Power on status: Display off and disable the internal system oscillator.

- If the programmed command is not defined, the function will not be affected.

Rev. 1.00 19 July 09, 2021

## **Blinking Frequency Command**

This command defines the blinking frequency of the display modes.

| Function                   | Byte | (MSB)<br>Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | (LSB)<br>Bit0 | Note | R/W | Def |

|----------------------------|------|---------------|------|------|------|------|------|------|---------------|------|-----|-----|

| Blinking frequency command | 1st  | 1             | 0    | 0    | 0    | 0    | 1    | 0    | 0             |      | W   |     |

| Blinking frequency setting | 2nd  | Х             | Х    | Х    | Х    | Х    | Х    | P1   | P0            |      | W   | 00H |

#### Note:

|    | Bit | Blinking Francisco |

|----|-----|--------------------|

| P1 | P0  | Blinking Frequency |

| 0  | 0   | Blinking off       |

| 0  | 1   | 2Hz                |

| 1  | 0   | 1Hz                |

| 1  | 1   | 0.5Hz              |

- Power on status: Blinking function is switched off.

- If the programmed command is not defined, the function will not be affected.

### **COM Option Command**

| Function                             | Byte | (MSB)<br>Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | (LSB)<br>Bit0 | Note | R/W | Def |

|--------------------------------------|------|---------------|------|------|------|------|------|------|---------------|------|-----|-----|

| Driver output of COM setting command | 1st  | 1             | 0    | 0    | 0    | 1    | 0    | 0    | 0             |      | W   |     |

| COM pin option setting               | 2nd  | Х             | Х    | Х    | Х    | Х    | Х    | Х    | P0            |      | W   | 00H |

#### Note:

| Bit | COM pin open drain type selection |  |  |  |  |  |  |

|-----|-----------------------------------|--|--|--|--|--|--|

| P0  | com pin open drain type selection |  |  |  |  |  |  |

| 0   | N-MOS                             |  |  |  |  |  |  |

| 1   | P-MOS                             |  |  |  |  |  |  |

- Power on status: The COM N-MOS open drain output is setup.

- If the programmed command is not defined the function will not be affected.

### **Cascade Set Mode Command**

This command will select master/slave mode and input clock source.

| Function                                            | Byte | (MSB)<br>Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | (LSB)<br>Bit0 | Note | R/W | Def |

|-----------------------------------------------------|------|---------------|------|------|------|------|------|------|---------------|------|-----|-----|

| Cascade set mode command                            | 1st  | 1             | 0    | 1    | 0    | 0    | 0    | 0    | 0             |      | W   |     |

| Master/ slave select and input clock source setting | 2nd  | Х             | Х    | х    | Х    | х    | P2   | P1   | P0            |      | W   | 04H |

### Note:

| Name                    |    | Bit |    | Master/Slave | Input Clock     | OSC pin     | Sync pin              | Note                         |

|-------------------------|----|-----|----|--------------|-----------------|-------------|-----------------------|------------------------------|

| Ivaille                 | P2 | P1  | P0 | Select       | Source          | Status      | Status                | Note                         |

| RC<br>Master Mode0      | 1  | 0   | 0  | Master mode  | On Chip RC      | Output Hi-Z | Always<br>Output high | Only single chip application |

| RC<br>Master Mode1      | 1  | 0   | 1  | Master mode  | Oscillator      | Output      | Output                |                              |

| EXT CLK<br>Master Mode0 | 1  | 1   | 0  | Master mode  | External        | Input       | Always<br>Output high | Only single chip application |

| EXT CLK<br>Master Mode1 | 1  | 1   | 1  | Master mode  | OSC             | Input       | Output                |                              |

| Slave Mode              | 0  | Х   | Х  | Slave mode   | External<br>OSC | Input       | Input                 |                              |

- Power on status: The RC MASTER MODE0 is selected.

- It is not recommended to change between MASTER and SLAVE mode after a system enable (SYS\_EN=1)

- If the programmed command is not defined the function will not be affected.

# **PWM Duty Command**

This command controls the row pulse width.

| Function                   | Byte | (MSB)<br>Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | (LSB)<br>Bit0 | Note | R/W | Def |

|----------------------------|------|---------------|------|------|------|------|------|------|---------------|------|-----|-----|

| PWM setting command        | 1st  | 1             | 1    | 0    | 0    | 0    | 0    | 0    | 0             |      | W   |     |

| Pulse width of ROW setting | 2nd  | Х             | Х    | Х    | Х    | P3   | P2   | P1   | P0            |      | W   | 0FH |

Note:

|    | В  |    | PWM duty |              |

|----|----|----|----------|--------------|

| P3 | P2 | P1 | P0       | P VVIVI duty |

| 0  | 0  | 0  | 0        | 1/16         |

| 0  | 0  | 0  | 1        | 2/16         |

| 0  | 0  | 1  | 0        | 3/16         |

| 0  | 0  | 1  | 1        | 4/16         |

| 0  | 1  | 0  | 0        | 5/16         |

| 0  | 1  | 0  | 1        | 6/16         |

| 0  | 1  | 1  | 0        | 7/16         |

| 0  | 1  | 1  | 1        | 8/16         |

| 1  | 0  | 0  | 0        | 9/16         |

| 1  | 0  | 0  | 1        | 10/16        |

| 1  | 0  | 1  | 0        | 11/16        |

| 1  | 0  | 1  | 1        | 12/16        |

| 1  | 1  | 0  | 0        | 13/16        |

| 1  | 1  | 0  | 1        | 14/16        |

| 1  | 1  | 1  | 0        | 15/16        |

| 1  | 1  | 1  | 1        | 16/16        |

Rev. 1.00 21 July 09, 2021

<sup>Power on status: 16/16 PWM duty is selected.

If the programmed command is not defined the function will not be affected.</sup>

# **Application Circuits**

# **LED Matrix Circuit**

Rev. 1.00 22 July 09, 2021

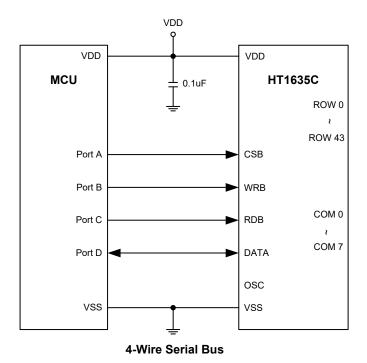

# **Communication Bus Type Circuit**

The deivce are compatible with most microcontrollers and communicates using two serial interfaces, an I<sup>2</sup>C bus or a 4-wire serial bus.

VDD VDD VDD MCU HT1635D 0.1uF 4.7kΩ≶ ROW 0 ROW 43 SCL Port A Port B SDA Port C A0 COM 0 Port D Α1 COM 7 osc VSS VSS I<sup>2</sup>C Serial Bus

Rev. 1.00 23 July 09, 2021

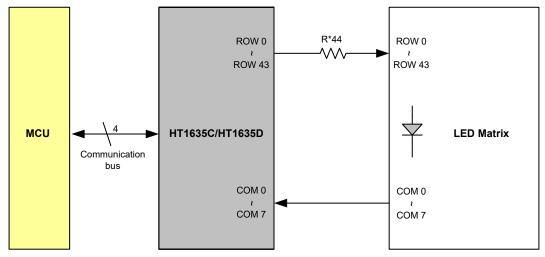

### Low Power LED Application – Direct Drive

### 44 ROW × 8 COM Example: N-MOS Open Drain Output

Note: 1. Values of the R resistors are selected depending on the power consumption of the LEDs.

- 2. In PCB Layout that must connect all of the VDD pins to the power plane.

- 3. In PCB Layout that must connect all of the VSS pins to the GND plane.

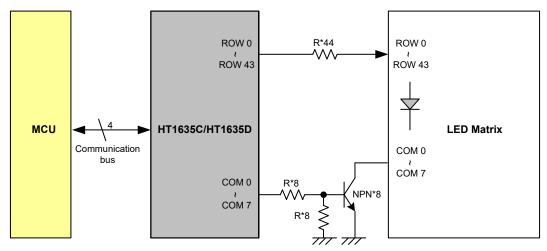

# **High Power LED Application – COM with Transistor Buffer**

# 44 ROW × 8 COM Example – P-MOS Open Drain Output and 8 COM Option

Note: 1. Values of the R resistors are selected depending on the power consumption of the LEDs.

- 2. In PCB Layout that must connect all of the VDD pins to the power plane.

- 3. In PCB Layout that must connect all of the VSS pins to the GND plane.

Rev. 1.00 24 July 09, 2021

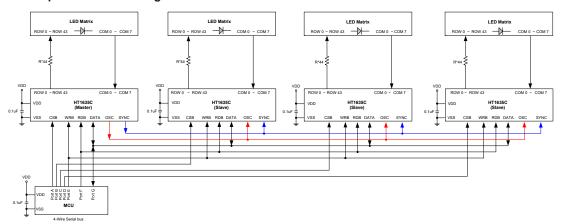

# **Cascade Function**

Low Power LED Application – In the Case, the COM Pins Output Must be Set to N-MOS Open Drain Outputs

### • Example 1: Direct Driving for 4-wire Serial Bus

Note: 1. Cascading can also be implemented using software. Users must set the Master in the master mode and the Slave in the slave mode using the commands. The CSB pin must be connected to the MCU individually for independent read and write.

- 2. Values of the R resistors are selected depending on the power consumption of the LEDs.

- 3. In PCB Layout that must connect all of the VDD pins to the power plane.

- 4. In PCB Layout that must connect all of the VSS pins to the GND plane.

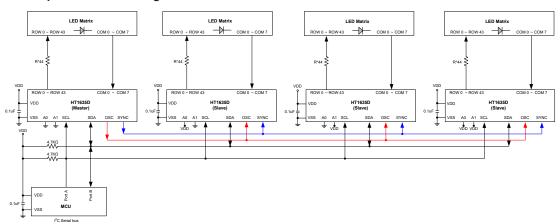

# • Example 2: Direct Driving for I<sup>2</sup>C Serial Bus

Note: 1.Cascading can also be implemented using software. Users must set the Master in the master mode and the Slave in the slave mode using the commands. The CSB pin must be connected to the MCU individually for independent read and write.

- 2. Values of the R resistors are selected depending on the power consumption of the LEDs.

- 3. In PCB Layout that must connect all of the VDD pins to the power plane.

- 4. In PCB Layout that must connect all of the VSS pins to the GND plane.

Rev. 1.00 25 July 09, 2021

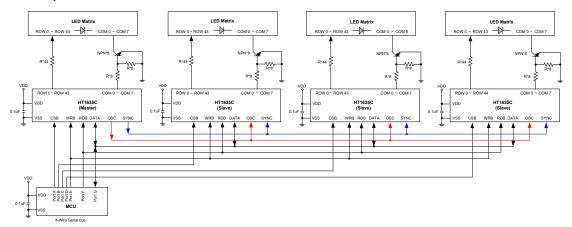

High Power LED Application – In the Case, the COM Pins Output Must be Set to P-MOS Open Drain Outputs.

#### Example 1: COM with Transistor Buffer for 4-wire Serial Bus

- Note: 1. Cascading can also be implemented using software. Users must set the Master in the master mode and the Slave in the slave mode using the commands. The CSB pin must be connected to the MCU individually for independent read and write.

- 2. Values of the R resistors are selected depending on the power consumption of the LEDs.

- 3. In PCB Layout that must connect all of the VDD pins to the power plane.

- 4. In PCB Layout that must connect all of the VSS pins to the GND plane.

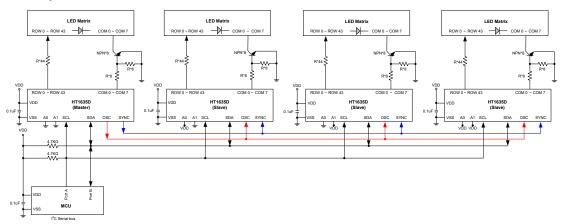

## • Example 2: COM with Transistor Buffer for I<sup>2</sup>C Serial Bus

- Note: 1. Cascading can also be implemented using software. Users must set the Master in the master mode and the Slave in the slave mode using the commands. The CSB pin must be connected to the MCU individually for independent read and write.

- 2. Values of the R resistors are selected depending on the power consumption of the LEDs.

- 3. In PCB Layout that must connect all of the VDD pins to the power plane.

- 4. In PCB Layout that must connect all of the VSS pins to the GND plane.

Rev. 1.00 26 July 09, 2021

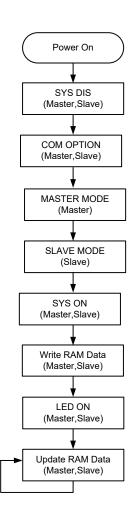

# **Cascade Control Flow**

# **Package Information**

Note that the package information provided here is for consultation purposes only. As this information may be updated at regular intervals users are reminded to consult the <u>Holtek website</u> for the latest version of the <u>Package/Carton Information</u>.

Additional supplementary information with regard to packaging is listed below. Click on the relevant section to be transferred to the relevant website page.

- Further Package Information (include Outline Dimensions, Product Tape and Reel Specifications)

- Packing Meterials Information

- Carton information

Rev. 1.00 28 July 09, 2021

# 64-pin LQFP (7mm×7mm) Outline Dimensions

| Symbol | Dimensions in inch |           |       |

|--------|--------------------|-----------|-------|

|        | Min.               | Nom.      | Max.  |

| Α      | _                  | 0.354 BSC | _     |

| В      | _                  | 0.276 BSC | _     |

| С      | _                  | 0.354 BSC | _     |

| D      | _                  | 0.276 BSC | _     |

| E      | _                  | 0.016 BSC | _     |

| F      | 0.005              | 0.007     | 0.009 |

| G      | 0.053              | 0.055     | 0.057 |

| Н      | _                  | _         | 0.063 |

| I      | 0.002              | _         | 0.006 |

| J      | 0.018              | 0.024     | 0.030 |

| K      | 0.004              | _         | 0.008 |

| α      | 0°                 | _         | 7°    |

| Symbol | Dimensions in mm |          |      |

|--------|------------------|----------|------|

|        | Min.             | Nom.     | Max. |

| A      | _                | 9.00 BSC | _    |

| В      | _                | 7.00 BSC | _    |

| С      | _                | 9.00 BSC | _    |

| D      | _                | 7.00 BSC | _    |

| E      | _                | 0.40 BSC | _    |

| F      | 0.13             | 0.18     | 0.23 |

| G      | 1.35             | 1.40     | 1.45 |

| Н      | _                | _        | 1.60 |

| I      | 0.05             | _        | 0.15 |

| J      | 0.45             | 0.60     | 0.75 |

| K      | 0.09             | _        | 0.20 |

| α      | 0°               | _        | 7°   |

Rev. 1.00 29 July 09, 2021

# Copyright<sup>©</sup> 2021 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.

Rev. 1.00 30 July 09, 2021

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LED Display Drivers category:

Click to view products by Holtek manufacturer:

Other Similar products are found below:

ISL97631IHTZ-T7A ISL97632IRT26Z-T LV5026MC-AH AW9110CQNR AiP650EOSA16.TR MEL7140PG-N PT4115-MS

OB5682MWUPA-H OB5682MMKP-H RY7614 SL401 TM1637(TA2007) TM1648A TM5020A TM1640B(TA1902) TM1812B

TM1620(TA1323C) WS2811F AW36402DNR HT1635D OB3655MP OB2578TCPA OB2365PCPA OB2201TCPA OB3619ETJPA-H

OB3335TJPA-J OB3600CPA OB2500NCP OB3652NCPA-V OB3652NCPA OB3652MCPA-H OB3635ENCPA OB2225NCPA-P

OB5284CCPA OB3635ERCPA-H OB2365TCPA OB3639BCPA OB2281AMP-C OB5283CPA OB3398MP OB3338CPA RH6618T

LYT3315D BCR420U SCT2001ASIG SCT2024CSSG SCT2024CSTG SCT2167CSSG STP16CPPS05XTTR AL8400QSE-7