## Description

The AL8891Q is an automotive compliant single chip with integrated MOSFETs synchronous step-down LED driver, high-side current sense capable of driving up to 2A constant current with input voltage range from 4.5V to 65V. The AL8891Q provides high switching frequency up to 2.5MHz to optimize high efficiency, allowing a smaller inductor size and compact form factor solution. Pin arrangement allows simple, optimum PCB layout. Constant on time adaptive control is employed to achieve simple control-loop compensation and cycle-by-cycle current limiting with fast dynamic response and fixed frequency.

Features such as fault flag, PWM support, analog and hybrid dimming, internal soft-start, and shutdown provide a flexible and easy-to-use platform for a wide range of applications.

Protection features include thermal shutdown, VIN and VCC undervoltage lockout, cycle-by-cycle current limit, output open & short-circuit protection for LED, and external components open & short protection.

The AL8891Q device is available in the enhanced thermal TSSOP-16EP package.

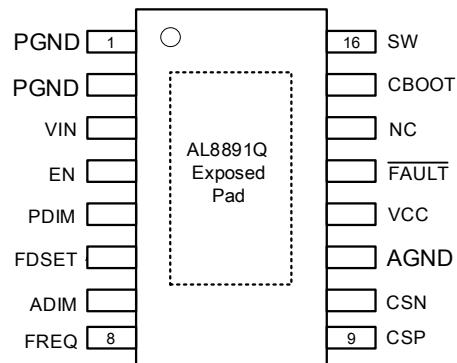

## Pin Assignments

(3D Step file available)

### Top View – (Not to Scale)

TSSOP-16EP

## Features

- AEC-Q100 Grade 1

- Input Voltage 4.5V to 65V

- V<sub>OUT</sub> Close to VIN Rail (up to 99% Duty Cycle)

- Integrated MOSFETs High-Side 200mΩ and Low-Side 130mΩ

- 2A Constant Output Current

- High-Side Current Sense

- Support PWM, Analog and Hybrid Dimming

- Hybrid Dimming < 0.01% Resolution

- Combine Analog (20%) and PWM (0.05% to 5%)

- CISPR25 Class 5 with Frequency Spread Spectrum Built-In

- Internal Compensation Without External Capacitor

- Cycle-by-Cycle Current Protection

- Diagnosis and Fault Flag Indicator

- LED Open and Short Protection

- Overtemperature Thermal Protection and Auto-Restart

- Ambient Temperature -40°C to +125°C

- Thermally Enhanced TSSOP-16EP Package

- **Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)**

- **Halogen and Antimony Free. "Green" Device (Note 3)**

- **The AL8891Q is suitable for automotive applications requiring specific change control; this part is AEC-Q100 qualified, PPAP capable, and manufactured in IATF16949 certified facilities.**

<https://www.diodes.com/quality/product-definitions/>

Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See <https://www.diodes.com/quality/lead-free/> for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

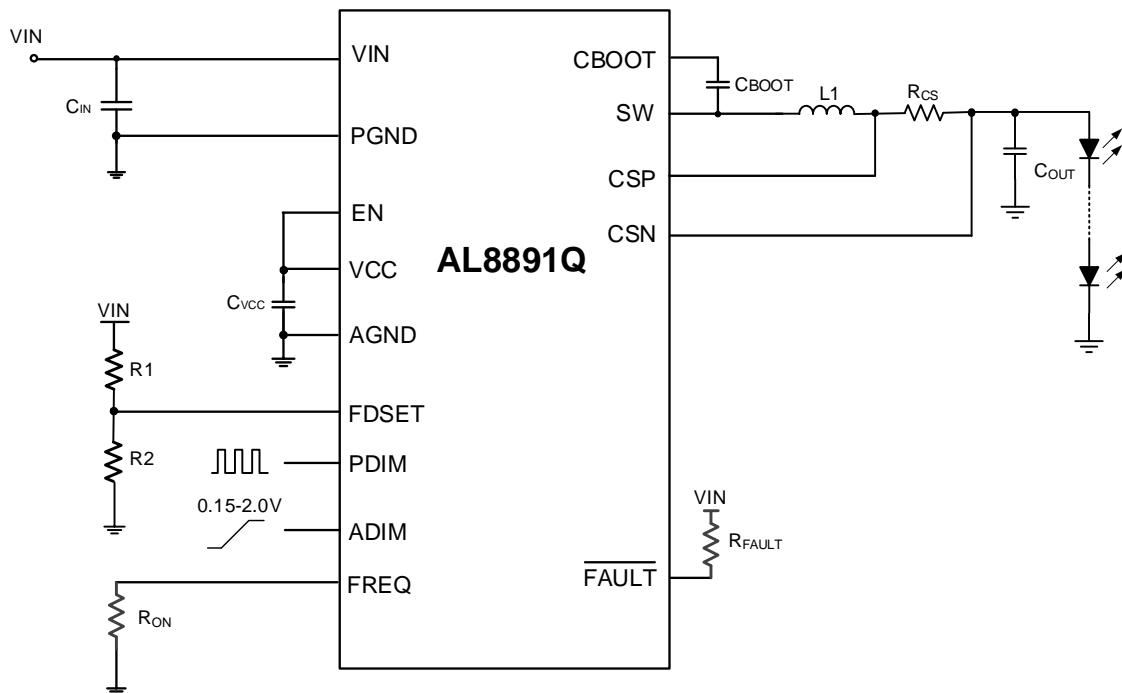

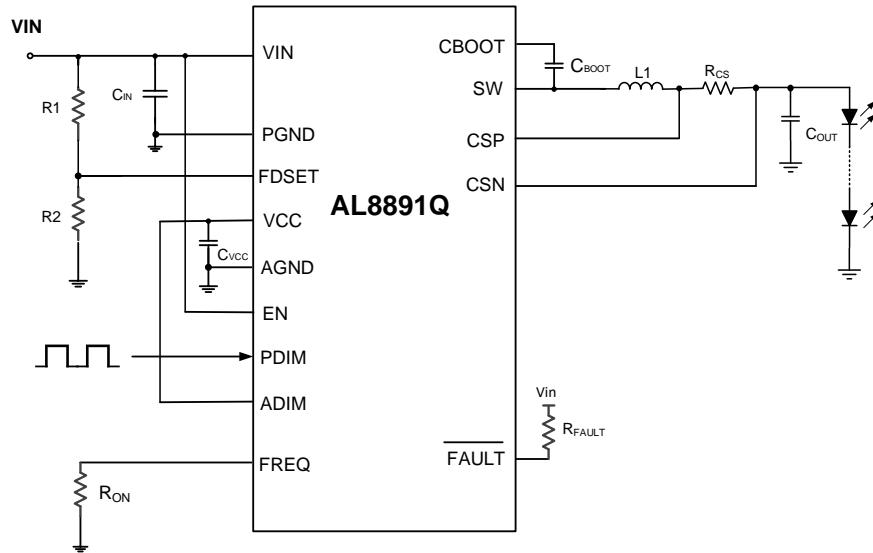

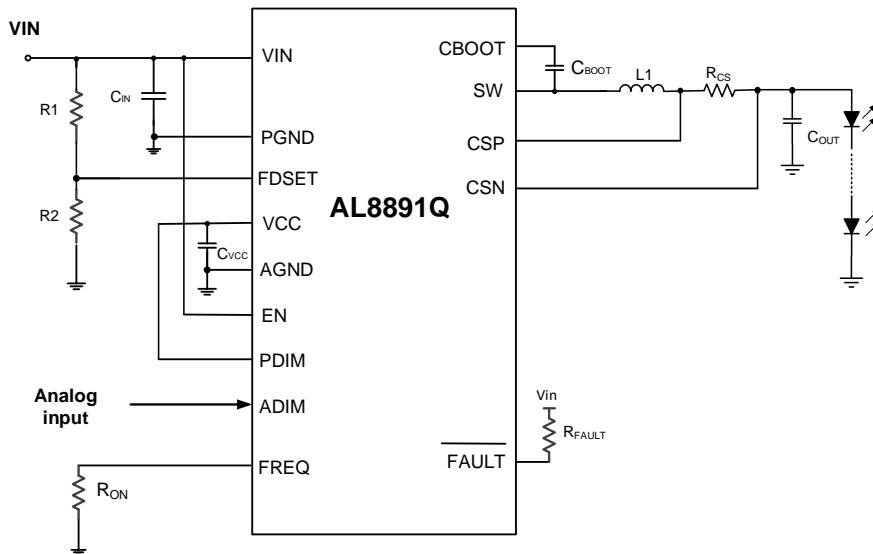

## Typical Applications Circuit

Figure 1. Typical Application

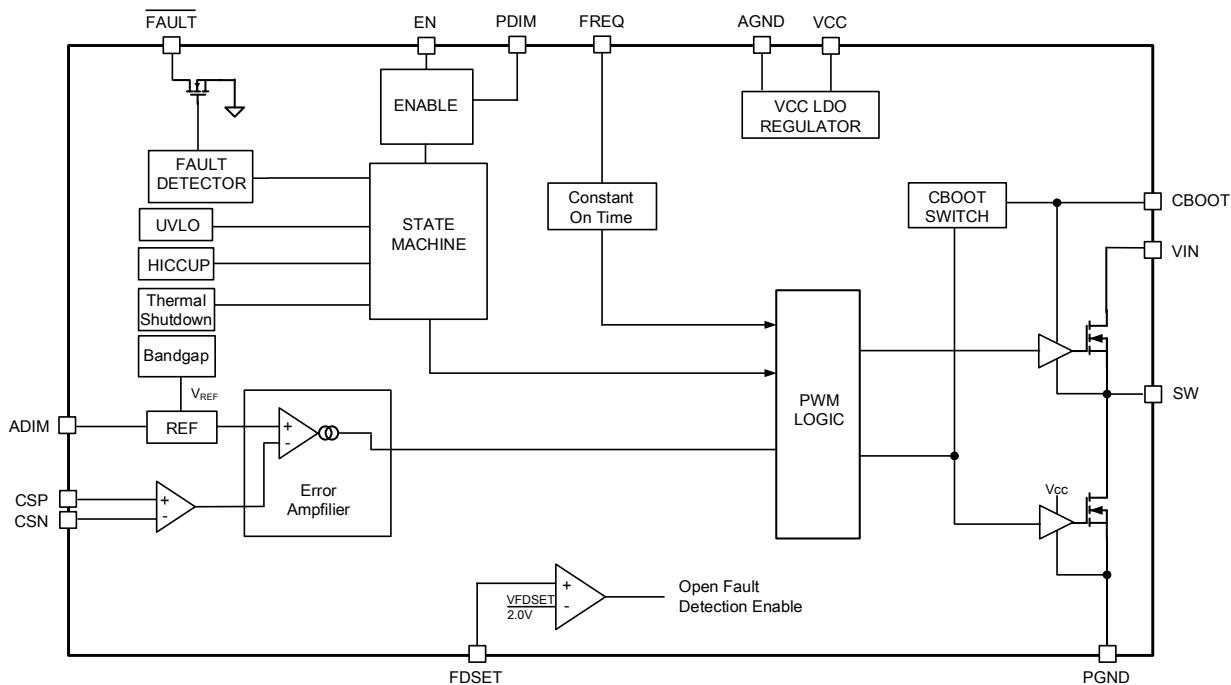

## Functional Block Diagram

Figure 2. Functional Block Diagram

## Pin Descriptions

| Pin Name            | Pin Number | Function                                                                                                                                                                                                                                |

|---------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGND                | 1, 2       | Power ground. Connect the pins to the ground plane.                                                                                                                                                                                     |

| VIN                 | 3          | Power supply input pin to high-side power MOSFET and VIN LDO regulator. Decouple this pin to GND with ceramic capacitors.                                                                                                               |

| EN                  | 4          | Enable pin for VCC LDO regulator and input voltage for VIN UVLO. Connect to VIN directly through a resistor divider, or to an external voltage source. This pin can also achieve PWM dimming by connecting to an external pulse signal. |

| PDIM                | 5          | PWM dimming input pin. Apply PWM signal for PWM dimming. Connect to high-level voltage when not in use. Do not leave it floating.                                                                                                       |

| FDSET               | 6          | Set VIN rising threshold to mask LED open fault. Connect to an external divider to detect VIN rising condition.                                                                                                                         |

| ADIM                | 7          | Apply an analog voltage for analog dimming. Do not leave it floating.                                                                                                                                                                   |

| FREQ                | 8          | Switching frequency control pin. Place a resistor between this pin and AGND to set the switching frequency between 200kHz and 2.5MHz.                                                                                                   |

| CSP                 | 9          | Current sense positive input across RCS                                                                                                                                                                                                 |

| CSN                 | 10         | Current sense negative input across RCS                                                                                                                                                                                                 |

| AGND                | 11         | Analog ground for regulator and system. All electrical parameters are measured with respect to this pin. Connect to EP and PGND on PCB.                                                                                                 |

| VCC                 | 12         | Internal VCC regulator that powers the control circuits. Must be decoupled to PGND with 1 $\mu$ F to 4.7 $\mu$ F ceramic capacitor.                                                                                                     |

| FAULT               | 13         | FAULT Indication. Asserted Low to report faulty conditions. Needs an external pullup resistor.                                                                                                                                          |

| NC                  | 14         | Not Connected, leave it floating.                                                                                                                                                                                                       |

| CBOOT               | 15         | Bootstrap supply input for high-side gate driver. Connect a 100nF ceramic capacitor from this pin to SW.                                                                                                                                |

| SW                  | 16         | Regulator switch node. Connect to power inductor.                                                                                                                                                                                       |

| Exposed Thermal Pad | —          | Connect to ground plane for adequate heat sinking and noise reduction.                                                                                                                                                                  |

## Absolute Maximum Ratings (Note 4)

| Symbol                                    | Parameter                                             | Rating               | Unit |

|-------------------------------------------|-------------------------------------------------------|----------------------|------|

| $V_{IN}$                                  | Input Voltages, $V_{IN}$ to PGND                      | -0.3 to +72          | V    |

| $V_{EN}, V_{FAULT}$                       | Input Voltages, EN, FAULT to AGND                     |                      | V    |

| $V_{AGND}$                                | Input Voltages, AGND to PGND                          | -0.3 to +0.3         | V    |

| $V_{PDIM}, V_{ADIM}, V_{FREQ}, V_{FDSET}$ | Input Voltages, PDIM, ADIM, FREQ, FDSET to AGND       | -0.3 to +5.5         | V    |

| $V_{SW}$                                  | Output Voltages, SW to PGND                           | -0.3 to $V_{IN}+0.3$ | V    |

| $V_{SW\_PK}$                              | Output Voltages, SW to PGND Less than 10ns Transients | -3.5 to +72          | V    |

| $V_{CSP}, V_{CSN}$                        | Input Voltages, CSP, CSN to AGND                      | -0.3 to +72          | V    |

| $V_{CBOOT\_SW}$                           | Output Voltages, CBOOT to SW                          | -0.3 to +5.5         | V    |

| $V_{CC}$                                  | Output Voltages, VCC to AGND                          | -0.3V to +5.5        | V    |

| $T_J$                                     | Operating Junction Temperature                        | -40 to +150          | °C   |

| $T_{ST}$                                  | Storage Temperature                                   | -55 to +150          | °C   |

| $V_{ESD}$                                 | Human Body Model (HBM)                                | ±2000                | V    |

|                                           | Charged Device Model (CDM)                            | ±1000                |      |

Note: 4. Stresses greater than those listed under *Absolute Maximum Ratings* can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to *Absolute Maximum Ratings* for extended periods can affect device reliability.

## Thermal Information (Note 5)

| Symbol               | Thermal Resistance                           | TSSOP-16EP | Unit |

|----------------------|----------------------------------------------|------------|------|

| $R_{JA}$             | Junction-to-Ambient Thermal Resistance       | 32.2       | °C/W |

| $R_{JC(\text{top})}$ | Junction-to-Case (Top) Thermal Resistance    | 40.7       | °C/W |

| $R_{JB}$             | Junction-to-Board Thermal Resistance         | 11.8       | °C/W |

| $\Psi_{JT}$          | Junction-to-Top Characterization Parameter   | 1.3        | °C/W |

| $\Psi_{JB}$          | Junction-to-Board Characterization Parameter | 11.9       | °C/W |

| $R_{JC(\text{bot})}$ | Junction-to-Case (Bottom) Thermal Resistance | 1.5        | °C/W |

Note: 5. The device is mounted on JEDEC standard 4 layers (2s2p) PCB test board.

## Recommended Operating Conditions (Over operating free-air temperature range, unless otherwise specified.) (Note 6)

| Parameter                                   |                   | Min  | Typ | Max      | Unit |

|---------------------------------------------|-------------------|------|-----|----------|------|

| Input voltages                              | $V_{IN}$ to PGND  | 4.5  | —   | 65       | V    |

|                                             | EN                | 0    | —   | $V_{IN}$ |      |

|                                             | PDIM, ADIM, FDSET | 0    | —   | 5.5      |      |

|                                             | AGND to PGND      | -0.1 | —   | 0.1      |      |

| Output Voltage, CBOOT                       |                   | 1    | —   | 65       | V    |

| Output Voltage, VOUT                        |                   | 1    | —   | 65       | V    |

| Output Current, IOUT                        |                   | 0    | —   | 2        | A    |

| Operating Junction Temperature Range, $T_J$ |                   | -40  | —   | +150     | °C   |

| Operating Ambient Temperature Range, $T_A$  |                   | -40  | —   | +125     | °C   |

Note: 6. Operating ratings indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For verified specifications, see *Electrical Characteristics*.

**Electrical Characteristics** ( $V_{IN} = 24V$ ,  $f_s = 400kHz$ ,  $T_A = -40^\circ C$  to  $+125^\circ C$ , unless otherwise specified.)

| Symbol                                       | Parameter                                              | Condition                                                  | Min | Typ  | Max  | Unit    |

|----------------------------------------------|--------------------------------------------------------|------------------------------------------------------------|-----|------|------|---------|

| <b>Supply Voltage (VIN Pin)</b>              |                                                        |                                                            |     |      |      |         |

| $V_{IN\_MIN}$                                | Minimum Input Voltage for Startup                      | —                                                          | —   | —    | 4.5  | V       |

| $I_{SHDN}$                                   | Shutdown Quiescent Current                             | $V_{IN} = 24V$ , $V_{EN} = 0V$                             | —   | 0.1  | 10   | $\mu A$ |

| $I_{Q\_SW}$                                  | Operating Quiescent Current (Switching)                | $V_{EN} = V_{IN} = 24V$ , $I_{OUT} = 0A$<br>$f_s = 400kHz$ | —   | 1.0  | —    | mA      |

| <b>Enable VIN UVLO (EN Pin)</b>              |                                                        |                                                            |     |      |      |         |

| $EN_{VCC-ON}$                                | $V_{EN}$ High-Level Threshold                          | $V_{EN}$ rising                                            | 2.2 | —    | —    | V       |

| $EN_{VCC-OFF}$                               | $V_{EN}$ Low-Level Threshold                           | $V_{EN}$ falling                                           | —   | —    | 0.7  | V       |

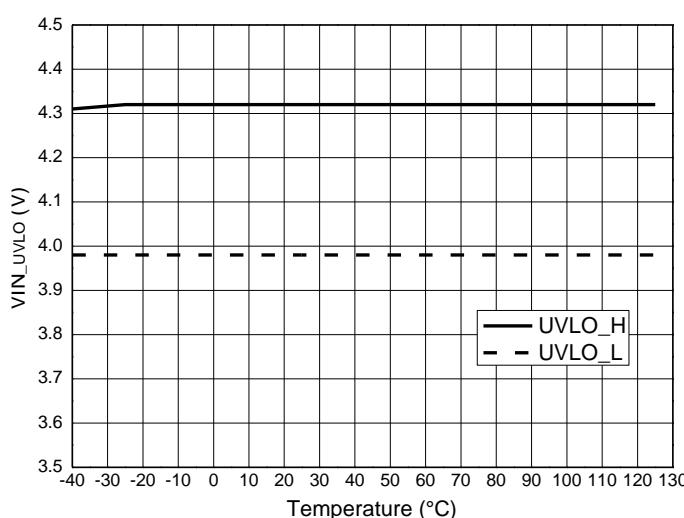

| $V_{IN\_UVLO\_R}$                            | $V_{IN}$ UVLO Rising Threshold                         | $V_{IN}$ rising                                            | 4.0 | 4.2  | 4.45 | V       |

| $V_{IN\_UVLO\_F}$                            | $V_{IN}$ UVLO Falling Threshold                        | $V_{IN}$ falling                                           | —   | 3.9  | —    | V       |

| $I_{Q-EN}$                                   | EN Pin Current                                         | $V_{EN} = 3.3V$                                            | —   | 1    | —    | $\mu A$ |

| $t_{EN\_OFF\_DELAY}$                         | EN Turned Off Delay                                    | —                                                          | 6   | 23   | 40   | ms      |

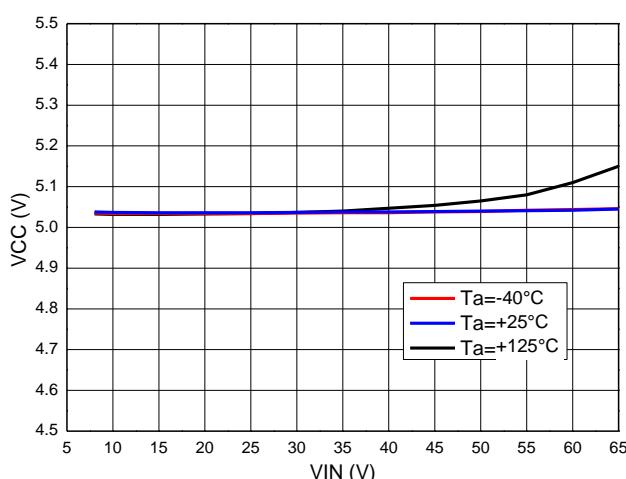

| <b>Internal LDO (VCC Pin)</b>                |                                                        |                                                            |     |      |      |         |

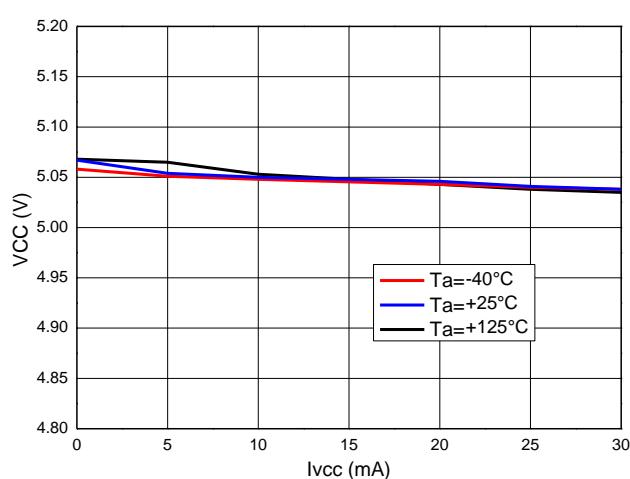

| $V_{CC}$                                     | Internal LDO Output Voltage $V_{CC}$                   | $V_{IN} \geq 6V$ , $I_{VCC} > 15mA$                        | 4.4 | 5.0  | 5.7  | V       |

| $I_{VCC\_LIMIT}$                             | $V_{CC}$ Current Limit                                 | $V_{IN} > 6V$ , $V_{CC} = 4.5V$                            | 30  | —    | —    | mA      |

| $V_{CC\_UVLO}$                               | Undervoltage Lockout (UVLO)<br>Thresholds for $V_{CC}$ | $V_{CC}$ rising threshold                                  | 3.4 | 3.6  | 3.8  | V       |

|                                              |                                                        | $V_{CC}$ thresholds hysteresis                             | —   | 0.15 | —    | mV      |

| <b>Current Control (CSP, CSN, ADIM Pins)</b> |                                                        |                                                            |     |      |      |         |

| $V_{CSP-CSN}$                                | CSP-CSN Voltage                                        | $V_{ADIM} = 2V$                                            | 192 | 200  | 208  | mV      |

|                                              |                                                        | $V_{ADIM} = 1V$                                            | —   | 100  | —    |         |

|                                              |                                                        | $V_{ADIM} = 0.4V$                                          | —   | 40   | —    |         |

| $V_{CSP}-V_{CSN\ LOW\ CLAMP}$                | Analog Dimming Low Clamp                               | $V_{ADIM} \leq 0.15V$                                      | —   | 15   | —    | mV      |

| $I_{CSN}$                                    | CSN Sink Current                                       | $V_{CSP} - V_{CSN} = 200mV$ , $V_{CSN} > 5V$               | 30  | 60   | 90   | $\mu A$ |

| <b>Overcurrent Limit</b>                     |                                                        |                                                            |     |      |      |         |

| $I_{HS-LIMIT}$                               | Peak Inductor Current Positive Limit                   | $V_{IN} = 24V$                                             | —   | 3.6  | —    | A       |

| $I_{LS-LIMIT}$                               | Valley Inductor Current Negative Limit                 | $V_{IN} = 24V$                                             | —   | -1.6 | —    | A       |

**Electrical Characteristics** (continued) ( $V_{IN} = 24V$ ,  $f_s = 400kHz$ ,  $T_A = -40^\circ C$  to  $+125^\circ C$ , unless otherwise specified.)

| Symbol                                      | Parameter                                  | Condition                                                                                                                               | Min | Typ      | Max | Unit      |

|---------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----|-----------|

| <b>Power MOSFETs (Note 7)</b>               |                                            |                                                                                                                                         |     |          |     |           |

| $R_{DS(ON\_HS)}$                            | High-Side MOSFET ON-Resistance (Note 8)    | $I_{OUT} = 0.5A$ , $V_{CBOOT} - V_{SW} = 5V$                                                                                            | —   | 200      | 360 | $m\Omega$ |

| $R_{DS(ON\_LS)}$                            | Low-Side MOSFET ON-Resistance (Note 8)     | $I_{OUT} = 0.5A$ , $V_{CC} = 5V$                                                                                                        | —   | 130      | 240 | $m\Omega$ |

| <b><math>t_{ON}</math> (SW, FREQ Pins)</b>  |                                            |                                                                                                                                         |     |          |     |           |

| $t_{ON\_MIN\_HS}$                           | Minimum High-Side MOSFET ON-Time           | $T_A = +25^\circ C$ , $V_{IN} = 24V$ , $V_{OUT} = 12V$<br>$R_{ON} = 237k\Omega$ , $I_{LOAD} = 0A$                                       | —   | 65       | 90  | ns        |

| $t_{ON}$                                    | Typical $t_{ON}$ @ 400kHz                  | $T_A = +25^\circ C$ , $V_{IN} = 24V$ , $V_{OUT} = 12V$<br>$R_{ON} = 237k\Omega$ , $I_{LOAD} = 0A$                                       | —   | 1250     | —   | ns        |

| $f$                                         | Typical 400kHz Frequency                   | $T_A = +25^\circ C$ , $V_{IN} = 24V$ , $V_{OUT} = 12V$<br>$R_{ON} = 237k\Omega$ , $I_{LOAD} = 0A$                                       | —   | 400k     | —   | Hz        |

| $\%F$                                       | Frequency over 400kHz Target               | $V_{IN} = 4.5V$ to $65V$<br>$V_{OUT} = 3V$ to $V_{IN} \times 95\%$ , $R_{ON} = 237k\Omega$<br>$I_{LOAD} = 0A$ , full temperature range  | 80  | —        | 120 | %         |

| $t_{ON\_2.1M}$                              | Typical $t_{ON}$ @ 2.1MHz                  | $T_A = +25^\circ C$ , $V_{IN} = 24V$ , $V_{OUT} = 12V$<br>$R_{ON} = 43k\Omega$ , $I_{LOAD} = 0A$                                        | —   | 238      | —   | ns        |

| $f_{2.1M}$                                  | Typical 2.1MHz Frequency                   | $T_A = +25^\circ C$ , $V_{IN} = 24V$ , $V_{OUT} = 12V$<br>$R_{ON} = 43k\Omega$ , $I_{LOAD} = 0A$                                        | —   | 2.1M     | —   | Hz        |

| $\%F_{2.1M}$                                | Frequency over 2.1MHz Target               | $V_{IN} = 4.5V$ to $65V$<br>$V_{OUT} = 3.5V$ to $V_{IN} \times 85\%$ , $R_{ON} = 43k\Omega$<br>$I_{LOAD} = 0A$ , full temperature range | 80  | —        | 120 | %         |

| $t_{OFF\_MIN\_HS}$                          | Minimum High-Side MOSFET OFF-Time (Note 7) | —                                                                                                                                       | —   | 100      | —   | ns        |

| <b>Dimming (PDIM Pin)</b>                   |                                            |                                                                                                                                         |     |          |     |           |

| $V_{PDIM}$                                  | PDIM Input Threshold                       | Rising                                                                                                                                  | 1.5 | —        | —   | V         |

|                                             |                                            | Falling                                                                                                                                 | —   | —        | 0.7 | V         |

| $t_{ON\_PDIM\_MIN}$                         | Minimum PWM On Time for FAULT Recovery     | —                                                                                                                                       | —   | 360      | —   | $\mu s$   |

| <b>Spread Spectrum (Measured at SW Pin)</b> |                                            |                                                                                                                                         |     |          |     |           |

| $t_{ON\_SS}$                                | $t_{ON}$ Spread Spectrum Amplitude         | $T_A = +25^\circ C$ , $V_{IN} = 24V$ , $V_{OUT} = 12V$<br>$R_{ON} = 238.5k\Omega$ , $I_{LOAD} = 0A$                                     | —   | $\pm 10$ | —   | %         |

| $f_{SS}$                                    | $t_{ON}$ Spread Spectrum Frequency         | $T_A = +25^\circ C$ , $V_{IN} = 24V$ , $V_{OUT} = 12V$<br>$R_{ON} = 238.5k\Omega$ , $I_{LOAD} = 0A$                                     | —   | 20       | —   | kHz       |

Notes: 7. Guaranteed by design.

8. Measured at package pins.

**Electrical Characteristics** (continued) ( $V_{IN} = 24V$ ,  $f_s = 400kHz$ ,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise specified.)

| Symbol                  | Parameter                                   | Condition         | Min | Typ  | Max | Unit        |

|-------------------------|---------------------------------------------|-------------------|-----|------|-----|-------------|

| <b>Fault Detection</b>  |                                             |                   |     |      |     |             |

| $V_{FT\_SHORT\_FALL}$   | LED Short Threshold Detected on CSN Falling | $V_{IN} = 24V$    | 1.0 | 1.6  | —   | V           |

| $V_{FT\_SHORT\_RISE}$   | LED Short Threshold Detected on CSN Rising  | $V_{IN} = 24V$    | —   | 1.8  | 2.5 | V           |

| $V_{PD\_FAULT}$         | $\overline{FAULT}$ Pin Pulldown Strength    | $I_{FT} = 1mA$    | —   | 40   | 100 | mV          |

| $t_{FDFT}$              | $\overline{FAULT}$ Deglitch Timer           | —                 | —   | 80   | —   | $\mu s$     |

| $t_{MASK-DET}$          | $\overline{FAULT}$ Detect Mask Timer        | —                 | —   | 160  | —   | $\mu s$     |

| $t_{MASK-REL}$          | $\overline{FAULT}$ Mask Release Timer       | —                 | —   | 320  | —   | $\mu s$     |

| $I_{LEAK\_FT}$          | $\overline{FAULT}$ Leakage Current          | $V_{FT} = 5V$     | —   | 10   | 100 | nA          |

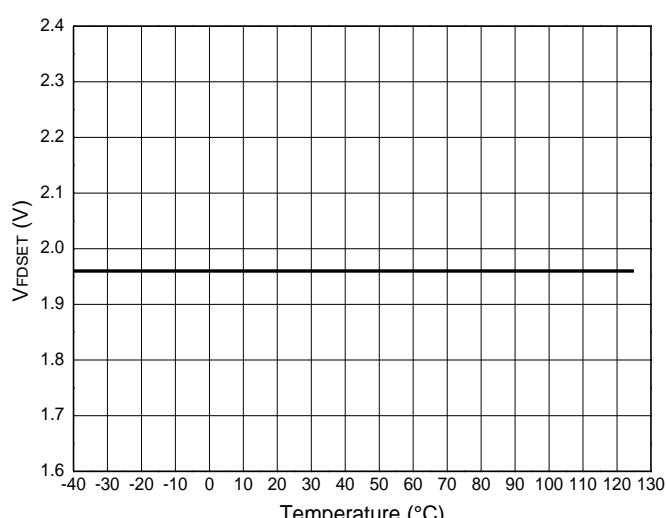

| $V_{FDSET}$             | LED Open-Fault Enable Reference             | Reference to AGND | 1.8 | 2.0  | 2.2 | V           |

| $R_{OPEN}$              | FREQ Pin to GND Open Detect Threshold       | $V_{CC} = 5V$     | 2   | —    | —   | $M\Omega$   |

| $R_{SHORT}$             | FREQ Pin to GND Short Detect Threshold      | $V_{CC} = 5V$     | —   | —    | 150 | $\Omega$    |

| $t_{RETRY}$             | Time for Fault Retry                        | —                 | —   | 1    | —   | ms          |

| <b>Thermal Shutdown</b> |                                             |                   |     |      |     |             |

| $T_{SD}$                | Thermal Shutdown Threshold                  | —                 | —   | +170 | —   | $^{\circ}C$ |

| $T_{SD(HYS)}$           | Thermal Shutdown Hysteresis                 | —                 | —   | +20  | —   | $^{\circ}C$ |

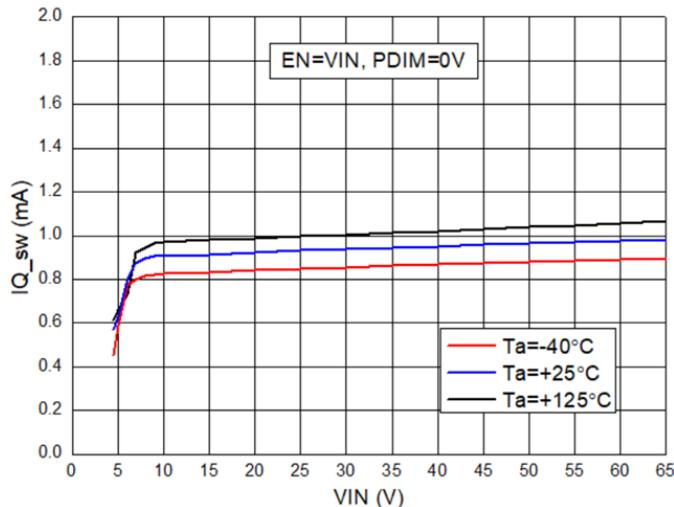

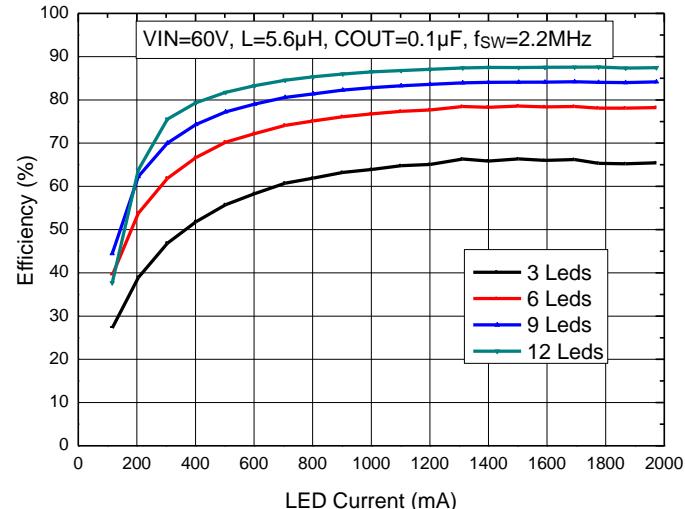

**Typical Performance Characteristics** (VIN = 24V, I<sub>OUT</sub> = 2A, C<sub>OUT</sub> = 0.47μF, f<sub>sw</sub> = 400kHz, unless otherwise specified.)

Figure 3. IQ<sub>SW</sub> vs. VIN

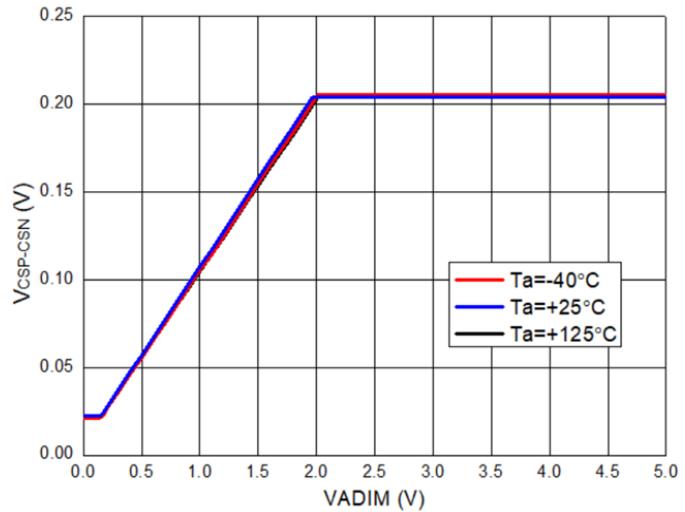

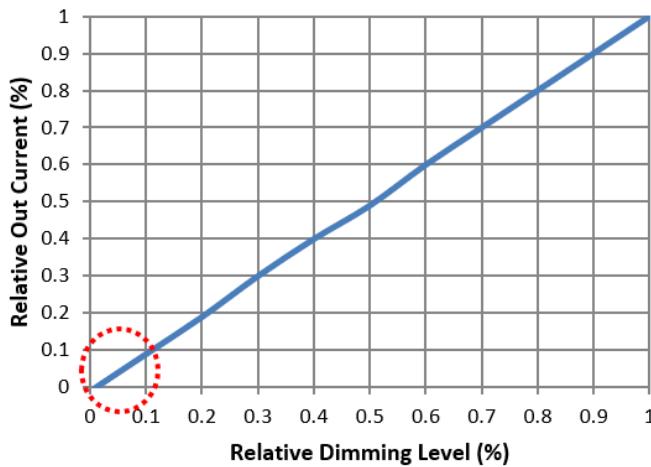

Figure 4. Analog Dimming Curve

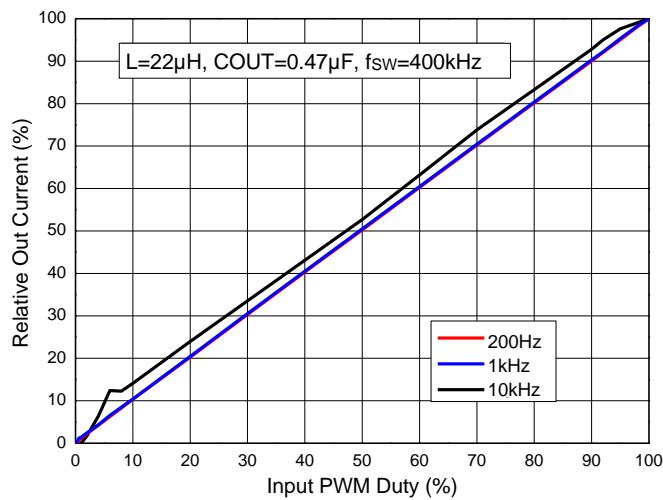

Figure 5. PWM Dimming Curve

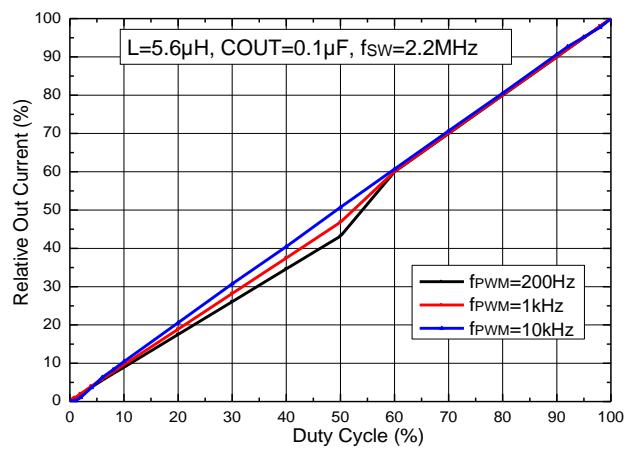

Figure 6. PWM Dimming Curve

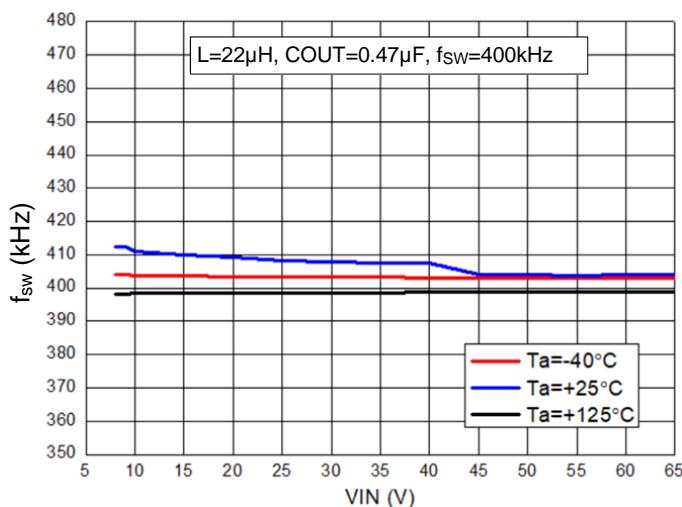

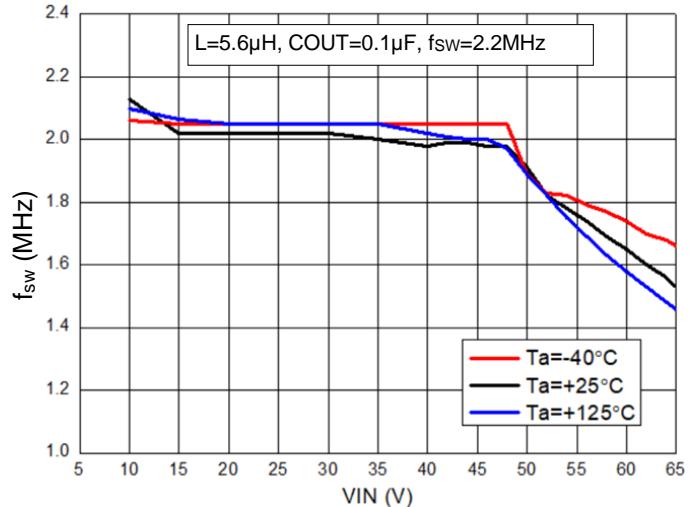

Figure 7. f<sub>sw</sub> vs. VIN

Figure 8. f<sub>sw</sub> vs. VIN

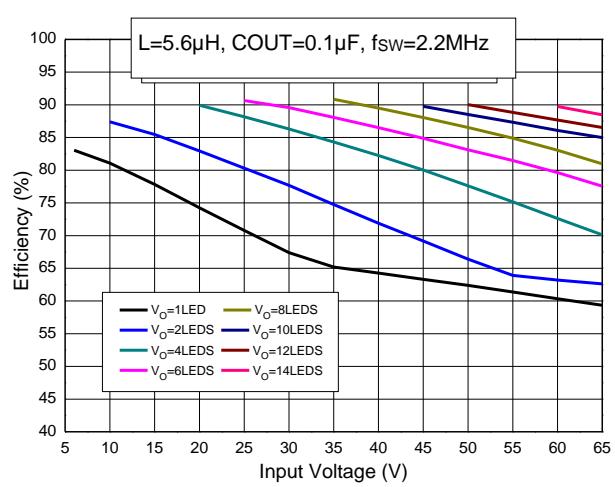

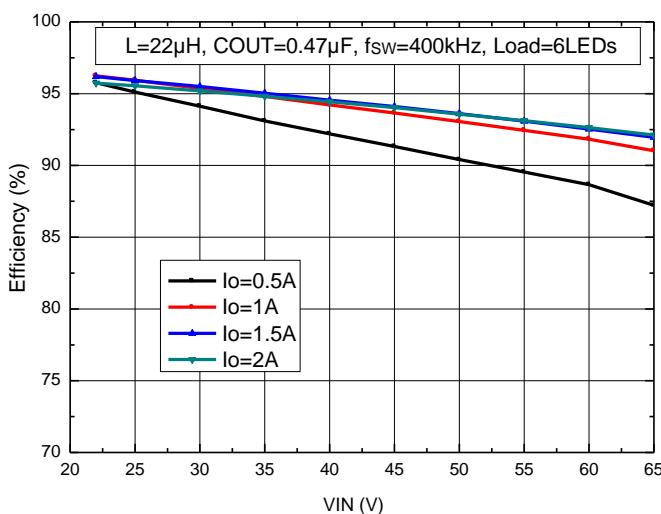

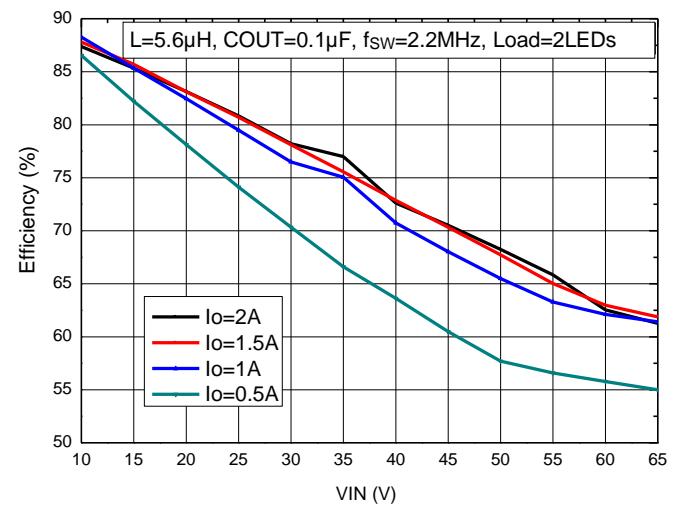

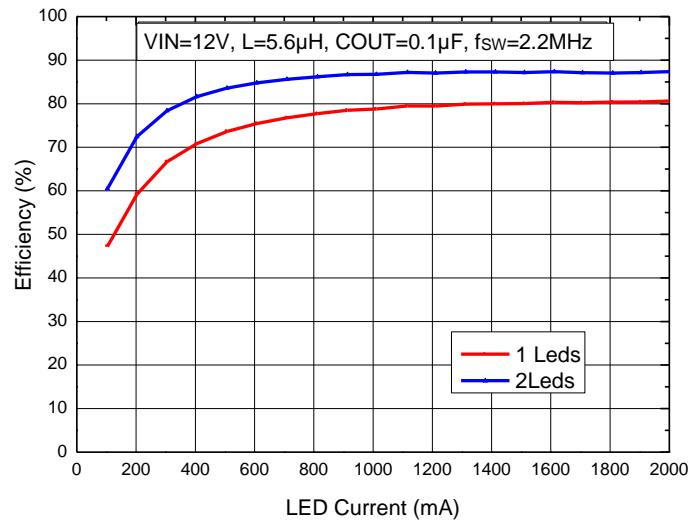

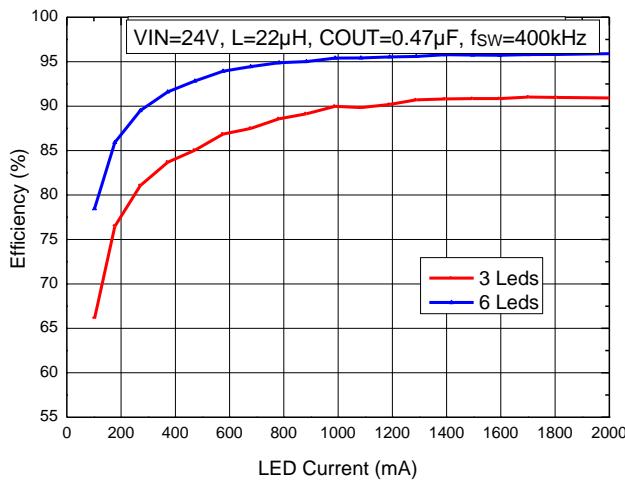

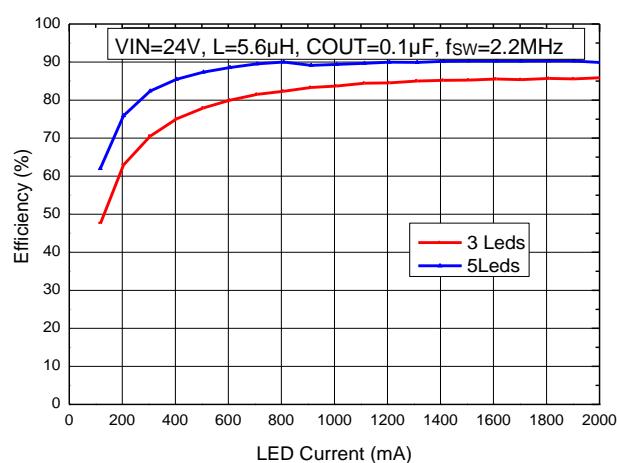

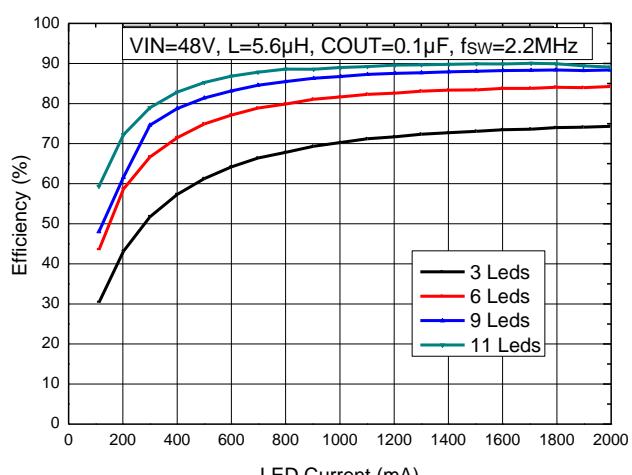

**Typical Performance Characteristics** (continued)

(VIN = 24V, I<sub>OUT</sub> = 2A, C<sub>OUT</sub> = 0.47μF, f<sub>SW</sub> = 400kHz, unless otherwise specified.)

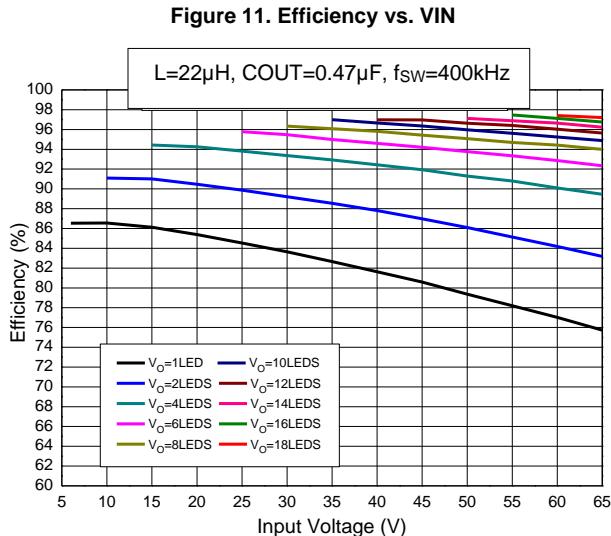

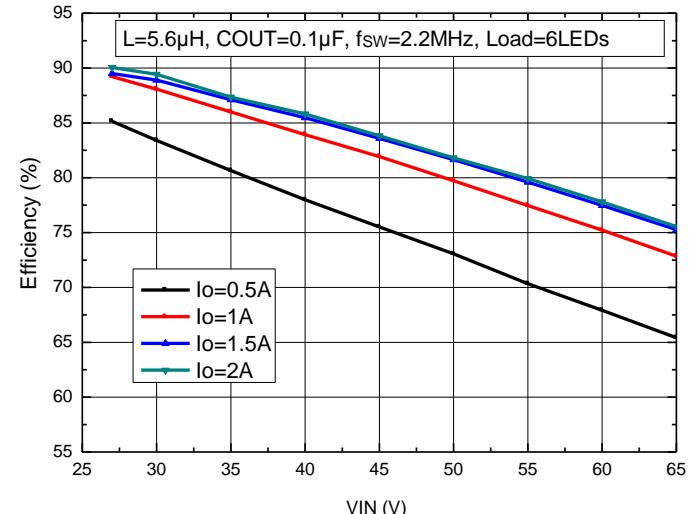

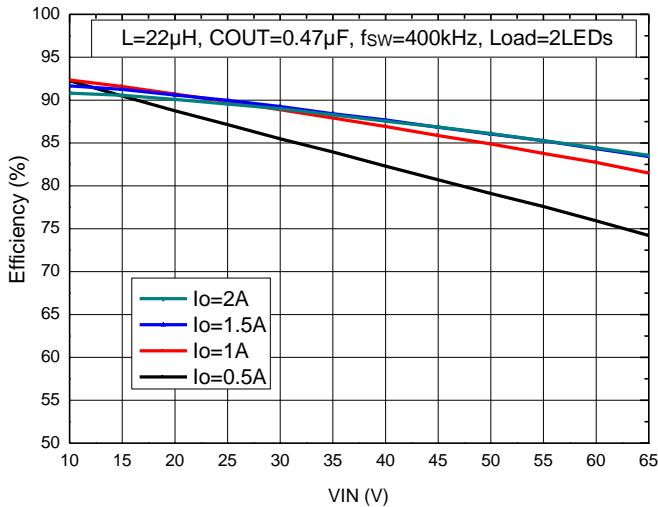

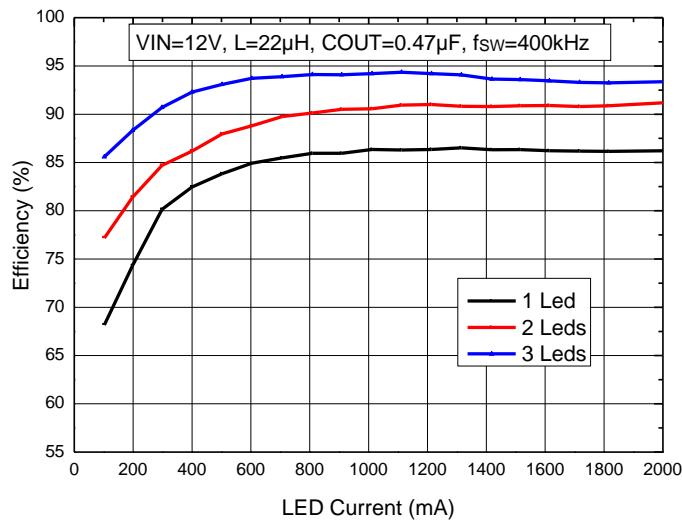

**Typical Performance Characteristics** (continued)

( $V_{IN} = 24V$ ,  $I_{OUT} = 2A$ ,  $C_{OUT} = 0.47\mu F$ ,  $f_{SW} = 400kHz$ , unless otherwise specified.)

Figure 15. Efficiency vs. LED Current

Figure 16. Efficiency vs. LED Current

Figure 17. Efficiency vs. LED Current

Figure 18. Efficiency vs. LED Current

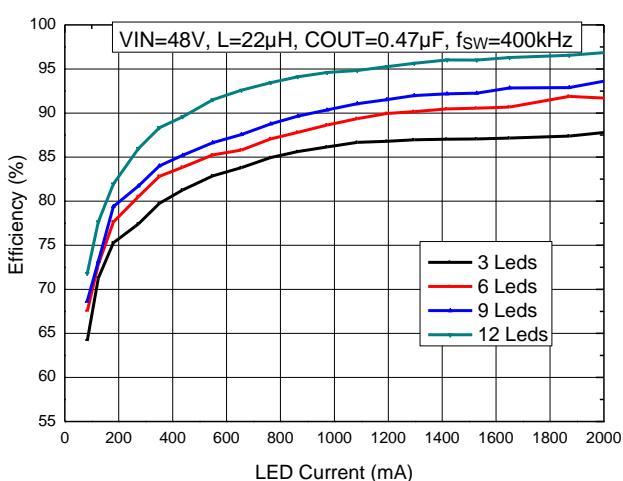

Figure 19. Efficiency vs. LED Current

Figure 20. Efficiency vs. LED Current

**Typical Performance Characteristics** (continued)

(VIN = 24V, I<sub>OUT</sub> = 2A, C<sub>OUT</sub> = 0.47μF, f<sub>sw</sub> = 400kHz, unless otherwise specified.)

**Typical Performance Characteristics** (continued)

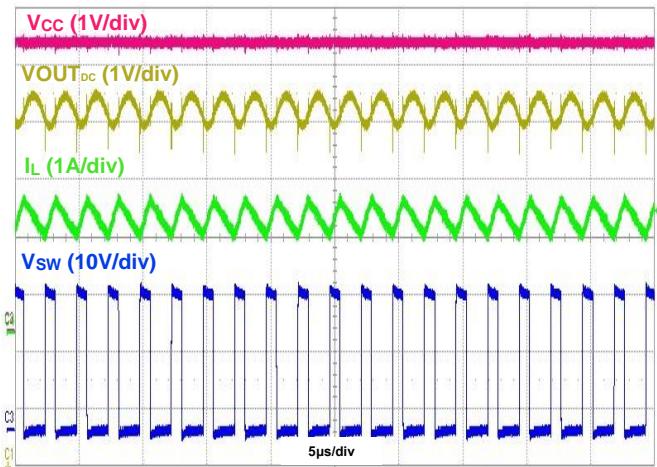

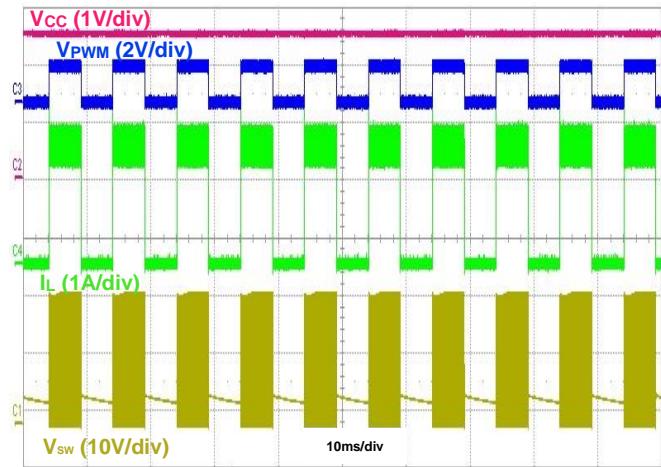

( $V_{IN} = 24V$ ,  $I_{OUT} = 2A$ ,  $C_{OUT} = 0.47\mu F$ ,  $f_{sw} = 400kHz$ , unless otherwise specified.)

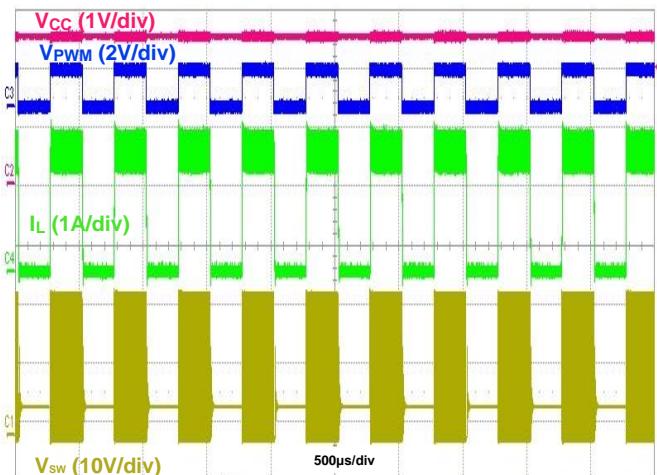

Figure 27. Steady State,  $I_{OUT} = 2A$

Figure 28. PWM Dimming, 100Hz, 50% Duty Cycle

Figure 29. PWM Dimming, 2kHz, 50% Duty Cycle

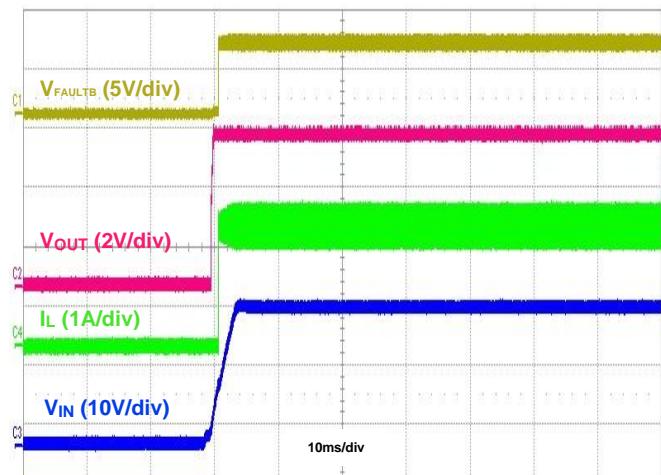

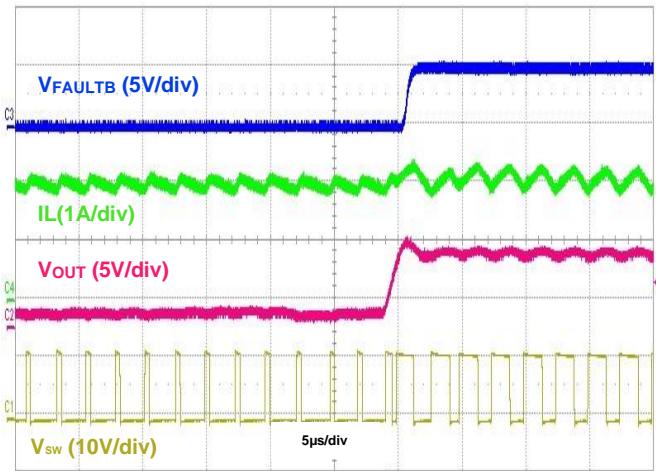

Figure 30. Startup through  $V_{IN}$

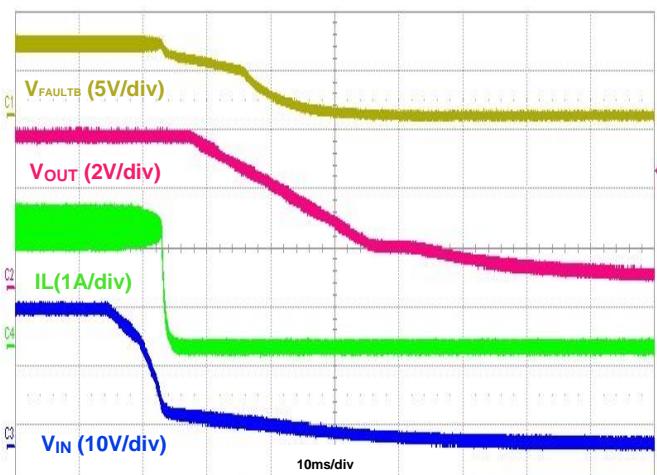

Figure 31. Shutdown through  $V_{IN}$ ,  $V_{FDSET} = 0V$

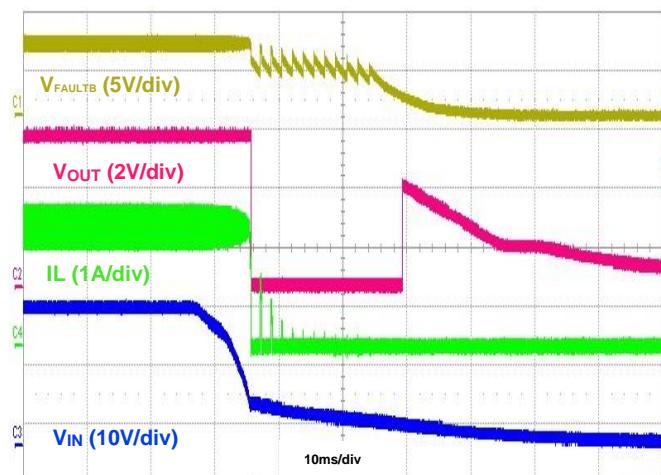

Figure 32. Shutdown through  $V_{IN}$ ,  $V_{FDSET} = 5V$

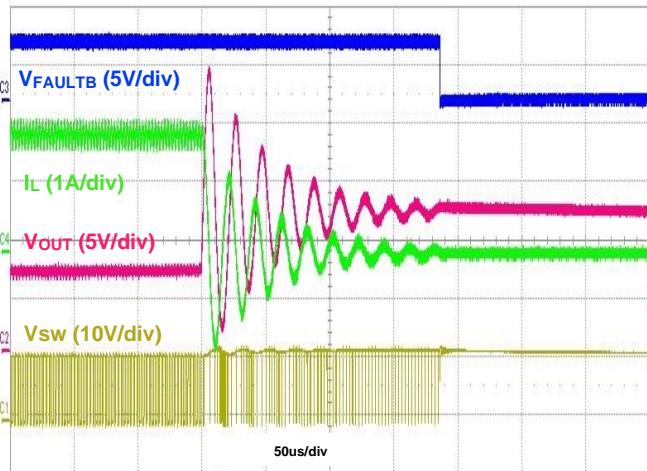

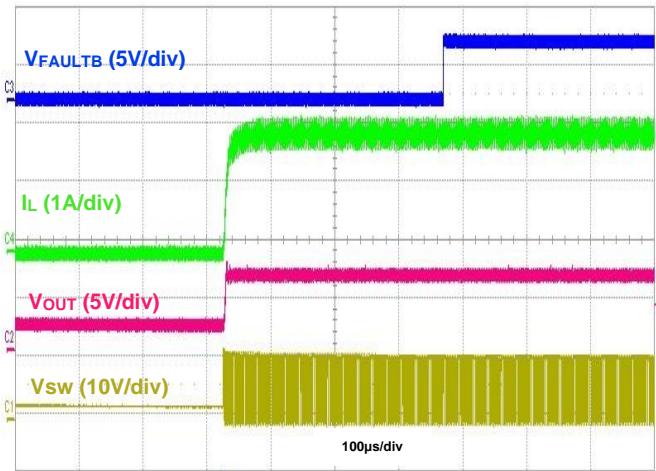

**Typical Performance Characteristics** (Test at  $T_A = +25^\circ\text{C}$ ,  $V_{IN} = 24\text{V}$ , LOAD = 2LEDs in series,  $I_{OUT} = 2\text{A}$ ,  $C_{OUT} = 0.47\mu\text{F}$ ,  $f_{SW} = 400\text{kHz}$ , unless otherwise specified.)

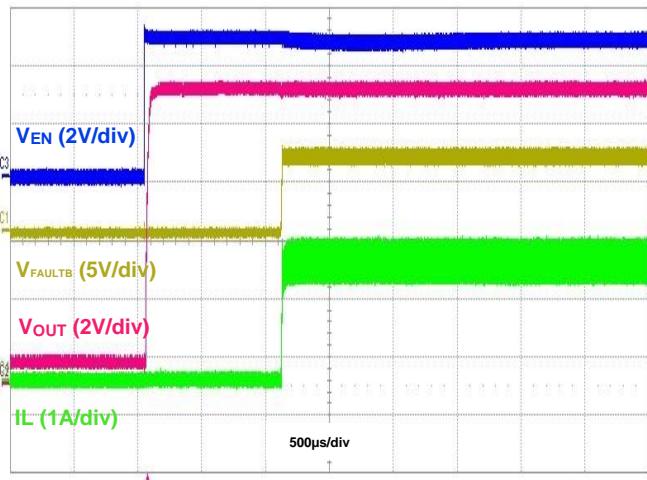

Figure 33. Start through EN

Figure 34. Shutdown through EN

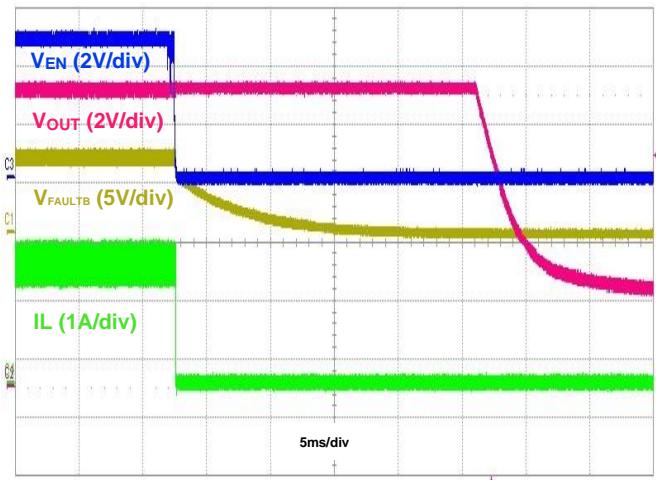

Figure 35. LED+ Short to LED- Entry,  $V_{IN} = 12\text{V}$

Figure 36. LED+ Short to LED- Recovery,  $V_{IN} = 12\text{V}$

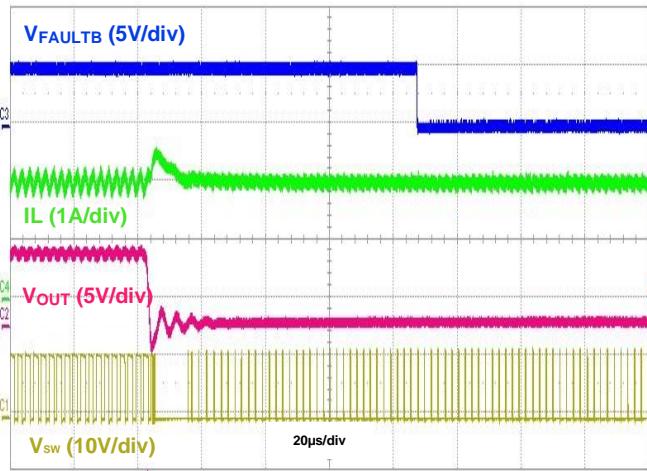

Figure 37. LED Open Entry,  $V_{IN} = 12\text{V}$

Figure 38. LED Open Recovery,  $V_{IN} = 12\text{V}$

## Functional Description

### Overview

The AL8891Q regulator is an easy-to-use, high-efficiency, compact, synchronous step-down LED driver capable of driving up to 2A of load current from an input voltage ranging from 4.5V to 65V. The switching frequency is adjustable from 200kHz to 2.5MHz by an external resistor.

Constant on time control is employed to achieve simple control-loop compensation and cycle-by-cycle current limiting. Internal compensation makes the AL8891Q require few external components.

Optional features such as programmable switching frequency, Power Good flag, internal soft-start, and multiple dimming methods provide a flexible and easy-to-use platform for a wide range of applications. Protection features include thermal shutdown, VIN and VCC undervoltage lockout, cycle-by-cycle current limit, output short-circuit protection, LED open and short detection, and external components open and short protection.

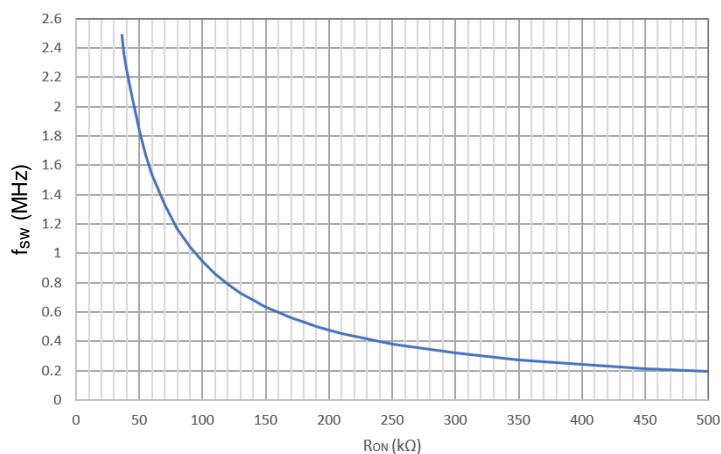

### Switching Frequency

An adaptive on-time average current mode control is implemented to provide near constant switching frequency which can be set between 200kHz and 2.5MHz. The frequency is programmed using an external resistor  $R_{ON}$  connected between the FREQ pin and ground, thus the switching frequency is adjusted.  $t_{ON}$  is given by the following equation:

$$t_{ON} = k \times (R_{ON} + R_{INT}) \times (V_{OUT}/V_{IN}) \quad \text{Equation 1}$$

$$f_{SW} = 1 / [k \times (R_{ON} + R_{INT})] \quad \text{Equation 2}$$

Where  $k = 0.0103$ , with  $f_{SW}$  in MHz,  $t_{ON}$  in  $\mu s$ ,  $R_{ON}$  and  $R_{INT}$  in  $k\Omega$ .  $R_{INT}$  is an internal resistor  $3k\Omega$ .

Figure 39.  $f_{SW}$  vs.  $R_{ON}$

### Enable (EN)

Enable (EN) is a digital control pin that turns the converter on and off. The AL8891Q is activated when a logic high signal is applied to the EN pin and VIN is above UVLO threshold. The device delivers desired LED current set by RCS when PDIM is high. EN pin should not be open circuit or floating.

### PWM Dimming (PDIM)

PWM dimming can be achieved by PDIM pin or EN pin. By sending a PWM signal to PDIM pin or EN pin, the average LED current is proportional to the duty cycle of the applied PWM signal. The dimming frequency between 100Hz and 2kHz is recommended. By selecting a PWM frequency 100Hz, a dimming ratio of 0.1% can be achieved. The average LED current during dimming can be calculated as the following equation:

$$I_{LED\_AVG} = \text{PWM duty cycle} \times I_{LED\_setting} \quad \text{Equation 3}$$

Note that when EN dimming is applied, a pulse width greater than 200 $\mu s$  is necessary to activate the device during startup.

When the EN pin is toggled from high to low, the output is turned off immediately, but VCC will keep on for time  $t_{EN\_OFF\_DELAY}$  and the device will stay in standby mode during this period. After that VCC will turn off, and the device will shut down completely.

## Functional Description (continued)

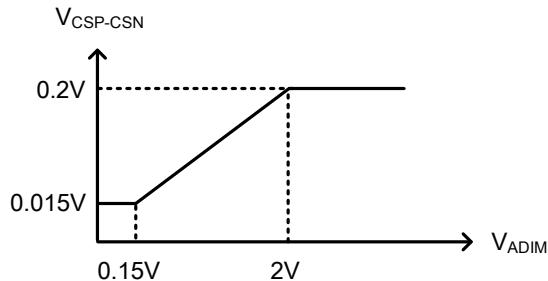

### Analog Dimming (ADIM)

The AL8891Q can also achieve analog dimming by applying an analog voltage on ADIM pin. When  $V_{ADIM}$  is higher than 2.0V, the LED current is at 100% level which is defined by sense resistor  $R_{CS}$ . When  $V_{ADIM}$  is between 2V and 0.15V, the LED current decreases linearly down from 100% to 7.5% level. The LED current is internally clamped to 7.5% level when  $V_{ADIM}$  is lower than 0.15V. The analog dimming feature is shown as below.

Figure 40. V<sub>CSP-CSN</sub> vs. V<sub>ADIM</sub>

Then the LED current can be calculated as the following equation, the LED current can be programmed by sense resistor  $R_{CS}$ .

$$I_{LED\_AVG} = V_{CSP-CSN}/R_{CS} \quad \text{Equation 4}$$

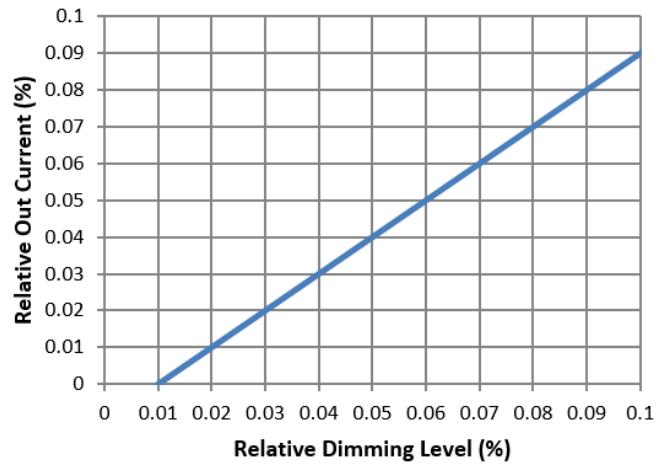

### Hybrid Dimming

AL8891Q has independent PWM dimming and analog dimming input pins, hybrid dimming mode by controlling PDIM and ADIM pins to achieve better dimming resolution. AL8891Q supports 0.1% depth with 100Hz PWM dimming in directive PWM dimming mode. If analog dimming level is set to 20%, the dimming depth would be low to 0.01% at 100Hz 0.25% PWM input.

VIN=12V, Vout =6.6V, Iout =2A, Fpwm=100Hz

(ADIM=20% + PDIM=0.05-5%)

Figure 41. Hybrid Dimming – ADIM + PDIM 0.01% Resolution

VIN=12V, Vout =6.6V, Iout =2A, Fpwm=100Hz

(ADIM=20% + PDIM=0.05-5%)

Figure 42. Hybrid Dimming Zoom in 0.01% Resolution

---

**Functional Description** (continued)**VCC, and UVLO**

The AL8891Q integrates an internal LDO to generate Vcc for control circuitry and MOSFET drivers. The nominal voltage for Vcc is 5V (typical). The VCC pin is the output of the LDO. A high-quality ceramic capacitor is recommended to be placed as close as possible to VCC pin. The VCC output pin must not be loaded during operation.

Undervoltage lockout (UVLO) protects the chip from operating at an insufficient supply voltage. It monitors the VCC voltage. When the voltage is lower than UVLO threshold voltage, the device is shut down. The UVLO rising threshold is about 3.6V (typical), while its falling threshold is 3.45V (typical).

**Bootstrap Voltage (CBOOT)**

A voltage higher than VIN is required to drive the HS power MOSFET. The capacitor connected between CBOOT and SW pins works as a charge pump to boost voltage on the CBOOT pin to (Vsw + Vcc) through internally integrated diode. A ceramic capacitor of 0.47 $\mu$ F/6.3V or higher value for CBOOT is recommended.

## Functional Information – Fault and Protections

The AL8891Q provides full protection functions, including cycle-by-cycle peak and valley current clamp, LED short and open protection, inductor short and open protection, RCS short protection (overcurrent), LED+ short to battery protection, FREQ pin short and open protection, and thermal shutdown. The following table summarizes all fault functions.

| Fault                 | Detection                                                                                           | Fault Flag | Fault Delay           | Fault Mode                 | Output  |

|-----------------------|-----------------------------------------------------------------------------------------------------|------------|-----------------------|----------------------------|---------|

| LED+ short to LED-    | CSN-PGND < 1.6V                                                                                     | Yes        | t <sub>FDT</sub>      | No action to driver        | Running |

| LED open              | FDSET > threshold & low LED current, inactive if ADIM < 0.4V.                                       | Yes        | t <sub>MASK_DET</sub> | Hiccup mode                | Stop    |

| LED+ short to battery | Same as LED open                                                                                    | Yes        | t <sub>MASK_DET</sub> | Hiccup mode                | Stop    |

| Inductor open         | Same as LED open                                                                                    | Yes        | t <sub>MASK_DET</sub> | Hiccup mode                | Stop    |

| Inductor short        | Trigger peak current limit for 9 cycles then latch. Toggling EN can exit latch after fault removal. | Yes        | 0μs                   | Latchoff                   | Stop    |

| Rcs short             | FDSET > threshold & overcurrent, inactive if ADIM < 0.4V.                                           | Yes        | t <sub>MASK_DET</sub> | Hiccup mode                | Stop    |

| Overcurrent           | Trigger peak current limit for 9 cycles then latch.                                                 | Yes        | 0μs                   | Latchoff                   | Stop    |

| FREQ pin open         | External resistor open circuit detected for FREQ pin after VCC power-up                             | Yes        | 0μs                   | Latchoff                   | Stop    |

| FREQ pin short        | External resistor short circuit detected for FREQ pin after VCC power-up.                           | Yes        | 0μs                   | Latchoff                   | Stop    |

| Overtemperature       | T <sub>J</sub> > Thermal shutdown threshold                                                         | Yes        | 0μs                   | Shutdown and auto recovery | Stop    |

### LED+ Short to LED-

When output short fault occurs and CSN-PGND < 1.6V, including LED+ short to LED- or output capacitor short or any other event resulting in output short, the fault is detected, and FAULT pin is set to low level after deglitch time t<sub>FDT</sub>. But the converter will work continuously and output nominal current. When the output short fault is removed and CSN-PGND > 1.8V, FAULT is set to high level immediately and the converter returns to normal work.

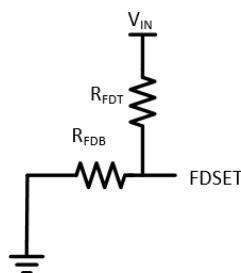

### LED Open

The LED open fault is masked when FDSET pin voltage is lower than V<sub>FDSET</sub> to avoid misreporting LED open faults during VIN startup. To achieve the mask function, connect a voltage divider between VIN and GND, and connect the center of the divider to FDSET pin.

Figure 43. Set VIN Threshold to Mask LED Open Fault

---

## Functional Information – Fault and Protections (continued)

---

The VIN rising threshold that enables LED open fault detection can be determined by:

$$V_{IN-RISING} = (1 + R_{FDT} / R_{FDB}) \times V_{FDSET} \quad \text{Equation 5}$$

In addition, no LED open fault reporting if  $ADIM < 0.4V$ . So, only  $FDSET >$  threshold and  $ADIM > 0.4V$  are met, the LED open fault is reported, and the converter enter hiccup mode after mask time  $t_{MASK-DET}$ . When LED open is removed, the converter returns to normal operation when a hiccup period ended.  $\overline{FAULT}$  pin is set to high level after mask time  $t_{MASK-REL}$ . The cool down time of hiccup mode is  $t_{TRY}$ .

Note that FDSET is a high-impedance input pin and should not be left floating. If LED open detection is not required, tie the FDSET pin to GND. Or tie the FDSET pin to VCC then LED Open fault is never masked.

For inductor open and LED+ short to Battery fault, the detection and recovery is same as LED open fault.

### RCS Short

When RCS short occurs and the peak current does not reach peak current limit  $I_{PEAK-LIMIT}$ , the converter will enter hiccup mode after mask time  $t_{MASK-DET}$  and  $\overline{FAULT}$  is set to low level. When RCS short is removed, the converter returns to normal operation: 1) when a hiccup period ended, and  $\overline{FAULT}$  pin is set to high level after mask time  $t_{MASK-REL}$ ; 2)  $FDSET >$  threshold and  $ADIM > 0.4V$ .

### Inductor Short and Overcurrent Protection

When inductor short occurs, the current of internal power MOSFET will ramp up until it hits peak current limit  $I_{PEAK-LIMIT}$ . After triggering peak current limit for 9 cycles the converter latches off immediately and  $\overline{FAULT}$  is set to low level. Toggling EN can exit latch after inductor short fault is removed.

Besides inductor short, if there is any other reason that results in the current of internal power MOSFET triggering peak current limit for 9 cycles, the converter will latch off.

### FREQ Pin Fault

There is FREQ pin short and open detection after each VCC power-up. Make sure the FREQ pin is properly connected to a resistor to avoid triggering pin short or open fault. After fault is detected, the converter latches off immediately and  $\overline{FAULT}$  pin is set to low level. The fault is latched until next VCC power-up.

### Overtemperature Protection

When the junction temperature exceeds  $T_{SD}$ , the AL8891Q shuts down the switching regulator to reduce thermal dissipation. It automatically restarts the switching regulator after junction temperature drops back below  $T_{SD}-T_{SD(HYS)}$ . The VCC LDO regulators remain operational during overtemperature event.

## Application Information

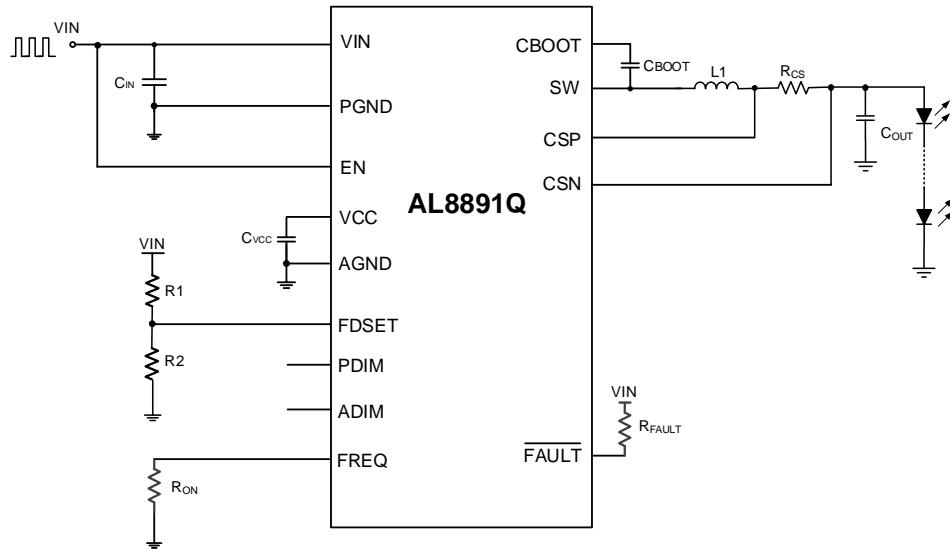

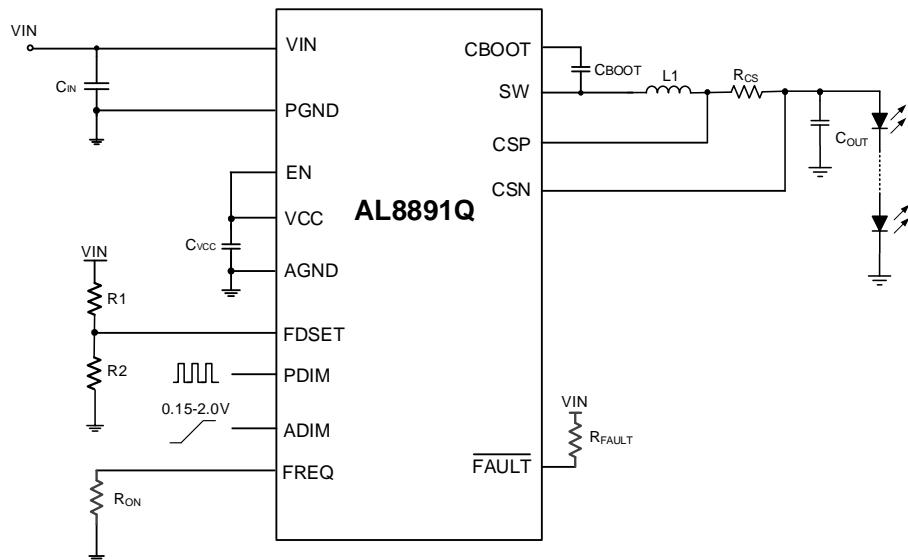

### 1) PWM Dimming Application Diagram

Figure 44. PWM Dimming Application Diagram

### 2) Analog Dimming Application Diagram

Figure 45. Analog Dimming Application Diagram

## Application Information (continued)

### 3) EN Pin to VIN Dimming Application Diagram

Figure 46. EN Pin to VIN Dimming Application Diagram

### 4) PDIM and ADIM Both Pins Dimming Application Diagram

Figure 47. PDIM and ADIM Both Pins Dimming Application Diagram

---

## Application Information (continued)

---

### 5) Output Capacitor Calculation

The output capacitor value depends on the total series resistance of the LED string,  $r_{LED}$ , and the switching frequency,  $f_{sw}$ . The capacitance required for the target LED ripple current,  $\Delta i_{LED}$ , is calculated using Equation below.

$$C_{OUT} = \frac{\Delta i_{L\_max}}{8 \times f_{sw} \times r_{LED} \times \Delta i_{LED}}$$

Equation 6

Where

$\Delta i_{(L\_max)}$  maximum ripple current of power inductor in worst case

$f_{sw}$  switching frequency

$r_{LED}$  equivalent resistance of total LED string

$\Delta i_{LED}$  target ripple current of LED string

When choosing the output capacitors, consider the ESR and ESL characteristics because they directly impact the LED current ripple. Ceramic capacitors are the best choice due to the following:

- Low ESR

- High ripple current rating

- Long lifetime

- Good temperature performance

With ceramic capacitor technology, consider the derating factors associated with higher temperature and DC bias operating conditions. It is recommended to use an X7R dielectric with a voltage rating greater than the maximum LED stack voltage.

### 6) Input Capacitor Calculation

The input capacitor buffers the input voltage for transient events and decouples the converter from the supply. It is recommended to use a 10 $\mu$ F input capacitor across the VIN pin and PGND placed close to the device and connected using wide traces. X7R-rated ceramic capacitors are the best choice due to the low ESR, high ripple current rating, and good temperature performance.

In addition, a small case size 100nF ceramic capacitor must be used across VIN to PGND, immediately adjacent to the device. This usage provides a high-frequency bypass for the control circuits internal to the device. These capacitors also suppress SW node ringing, which reduces the maximum voltage present on the SW node and EMI.

The capacitance can be increased to further limit the input voltage deviation during PWM dimming operation.

### 7) EMC Test Result

AL8891Q passed both conducted emission (CE) and radiated emission (RE) test on CISPR25 class 5 limit.

See below link for EMC test results in the AL8891QEY1 user guide.

<https://www.diodes.com/assets/Evaluation-Boards/AL8891Q-EV1-User-Guide.pdf>

---

## Application Information (continued)

---

### 8) Layout

The performance of any switching converter depends as much upon the layout of the PCB as the component selection. The AL8891Q is designed to meet the optimization requirements of PCB layout in the pin assignment. For example, VIN and GND pins are adjacent to each other, which is convenient for placing VIN bypass capacitors.

Radiated EMI is generated by the high  $di/dt$  components in pulsing currents in switching converters. The larger area covered by the path of a pulsing current, the more electromagnetic emission is generated. The key to minimize radiated EMI is to minimize the area of the pulsing current path, thus, placing high frequency ceramic bypass capacitor(s) as close as possible to the VIN and GND pins is necessary.

In addition, high  $dv/dt$  occurs on SW node during switching, so the trace between SW pin and inductor should be as short as possible, and just wide enough to carry the load current without excessive heating. Short and thick traces are highly recommended to minimize parasitic resistance. Besides, sensitive signal lines should be kept away from SW traces.

The following guidelines are provided to help users design a PCB with the best power conversion performance, thermal performance, and minimized generation of unwanted EMI.

1. Place high-frequency ceramic bypass CIN as close as possible to VIN and GND pins; a ceramic capacitor in small package (such as 0603) is still needed even if multiple input capacitors are implemented.

2. The high-current loop consisting of VIN, VOUT and PGND should be as compact as possible.

3. The bypass capacitors of VCC should be arranged close to the VCC pin and return to the PGND pin with the shortest connection.

4. It is recommended to use a four-layer board with 2oz top and bottom layers, and a dedicate ground plane on middle layer. Use a minimum 3 by 4 arrays of 10 mil thermal VIAs to connect the thermal pad to the system ground plane for heat dissipation purpose.

5. The SW and CBOOT nodes contain a lot of high-frequency noise, so the connection of these pins should be as short as possible, meanwhile, there should be sufficient width to conduct the current.

6. Sensitive analog signals, such as CSP and CSN need to be far away from the noisy nodes, and ground plane can be used as a shielding layer while routing these sensitive signals.

7. The resistor for FREQ pin  $R_{on}$  must be located as close to the pin as possible.

---

## Design Tools

---

- AL8891QEVT Demo Board

- Demo Board Gerber File for PCB Layout Reference

- Design Calculator

<https://www.diodes.com/assets/Design-and-Eval-Kits/Design-Kits/AL8891Q-Design-Calculator.xlsx>

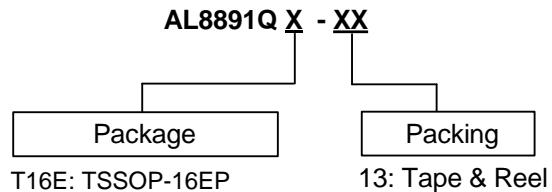

## Ordering Information

| Orderable Part Number | Package Code | Package    | Packing |             |

|-----------------------|--------------|------------|---------|-------------|

|                       |              |            | Qty.    | Carrier     |

| AL8891QT16E-13        | T16E         | TSSOP-16EP | 2500    | Tape & Reel |

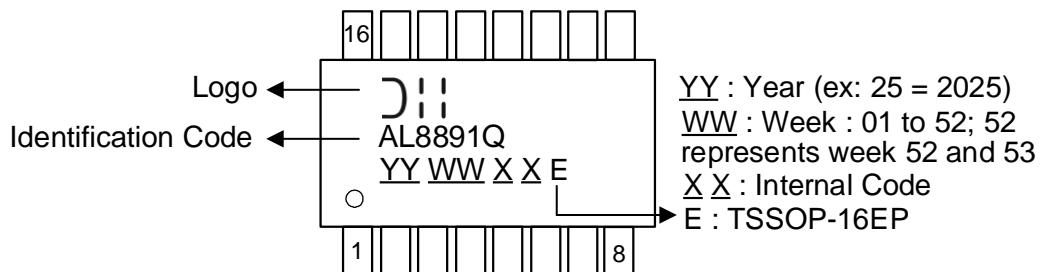

## Marking Information

TSSOP-16EP

(Top View – Not to Scale)

| Orderable Part Number | Package    | Identification Code |

|-----------------------|------------|---------------------|

| AL8891QT16E-13        | TSSOP-16EP | AL8891Q             |

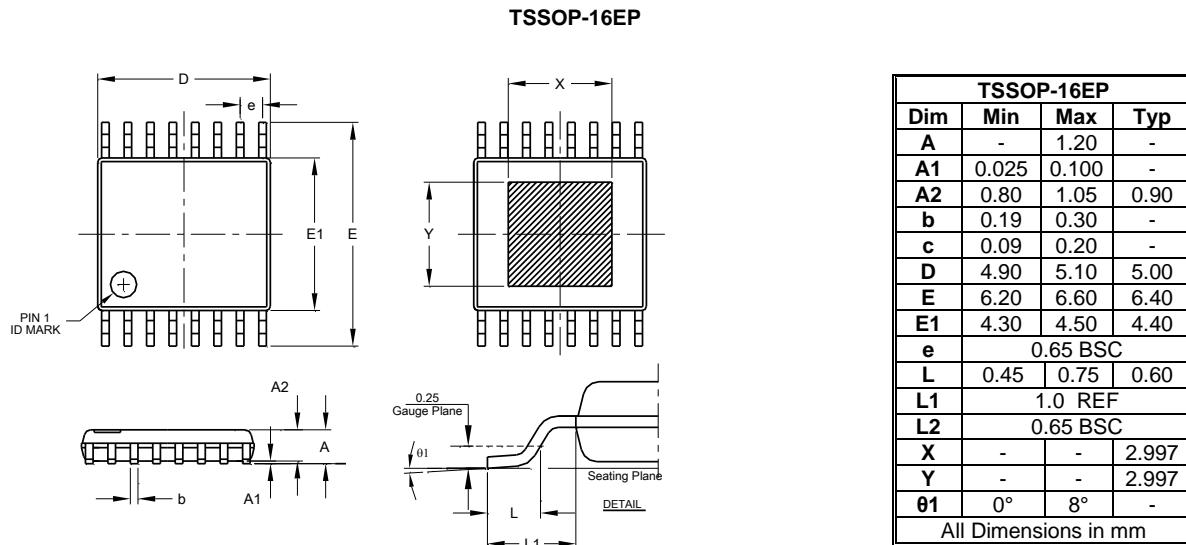

## Package Outline Dimensions

Please see <http://www.diodes.com/package-outlines.html> for the latest version.

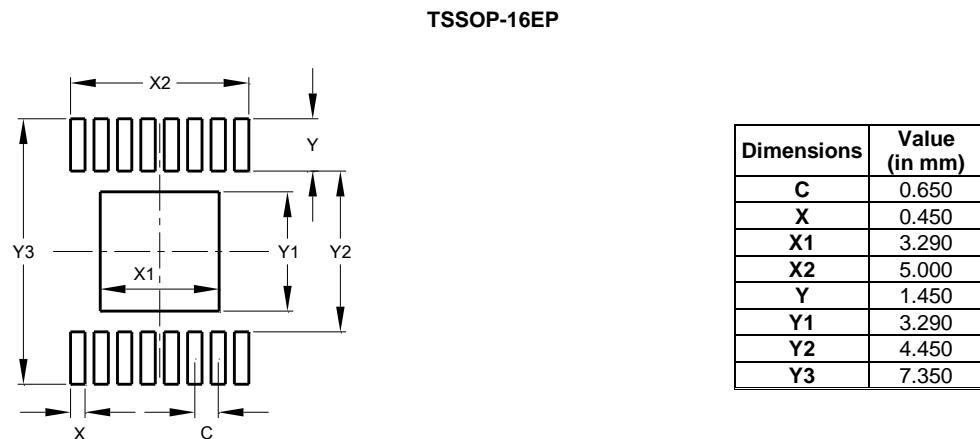

## Suggested Pad Layout

Please see <http://www.diodes.com/package-outlines.html> for the latest version.

## Tape and Reel Information

Please see <https://www.diodes.com/assets/Packaging-Support-Docs/AP02007.pdf> for the tape and reel details.

## Mechanical Data

### Package Type: TSSOP-16EP

- Moisture Sensitivity: Level 1 per JESD22-A113

- Terminals: Finish - Matte Tin Plated Leads, Solderable per M2003 JESD22-B102 <sup>②③</sup>

- Weight: 0.055 grams (Approximate)

# X-ON Electronics

Largest Supplier of Electrical and Electronic Components

***Click to view similar products for [LED Lighting Driver ICs](#) category:***

***Click to view products by [Diodes Incorporated manufacturer:](#)***

Other Similar products are found below :

[IS31BL3508A-TTLS2-TR](#) [NJW4617DL3-TE1](#) [BD6583MUV-E2](#) [NCV78723MW5BR2G](#) [LYT4321E](#) [CL520K4-G](#) [MIC3201YME](#)

[HV9910CNG-G](#) [TS19378CS RLG](#) [TS19452CS RLG](#) [KTD2037EWE-TR](#) [KTD2026BEWE-TR](#) [AL8891QT16E-13](#)

[AL1666+AL8116+AL5822EV1](#) [AL1783QT16E-13](#) [AL58221T24E-13](#) [AL58263QDKZW24-13](#) [AL58263T24E-13](#) [AL5836QT14-13](#)

[AL5873QT16E-13](#) [AL58818QFRZW40-13](#) [AL5887QJAZW52-13](#) [AL8116EV1](#) [AL8841QMP-13](#) [AL8841WT-7](#) [AL8853EV1](#) [AL8866QSP-13](#) [AP5725FDCG-7](#) [AP5726FDCG-7](#) [AP5726WUG-7](#) [DIO5661TST6](#) [DIO5662ST6](#) [TLD5099EPXUMA1](#) [ICL8830XUMA1](#) [IRS25401PBF](#)

[IS31FL3205-QFLS4-TR](#) [IS31FL3195-QFLS2-TR](#) [IS31FL3197-CLS2-TR](#) [IS31FL3296-UTLS4-TR](#) [IS31FL3726A-SALS4-TR](#) [IS32FL3265A-ZLA3-TR](#) [IS31FL3726A-QFLS4-TR](#) [KTZ8868EUAD-TB](#) [IS32LT3138-QWLA3-TR](#) [IS32LT3178-GRLA3-TR](#) [IS32LT3177-GRLA3-TR](#)

[KTD2027BEWE-TR](#) [KTD2052BEVAA-TR](#) [KTD2059EUAC-TR](#) [KTD2060EUAC-TR](#)