# 低功耗实时时钟芯(RTC)BL5372 用户手册 V1.2 (2012.11.12)

上海贝岭股份有限公司 Shanghai Belling Co., Ltd.

# 低功耗实时时钟芯片(RTC)BL5372

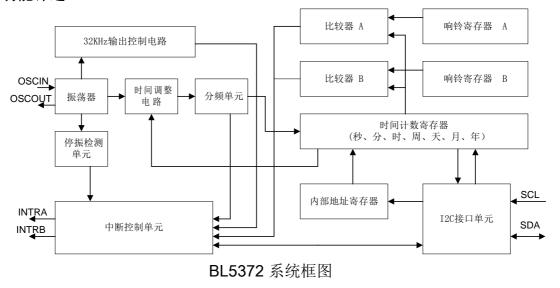

## 1. 概述

BL5372是一款低功耗实时时钟电路,通过I<sup>2</sup>C两线接口电路可以与CPU实时通信,主要用于一切需要提供时基的系统中。该芯片能够产生多种周期性中断脉冲(最长周期可长达1个月),还具有两套报时系统。BL5372内部集成一低功耗的稳压电源,故能够使恶劣的环境条件下仍能保持振荡器正常在很低的功耗工作(典型值:400nA@3.6V)。

BL5372具有晶振停振检测锁存的功能,通过检测该位可以检测内部时钟数据的有效性。

BL5372内置数字时间调整电路,可以保证时钟走时的高精度,并且有32KHz和

32.768KHz两种晶振选择模式。该产品与理光RS5C372A完全兼容。

## 2. 主要特点

- 超低功耗(典型值400nA@3.6V)

- 实时时钟(12时制或者24时制两种计时方式)

- 自动识别闰年、平年(2000~2099)

- BCD码表示的时钟计数(包括时、分、秒)和万年历(包括闰年、平年、月、日、周)

- 30秒数字校时功能

- 可控的32.768KHz(或者32KHz)输出

- 两个可编程闹钟输出

- 两路可编程方波输出,为CPU提供多种中断(一个月至一秒的周期性中断)

- 通过I<sup>2</sup>C两线接口与CPU相连(最大数据时钟频率为100KHz)

- 晶振停振检测锁存功能保证了时钟数据有效性

- 32KHz和32.768KHz晶振选择

- 高精度的时间调整电路,保证了时钟走时的精确

- 超低电压工作(计时电压最低可至1.8V,通讯电压最低可至1.8V)

- SOP8或TSSOP8封装

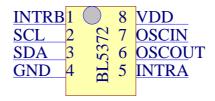

## 3. 管脚排列

## 4. 管脚功能说明

| PIN NO | PIN NAME | FUNCTION | IN/OUT |

|--------|----------|----------|--------|

| 1      | INTRB    | 中断输出B    | OUT    |

| 2      | SCL      | 串行时钟线    | IN     |

| 3      | SDA      | 串行数据线    | IN/OUT |

| 4      | GND      | 电源地      | POWER  |

| 5      | INTRA    | 中断输出A    | OUT    |

| 6      | OSCOUT   | 晶振的输出    | OUT    |

| 7      | OSCIN    | 晶振的输入    | IN     |

| 8      | VDD      | 工作电源电压   | POWER  |

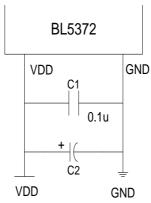

#### 4. 1 VDD和GND

VDD和GND分别是工作电源和接地引脚。当BL5372引脚上发生快速变化的信号时,为了防止噪声问题,要在BL5372旁边安置电容。可以如下图那样在尽可能靠近BL5372的地方,放置一个旁路电容。C2的电容容量可根据需要由用户确定,它可使引脚与地之间具有大电流通过能力。

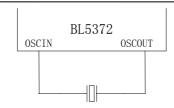

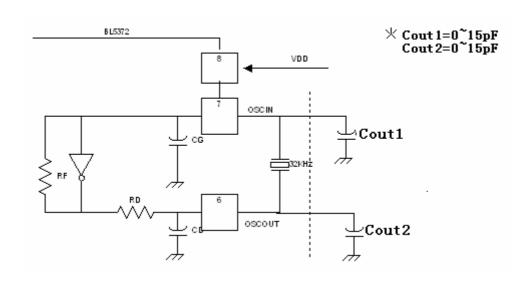

#### 4. 2 OSCIN和OSCOUT

在OSCIN与OSCOUT引脚之间连接一个晶体振荡器可以驱动片内振荡器。下图给出了晶体振荡器电路连接方式。参照晶振供应商的建议选用合适的晶振参数,因为它决定了外接部件提供的起振的可靠性和振荡的稳定性。一般情况下芯片上电起振时间为1.2-1.5s。振荡电路中选择电容容量时应当考虑分布电容的影响,为了减小输出失真,晶振和电容应当安装在尽可能靠近BL5372引脚的地方。

电话: 86-21-64850700 网址:www.belling.com.cn

外接的晶振连接

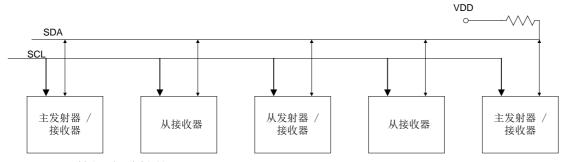

## 4. 3 SCL和SDA

SCL和SDA是两线接口的时钟线与数据线: SCL是时钟输入线; SDA为双向的I/O口, 既可以输入数据也可以输出数据。在外部电路板上,根据电压的不同,SCL、SDA可接不同的上拉电阻。

#### 4. 4 INTRA和INTRB

INTRA和INTRB是两个中断输出口且均为开漏输出,这样在BL5372使用时,INTRA和INTRB引脚必须要接一上拉电阻。INTRA可以输出周期中断、闹钟信号(ALARM-A、ALARM-B);INTRB可以输出32.768KHz 方波(使用32.768KHz晶振)、周期性中断脉冲、闹钟信号(ALARM-B),在上电时,默认输出 32.768kHz(使用 32.768KHz 晶振)方波。

#### 5. 功能详述

#### 5. 1 万年历功能

BL5372 可以与 CPU 交换年份(低两位)到秒的时钟数据。当年份的低两位能被 4 整除时,该年为闰年。它能够自动识别 2000-2099 年的年份。这些数据分别存放在 0H-6H 的寄存器中。

#### 5. 2 高精度的时间调整功能

BL5372 内部集成了数字化的时间精度调整电路(寄存器内部地址 7H),它根据高精度频率测量仪检测出的晶振本身的频率,再写入调整电路寄存器中,可以有效的调整时钟走时的精度(±1.5ppm)。调整范围: ±189ppm(±194ppm当使用32.000KHz晶振时),最小的调整步长为3ppm。采用该技术的优势:

- (1) 使用精度偏差较大的晶体也可以使时钟走时保持高精度。

- (2) 能够调整由于晶振季节性偏差导致时钟走不准情况。

- (3) 对于配有温度检测的系统,能有效的调整晶振精度随温度波动带来的走时偏差情况。

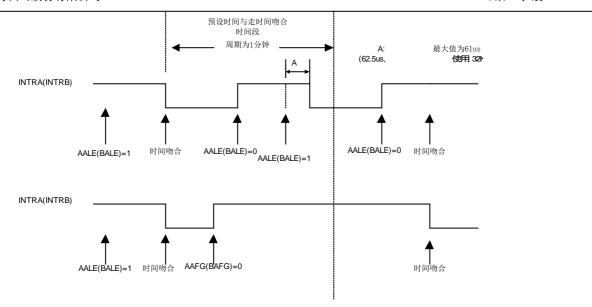

#### 5. 3 报时功能与周期性中断

(1)报时功能:定时寄存器内部地址为(8H~DH),当星期、时、分与定时寄存器预设的时间吻合时,两套定时中断信号就可以从INTRA、INTRB输出。其两套报时系统(ALARM-A,ALARM-B),根据所设定的时间,分别产生独立的中断信号。报时功能的开启与关闭可以通过控制寄存器 1 (内部地址 EH)中的 D7,D6 位选择,也可以通过星期来选择,这样就能选择每天或者一个星期中的几天产生特定的中断。ALARM-A 只能从INTRA输出,而 ALARM-B 可以从INTRA或者INTRB引脚输出,到底从哪个引脚输入通过控制寄存器 1 (内部地址 EH 的 D4、D5)可以选择的。

#### (2) 周期性中断:

BL5372 除了从 INTRA、INTRB 引脚能够输出闹钟信号,还能输出周期性中断脉冲。 该周期性中断频 率可以从 2Hz、1Hz、1/60Hz、1/3600Hz 到一个月,通过控制寄存器 1 (内部地址 EH 的低三位)选择性输出。周期性中断输出波形包括:标准的脉冲波形 (2Hz 和 1Hz) 和电平波形(每秒、每分、每时、每月)。

#### 5. 4 停振检测功能

BL5372 配有专门的寄存器(内部地址 FH 的 XSTP 位)来保存晶振停振信息。该功能能够判断上电、掉电、晶振停止振荡等情况,以确定时钟数据有效与否。

#### 5.5 脉冲输出功能

BL5372 可以从 INTRB 输出晶体振荡器的频率脉冲,脉冲的输出与否可以通过内部寄存器(内部地址 FH 的 CLEN 位)设定,但在上电的时候是保持脉冲输出状态。并且能够通过内部的寄存器(内部地址 7H 的 XSL 位)选择不同的晶体振荡器(32.768KHz 或者32.000KHz),可以输出两种频率的脉冲。

#### 5. 6 控制单元

控制单元是 BL5372 的重要部分,整个电路的功能都在控制电路的控制下实现的。时

间显示的选择, 中断、报时的选择、标志以及输出口选择, 停振检测的信息都由控制电路发出。

#### 5. 7 内部地址的分配

| 内部地址 | 目录    | 功能                              |

|------|-------|---------------------------------|

| 0H   | 秒寄存器  | 以 BCD 码形式计数与存储秒                 |

| 1H   | 分寄存器  | 以 BCD 码形式计数与存储分                 |

| 2H   | 时寄存器  | 以 BCD 码形式计数与存储时                 |

| 3H   | 周寄存器  | 以 BCD 码形式计数与存储周                 |

| 4H   | 天寄存器  | 以 BCD 码形式计数与存储天                 |

| 5H   | 月寄存器  | 以 BCD 码形式计数与存储月                 |

| 6H   | 年寄存器  | 以 BCD 码形式计数与存储年                 |

| 7H   | 时间调整  | 存储晶振的修正参数及外部晶振选择控制              |

| 8H   | 分定时 A | 存储定时器 A 分的数据                    |

| 9H   | 时定时 A | 存储定时器 A 时的数据                    |

| AH   | 天定时 A | 存储定时器 A 星期的数据                   |

| BH   | 分定时 B | 存储定时器 B 分的数据                    |

| CH   | 时定时 B | 存储定时器 B 时的数据                    |

| DH   | 天定时 B | 存储定时器 B 星期的数据                   |

| EH   | 控制 1  | 存储响铃使能、中断输出口选择、周期性中断的周期<br>选择信息 |

| FH   | 控制 2  | 存储时间显示选择、中断与报时标志、停振检测信<br>息     |

#### 5. 8 内部寄存器详细说明

## 符号定义:

- 1 "缺省"操作指当 XSTP 为"1"(上电,掉电或者停振后再起振)时,执行读操作。

- 2 "-"代表操作无效。

- 3 "P/A\_"表示 P 为高电平有效, A 为低电平有效, 以此类推。

#### 5. 8. 1 时钟计数器(内部地址 0-2H)

■ 时间数字显示(BCD 码显示):

秒计数: 00-59; 当从 59 变成 00 时, 会进位至分。

分计数: 00-59; 当从 59 变成 00 时, 会进位至时。

时计数: 当从 11PM 变成 12AM 或者说 23 变成 00 时(参看后面的 12\_/24 时制的说明),会进位至天 和星期。

■ 设置时钟时,应该设置实际中出现的时间,这样才能确保时钟正确的显示时间。

#### 5. 8. 1-1 秒寄存器 (内部地址 0H)

| D7 | D6  | D5  | D4  | D3 | D2 | D1 | D0 | 操作 |

|----|-----|-----|-----|----|----|----|----|----|

| _  | S40 | S20 | S10 | S8 | S4 | S2 | S1 | 写  |

| 0  | S40 | S20 | S10 | S8 | S4 | S2 | S1 | 读  |

| 0  | _   | _   | _   | _  | -  | _  | _  | 缺省 |

## 5. 8. 1-2 分寄存器 (内部地址 1H)

| D7 | D6  | D5  | D4  | D3 | D2 | D1 | D0 | 操作 |

|----|-----|-----|-----|----|----|----|----|----|

| _  | M40 | M20 | M10 | M8 | M4 | M2 | M1 | 写  |

| 0  | M40 | M20 | M10 | M8 | M4 | M2 | M1 | 读  |

| 0  | -   | -   | ı   | I  | I  | _  | ı  | 缺省 |

#### 5. 8. 1-3 时寄存器 (内部地址 2H)

| D7 | D6 | D5   | D4  | D3 | D2 | D1 | D0 | 操作 |

|----|----|------|-----|----|----|----|----|----|

| _  | _  | H20  | H10 | H8 | H4 | H2 | H1 | 写  |

|    |    | P/A_ |     |    |    |    |    |    |

| 0  | 0  | H20  | H10 | H8 | H4 | H2 | H1 | 读  |

|    |    | P/A_ |     |    |    |    |    |    |

| 0  | 0  | _    | _   | _  | _  | _  | _  | 缺省 |

注意: "P/A\_"的意思: 在 12 时制下,该位为"1"代表 PM,该位为"0"代表 AM。

#### 5. 8. 2 星期寄存器 (内部地址 3H)

- 当天计数加"1"时,星期计数也加"1"。

- 星期计数的显示 (特定的进位表示):

$(W4, W2, W1) = (0, 0, 0) \rightarrow (0, 0, 1) \rightarrow \cdots \rightarrow (1, 1, 0) \rightarrow (0, 0, 0)$

- 定义: 星期天为(0,0,0); 星期一为(0,0,1); ……; 星期六为(1,1,0)。

- (W4, W2, W1) 不能设为(1, 1, 1)。

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 操作 |

|----|----|----|----|----|----|----|----|----|

| _  | _  | _  | _  | _  | W4 | W2 | W1 | 写  |

| 0  | 0  | 0  | 0  | 0  | W4 | W2 | W1 | 读  |

| 0  | 0  | 0  | 0  | 0  | _  | _  | _  | 缺省 |

#### 5. 8. 3 万年历(内部地址 4-6H)

■ 万年历能够自动识别闰年和平年且用 BCD 码显示。

天计数: 1~31(一月、三月、五月、七月、八月、十月和十二月)

1~30(四月、六月、九月、十一月)

1~29 (闰年的二月)

1~28 (平年的二月)

月计数: 1~12; 当从 12 变成 1 时,会进位至年寄存器。

年计数: 00~99 其中 00, 04, 08, ……, 92, 96 为闰年。

■ 设置万年历时,应该设置实际中出现的日期,这样才能确保万年历正确的显示日期。

#### 5. 8. 3-1 天寄存器 (内部地址 4H)

| D7 | D6 | D5  | D4  | D3 | D2 | D1 | D0 | 操作 |

|----|----|-----|-----|----|----|----|----|----|

| _  | _  | D20 | D10 | D8 | D4 | D2 | D1 | 写  |

| 0  | 0  | D20 | D10 | D8 | D4 | D2 | D1 | 读  |

| Λ  | 0  | _   | _   | _  | _  | _  | _  | 缺省 |

#### 5. 8. 3-2 月寄存器(内部地址 5H)

| D7 | D6 | D5 | D4   | D3  | D2  | D1  | D0  | 操作 |

|----|----|----|------|-----|-----|-----|-----|----|

| _  | 1  | _  | MO10 | MO8 | MO4 | M02 | MO1 | 写  |

| 0  | 0  | 0  | MO10 | MO8 | MO4 | MO4 | MO1 | 读  |

| 0  | 0  | 0  | -    | _   | _   | _   | _   | 缺省 |

#### 5. 8. 3-3 年寄存器 (内部地址 6H)

| D7  | D6  | D5  | D4  | D3 | D2 | D1 | D0 | 操作 |

|-----|-----|-----|-----|----|----|----|----|----|

| Y80 | Y40 | Y20 | Y10 | Y8 | Y4 | Y2 | Y1 | 写  |

| Y80 | Y40 | Y20 | Y10 | Y8 | Y4 | Y2 | Y1 | 读  |

| _   | _   | _   | -   | _  | -  | _  | _  | 缺省 |

#### 5. 8. 4 数字化时间调整寄存器(内部地址 7H)

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 操作 |

|-----|----|----|----|----|----|----|----|----|

| XSL | F6 | F5 | F4 | F3 | F2 | F1 | F0 | 写  |

| XSL | F6 | F5 | F4 | F3 | F2 | F1 | F0 | 读  |

| 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 缺省 |

#### XSL

XSL\_是晶振选择位: XSL\_为 "0" (缺省状态)选择 32.768KHz; XSL\_为 "1" 选择 32KHz。

#### F6~F0

时间调整电路是在当秒计数为 00, 20, 40 时刻,根据预先设置的数据改变一秒钟内的计数周期的 大小。通常每 32768 个时钟脉冲(32000 个,当使用 32.000KHz 晶振时)才为 1 秒。对寄存器预设初值, 才能激活调整电路工作。

当 F6 为 "0" 时,产生 1 秒的寄存器计数脉冲将增加((F5, F4, F3, F2, F1, F0)-1)\*2 个脉冲。

当 F6 为 "1" 时,产生 1 秒的寄存器计数脉冲将减少((F5\_, F4\_, F3\_, F2\_, F1 , F0 ) +1) \*2个脉冲。

当(F6, F5, F4, F3, F2, F1, F0)预设为(\*, 0, 0, 0, 0, 0, \*)时,产生 1秒的寄存器计数脉冲不变。

例如(使用 32.768KHz 晶振时): 当(F6, F5, F4, F3, F2, F1, F0)=(0, 1, 0, 1, 0, 0, 1)且当 00, 20, 40 秒时刻时,寄存器计数脉冲变为: 32768+(41-1)\*2=32848。

当 (F6, F5, F4, F3, F2, F1, F0) = (0, 0, 0, 0, 0, 0, 1) 且当 00, 20, 40 秒时

刻时,寄存器计数脉冲保持不变。

当(F6, F5, F4, F3, F2, F1, F0) = (1, 1, 0, 1, 0, 0, 1) 且当 00, 20, 40 秒时刻时, 寄存器计数脉冲变为: 32768+(-23+1)\*2=32724。

每 20 秒增加 2 个时钟脉冲: 2/(32768\*20)=3.051ppm(3.125ppm,当使用 32.000KHZ 晶振时),将使时钟走时滞后约 3ppm,同样,每 20 秒减少 2 个时钟脉冲,将会使时钟超前约 3ppm,因此时钟走时精度为±1.5ppm。不过,值得注意的是时间调整电路仅调整是时钟走时,不对晶振本身振荡频率调整,所以 32.768KHz 脉冲输出没有变化。

#### 5. 8. 5 定时寄存器(ALARM-A 内部地址 8-AH: ALARM-B 内部地址 B-DH)

## 5. 8. 5-1 ALARM-A 分寄存器(内部地址 8H)

| D7 | D6   | D5   | D4   | D3  | D2  | D1  | D0  | 操作 |

|----|------|------|------|-----|-----|-----|-----|----|

| _  | AM40 | AM20 | AM10 | AM8 | AM4 | AM2 | AM1 | 写  |

| 0  | AM40 | AM20 | AM10 | AM8 | AM4 | AM2 | AM1 | 读  |

| 0  | _    | _    | ı    | ı   | 1   | ı   | _   | 缺省 |

## 5. 8. 5-2 ALARM-B 分寄存器(内部地址 BH)

| D7 | D6   | D5   | D4   | D3  | D2  | D1  | D0  | 操作 |

|----|------|------|------|-----|-----|-----|-----|----|

| _  | BM40 | BM20 | BM10 | BM8 | BM4 | BM2 | BM1 | 写  |

| 0  | BM40 | BM10 | BM10 | BM8 | BM4 | BM2 | BM1 | 读  |

| 0  | _    | -    | I    | I   | I   | _   | _   | 缺省 |

## 5. 8. 5-3 ALARM-A 时寄存器(内部地址 9H)

| D7 | D6 | D5    | D4   | D3  | D2  | D1  | D0  | 操作 |

|----|----|-------|------|-----|-----|-----|-----|----|

| _  | _  | AH20  | AH10 | AH8 | AH4 | AH2 | AH1 | 写  |

|    |    | AP/A_ |      |     |     |     |     |    |

| 0  | 0  | AH20  | AH10 | AH8 | AH4 | AH2 | AH1 | 读  |

|    |    | AP/A_ |      |     |     |     |     |    |

| 0  | 0  | _     | _    | -   | _   | _   | _   | 缺省 |

注意: "AP/A\_"的意思: 在 12 时制下,该位为"1"代表 PM,该位为"0"代表 AM。

#### 5. 8. 5-4 ALARM-B 时寄存器 (内部地址 CH)

| D7 | D6 | D5    | D4   | D3  | D2  | D1  | D0  | 操作 |

|----|----|-------|------|-----|-----|-----|-----|----|

| _  | -  | BH20  | BH10 | BH8 | BH4 | BH2 | BH1 | 写  |

|    |    | BP/A_ |      |     |     |     |     |    |

| 0  | 0  | BH20  | BH10 | BH8 | BH4 | BH2 | BH1 | 读  |

|    |    | BP/A_ |      |     |     |     |     |    |

| 0  | 0  | _     | -    | ı   | ı   | _   | -   | 缺省 |

注意: "BP/A\_"的意思: 在 12 时制下,该位为"1"代表 PM,该位为"0"代表 AM。

#### 5. 8. 5-5 ALARM-A 周寄存器(内部地址 AH)

| D7 | D6  | D5  | D4  | D3  | D2  | D1  | D0  | 操作 |

|----|-----|-----|-----|-----|-----|-----|-----|----|

| _  | AW6 | AW5 | AW4 | AW3 | AW2 | AW1 | AWO | 写  |

| 0  | AW6 | AW5 | AW4 | AW3 | AW2 | AW1 | AWO | 读  |

| 0  | _   | _   | 1   | _   | ı   | 1   | 1   | 缺省 |

## 5. 8. 5-6 ALARM-B 周寄存器(内部地址 DH)

| D7 | D6  | D5  | D4  | D3  | D2  | D1  | D0  | 操作 |

|----|-----|-----|-----|-----|-----|-----|-----|----|

| _  | BW6 | BW5 | BW4 | BW3 | BW2 | BW1 | BW0 | 写  |

| 0  | BW6 | BW5 | BW4 | BW3 | BW2 | BW1 | BW0 | 读  |

| 0  | _   | _   | _   | _   | ı   | _   | ı   | 缺省 |

- ALARM-A, ALARM-B 时寄存器 D5 位, 在 12 时制显示中置 "0"表示 AM, 置 "1"表示 PM: 在 24 时制显示中表示小时的 10 位。

- 使用报时功能时,必须设置实际中出现的时间,以避免报时功能出错现象。

- 在 12 时制显示中,零晨 0 点应该设置"12",正午 0 点应该设置"32"。

- AW0~AW6 (BW0~BW6) 对应着周寄存器 (0, 0, 0) ~ (1, 1, 0)。

- 当设置 AW0~AW6 (BW0~BW6) 全部为"0"时,报时功能不起作用。

## 报时时间设置举例

| 预设时间             |   |   |   | 星期 |   |    |   |     | 12 | 付制  |    |     | 24 🗈 | 付制  |    |

|------------------|---|---|---|----|---|----|---|-----|----|-----|----|-----|------|-----|----|

|                  | 日 | _ |   | =  | 四 | 五. | 六 | 10H | 1H | 10M | 1M | 10H | 1H   | 10M | 1M |

| 00:00AM<br>每天    | 1 | 1 | 1 | 1  | 1 | 1  | 1 | 1   | 2  | 0   | 0  | 0   | 0    | 0   | 0  |

| 05:27AM<br>每天    | 1 | 1 | 1 | 1  | 1 | 1  | 1 | 0   | 5  | 2   | 7  | 0   | 5    | 2   | 7  |

| 11:59AM<br>每天    | 1 | 1 | 1 | 1  | 1 | 1  | 1 | 1   | 1  | 5   | 9  | 1   | 1    | 5   | 9  |

| 00:00PM<br>周一~周五 | 0 | 1 | 1 | 1  | 1 | 1  | 0 | 3   | 2  | 0   | 0  | 1   | 2    | 0   | 0  |

| 05:56PM<br>周三    | 0 | 0 | 0 | 1  | 0 | 0  | 0 | 2   | 5  | 5   | 6  | 1   | 7    | 5   | 6  |

| 11:59PM<br>二、四、六 | 0 | 0 | 1 | 0  | 1 | 0  | 1 | 3   | 1  | 5   | 9  | 2   | 3    | 5   | 9  |

## 5. 8. 6 控制寄存器 1 (内部地址 EH)

| D7   | D6   | D5  | D4  | D3   | D2  | D1  | D0  | 操作      |

|------|------|-----|-----|------|-----|-----|-----|---------|

| AALE | BALE | SL2 | SL1 | TEST | CT2 | CT1 | CT0 | 写       |

| AALE | BALE | SL2 | SL1 | TEST | CT2 | CT1 | CT0 | 读       |

| 0    | 0    | 0   | 0   | 0    | 0   | 0   | 0   | *<br>缺省 |

#### AALE, BALE

■ ALARM-A, ALARM-B 使能位。

| AALE, BALE | 描述                    | 操作 |

|------------|-----------------------|----|

| 0          | 禁止 ALARM-A,ALARM-B 中断 | 缺省 |

| 1          | 允许 ALARM-A,ALARM-B 中断 |    |

#### SL2, SL1

■ 中断输出选择位。

| SL2 | SL1 | 描述                           | 操作 |

|-----|-----|------------------------------|----|

| 0   | 0   | ALARM-A,ALARM-B,周期性中断从       | 缺省 |

|     |     | INTRA 输出                     |    |

| 0   | 1   | ALARM-A,周期性中断从 INTRA 输出32K 时 |    |

|     |     | 钟脉冲,ALARM-B 从 INTRB 输出       |    |

| 1   | 0   | ALARM-A,ALARM-B 从 INTRA 输出   |    |

|     |     | 32K 时钟脉冲,周期性中断从 INTRB 输出     |    |

| 1   | 1   | ALARM-A 从 INTRA 输出从 INTRB 输出 |    |

|     |     | 32K 时钟脉冲,ALARM-B,周期性中断从      |    |

|     |     | INTRB 输出                     |    |

■ 设置 SL2、SL1 位,能够确定两报时脉冲(ALARM-A,ALARM-B),周期性中断 (INT), 32K 时钟脉冲是从 INTRA 还是从 INTRB 引脚输出。

#### **TEST**

■ BL5372 测试位。

| TES | 描述     | 操作 |

|-----|--------|----|

| 0   | 正常工作模式 | 缺省 |

| 1   | 测试模式   |    |

■ 该位用于 BL5372 测试。在正常工作时设置 TEST 为"0"。

## CT2, CT1, CT0

■ 周期性中断选择位。

| CT2 | CT1 | CT0 |      | 描述                    |  |  |  |  |

|-----|-----|-----|------|-----------------------|--|--|--|--|

|     |     |     | 波形模式 | 周期与 INTRA(INTRB)下降沿时刻 |  |  |  |  |

| 0   | 0   | 0   | _    | INTRA(INTRB)为高电平      |  |  |  |  |

| 0   | 0   | 1   | _    | INTRA(INTRB)为低电平      |  |  |  |  |

| 0   | 1   | 0   | 脉冲模式 | 2Hz(占空比 50%)          |  |  |  |  |

| 0   | 1   | 1   | 脉冲模式 | 1Hz(占空比 50%)          |  |  |  |  |

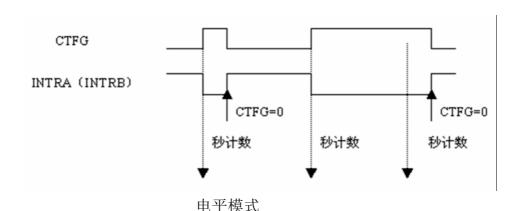

| 1   | 0   | 0   | 电平模式 | 每秒(与秒计数同步)            |  |  |  |  |

| 1   | 0   | 1   | 电平模式 | 每分(每分00秒)             |  |  |  |  |

| 1   | 1   | 0   | 电平模式 | 每时(每时00分:00秒)         |  |  |  |  |

| 1   | 1   | 1   | 电平模式 | 每月(每月第1天00时:00分:00秒)  |  |  |  |  |

■ 脉冲模式:输出 2Hz, 1Hz 时钟脉冲。

2Hz 时钟脉冲输出模式: 0.496 秒时钟脉冲与 0.504 秒时钟交替输出。

1Hz 时钟脉冲输出模式:占空比为 50.4%。

■ 电平模式:每秒、每分或者每月的周期性中断,可以从 INTRA (INTRB) 引脚输出低电平。注意:当时间调整电路作用时,每 20 秒会改变周期性中断脉冲大小。

脉冲模式:脉冲的低电平最大变化范围±3.784ms(当选择 32KHz 晶振时, ±3.875ms)。如:1Hz 脉冲输出时,占空比变化范围为 50± 0.3784%(当选择 32KHz 晶振时,50±0.3875%)。

电平模式:一秒最大变化范围±3.784ms(当选择 32KHz 晶振时, ± 3.875ms)。

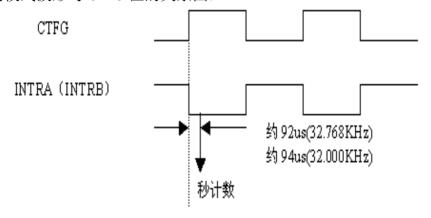

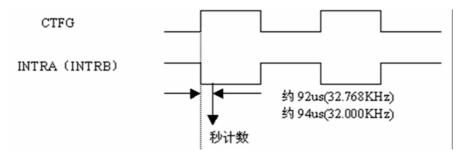

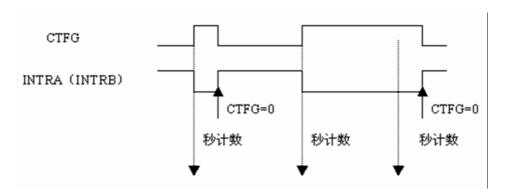

■ 以下是不同模式波形与 CTFG 位的关系图:

脉冲模式

5. 8. 7 控制寄存器 2 (内部地址 FH)

| D7 | D6 | D5     | D4   | D3   | D2   | D1   | D0   | 操作 |

|----|----|--------|------|------|------|------|------|----|

| _  | ı  | 12 /24 | ADJ  | CLEN | CTFG | AAFG | BAFG | 写  |

| 0  | 0  | 12 /24 | XSTP | CLEN | CTFG | AAFG | BAFG | 读  |

| 0  | 0  | _      | 1    | 0    | 0    | 0    | 0    | 缺省 |

12\_/24

#### ■ 12 /24 时制显示选择位。

| 12 /24 | 描述      |

|--------|---------|

| 0      | 12 时制显示 |

| 1      | 24 时制显示 |

■ 该位为 "0" 时表示 12 时制显示, 为 "1"表示 24 时制显示。

## 时间显示数字表

| 24 时制显示系统 | 12 时制显示系统 | 24 时制显示系统 | 12 时制显示系统 |

|-----------|-----------|-----------|-----------|

| 00        | 12(AM12)  | 12        | 32(PM12)  |

| 01        | 01(AM1)   | 13        | 21(PM1)   |

| 02        | 02(AM2)   | 14        | 22(PM2)   |

| 03        | 03(AM3)   | 15        | 23(PM3)   |

| 04        | 04(AM4)   | 16        | 24(PM4)   |

| 05        | 05(AM5)   | 17        | 25(PM5)   |

| 06        | 06(AM6)   | 18        | 26(PM6)   |

| 07        | 07(AM7)   | 19        | 27(PM7)   |

| 08        | 08(AM8)   | 20        | 28(PM8)   |

| 09        | 09(AM9)   | 21        | 29(PM9)   |

| 10        | 10(AM10)  | 22        | 30(PM10)  |

| 11        | 11(AM11)  | 23        | 31(PM11)  |

注意:不管是使用 12 时制还是 24 时制显示系统,都必有在写时钟数据之前进行选择。

## ADJ

■ ±30 秒调整位。

| ADJ | 描述    |

|-----|-------|

| 0   | 正常工作  |

| 1   | 秒调整操作 |

- 当 ADJ 置 "1" 时:

- (1) 秒计数在 "00" 与 "29" 之间: 秒计数复位为 "00", 分计数不变。

- (2) 秒计数在 "30" 与 "59" 之间: 秒计数复位为 "00", 分计数会加 "1"。

- 从写入 ADJ 为"1", 秒调整会在 122us(125us, 当使用 32KHz 晶振时)。

- ADJ 位只能执行写操作,不能被读取。

#### XSTP

■ 晶振停振检测位。

| XST | 描述   | 操作 |

|-----|------|----|

| 0   | 正常工作 |    |

| 1   | 停振检测 | 缺省 |

- XSTP 位可以检测晶振停振与否。

- 上电、掉电或者晶振停振后,该位自动置"1",检测该位可以判断时钟数据有效性。

当该位置"1" 后,XSL\_,F6~F0,CT2,CT1,CT0,AALE,BALE,SL2,SL1,CLEN\_和 TEST 位全部复位为"0"; INTRA 停止输出,INTRB 输出 32KHz 时钟脉冲。

■ 在正常工作时, XSTP 通过设置控制寄存器 2 (FH) 将其复位为"0"。

#### CLEN

■ 32KHz 脉冲输出使能位。

| CLEN | 描述            | 操作 |

|------|---------------|----|

| 0    | 允许 32KHz 脉冲输出 | 缺省 |

| 1    | 禁止 32KHz 脉冲输出 |    |

■ 设置该位为"0", INTRB 输出的脉冲频率与晶振的实际频率一致。

#### **CTFG**

■ 周期性中断标志位。

| CTF | 描述      | 操作 |

|-----|---------|----|

| 0   | 无周期性中断  | 缺省 |

| 1   | 周期性中断状态 |    |

- 当有周期性中断脉冲(INTRA 或者 INTRB 为低电平)输出时,该位将置"1"。

- 在电平中断模式中,可以写入 CTFG 位 "0"以终止中断过程。当写入"0"后,INTRA 或者 INTRB 全 部变成高电平。如果写入 CTFG 位 "1",没有任何变化。

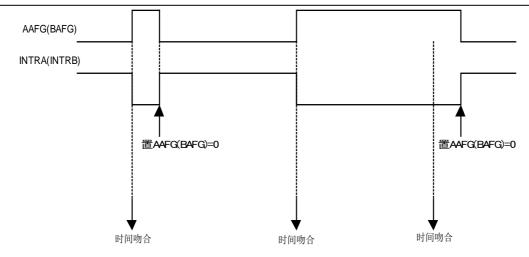

#### AAFG, BAFG

■ ALARM-A, ALARM-B 标志位

| ALARM-A, ALARM-B | 描述     | 操作 |

|------------------|--------|----|

| 0                | 无报时中断  | 缺省 |

| 1                | 报时中断状态 |    |

- 仅当 AALE, BALE 置"1"时,才能产生报时中断。当时钟时间与预置时间吻合时,该位会置"1"

- 在报时中断状态中,可以写入 AAFG, BAFG 位"0"以终止中断过程。当写入"0"后, INTRA 或者 INTRB 全部变成高电平。如果写入"1",没有任何变化。

- 当 AALE, BALE 位为 "0" 时, 禁止报时中断, AAFG, BAFG 位为 "0"。

- AAFG (BAFG) 与 INTRA (INTRB) 关系图如下:

AAFG (BAFG) 与 INTRA (INTRB) 关系图

## 5. 9 通信规则

## 5. 9. 1 两线的通信规则

通信协议规定:任何向 SDA 总线输出数据的设备、电路都看作是发射器;反之,从 SDA 总线上接收 数据的设备、电路都是接收器。控制数据传输的是主(MASTER)设备、电路;而受控的是从属电路(SLAVE) 电路。(如图所示)

典型的系统总线结构

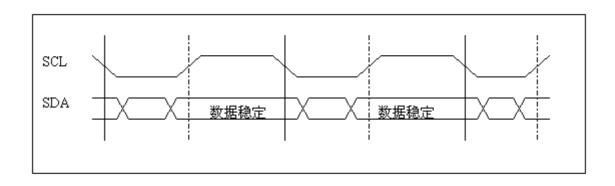

#### 5. 9. 2 数据有效性协议

数据传输协议规定:每个时钟周期传输一位数据。在时钟周期的高电平段 SDA 线上的数据必须保持稳定,因为这时 SDA 线的电平变化将被看作是"起始"或"终止"控制信号。(如图所示)

数据有效性协议

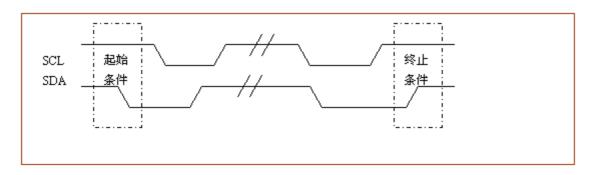

## 5. 9. 3 操作条件

SDA 和 SCL 在总线不工作时保持高电平。SCL 为高电平时,SDA 有一个从高电平到低电平跳变,这个跳变定义为"起始条件";反之,SDA 有一个从低电平到高电平的跳变的话则定义"终止条件"。(如图所示)

起始和终止条件

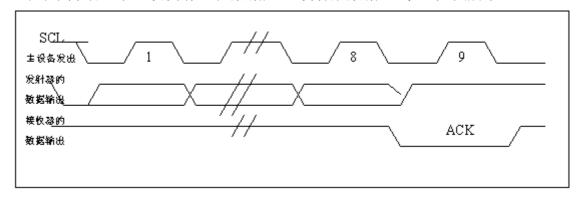

随着起始条件(START)的到达,主发射器必须发出一个"寻址命令字节",字节中包括电路类型标识符、指定电路地址和读写操作模式。总线上的某个接收器被选中后,会发出应答(ACK)信号,即 SDA 变为低电平。ACK 信号用来表明数据传输成功。发射器在SCL 时钟下降沿逐个连续发射 8 位数据后,会释放数据总线。(如图所示)

接收器的应答(ACK)信号

#### 5. 9. 4 器件寻址字节的定义

寻址字节的高有效 7 位(bit7—bit1)定义为器件类型标识符。对于 BL5372 而言,规定这 7 位是0110010,最低位 bit0 定义为是"写入"还是"读出"操作,该位是"1"就执行"读"操作,是"0"则选择"写"操作。(如图所示)

| I | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | віто |

|---|------|------|------|------|------|------|------|------|

| ı | DIII | DIIO | DIIJ | D114 | רווח | DIIZ | DILL | DITO |

|   | 0    | 1    | 1    | 0    | 0    | 1    | 0    | R/W  |

BIT7—BIT1: 器件标识符, BL5372 定义为 0110010

BITO: "写入"或"读出"操作的定义:

"1"为读操作,

"0"为写操作

## 器件寻址字节的定义

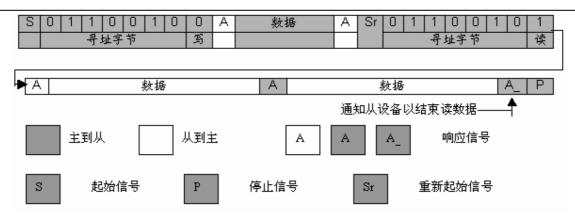

#### 5. 9. 5 两线数据传输格式

因为两线接口没有片选信号,取而代之的是 7 位寻址字节。所以第一个字节传送 7 位寻址字节和 1 位读/写命令位以唤醒要访问的电路。

BL5372 的寻址字节为(0110010)。 在数据传输/接收结束信号到来时,将结束其数据传输。如果只有起始信号,而没有结束信号,接着重新产生起始信号,还需要重新设置寻址字节,当传输方向需要改变时,就需要用这种传输方式传输数据。

| S | 0    | 1 | 1 | 0 | 0 | 1 | 0 | 0 | Α | 数据 | Α | 数据 | Α | Р |

|---|------|---|---|---|---|---|---|---|---|----|---|----|---|---|

|   | 寻址字节 |   |   | 写 |   |   |   |   |   |    |   |    |   |   |

主设备向从设备写入数据过程

| S | 0    | 1 | 1 | 0 | 0 | 1 | 0 | 1 | Α | 数据 | Α | 数据 | Α_ | Р |

|---|------|---|---|---|---|---|---|---|---|----|---|----|----|---|

|   | 寻址字节 |   |   |   | 读 |   |   |   |   |    |   |    |    |   |

主设备向从设备直接读取数据过程

响应信号 A 为低电平,A\_则为高电平 数据传输时改变其传输方向过程

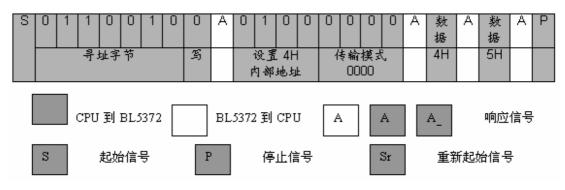

## 5. 9. 5-1 BL5372 数据传输的写模式

- (1) 先送 7 位寻址字节(0110010), 第 8 位送入写命令("0")。

- (2) 第9位是响应信号后,BL5372 进入写状态。

- (3)接下来 1个字节,高 4 位确定 BL5372 内部地址(0H~FH),低 4 位是传输模式(写状态时,定义传输模式为"0000")。

- (4) 再经过 1位的响应信号,就正常的写数据。

- (5)每写完 1字节数据之后,都经过1位的响应信号,才能写入下1字节的数据,如果想结束写操作,则需要在响应信号之后的1位产生停止信号即可。

BL5372 写数据实例(向 4H, 5H 地址写数据)

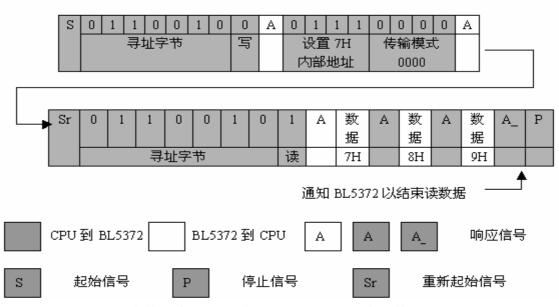

#### 5. 9. 5-2 BL5372 数据传输的读模式

BL5372 有三种读数据方法。

- (1) 从指定的内部地址中读取数据:

- 1) 与写模式的前 3 步一样。

- 2) 经一位响应信号后, 再重新产生起始信号以改变两线接口数据传输方向。

- 3)接着送 7位寻址字节,第8位读/写命令位为"1",BL5372 进入读数据状态。

- 4) 再经过 1位响应信号,就正常读数据。

5)每读出一个字节数据, CPU 送入一位响应信号(低电平), 才可以读下一字节数据, 如果想要结束读数据过程, CPU 送入的一位响应信号必须为高电平, 然后接着送入停止信号。

BL5372 第一种读数据实例(从内部地址 7H~9H 读取数据)

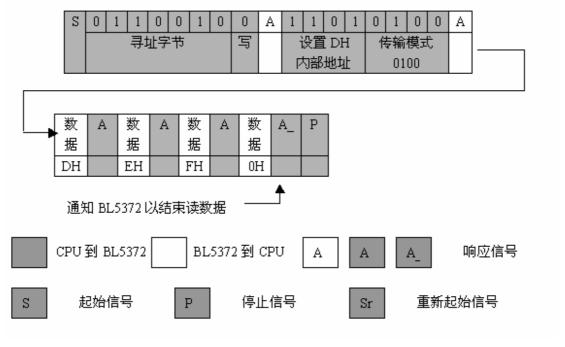

- (2) 指定的内部地址读数据(与第一种不同的是通过传输模式寄存器改变 BL5372 数据传输方向,此时设置传输模式寄存器为"0100")。

- 1) 与写模式前两步一样。

- 2)接下来 1 个字节,高四位为 BL5372 内部地址(0H~FH),低四位为传输模式(读状态时,定义传输模式为"0100")。

- 3) 再经过一个响应信号,就可以正常的读数据。

- 4)每读出一字节的数据后, CPU 都会发送一位响应信号(低电平), 才能读下一个地址的数据。 如果想结束本次读过程, CPU 发送一位响应信号(高电平)后再产生停止信号。

BL5372 第二种读数据实例(从内部地址 DH~0H 读取数据)

- (3) 直接读取数据(只能从 FH 地址开始依次读取数据)

- 1) 起始信号到来时,先送7位寻址字节,第8位读命令("1")。

- 2) 第9位响应信号后, BL5372进入读数据状态。

- 3) 在每读出一字节的数据后, CPU 都会发送一位响应信号(低电平), 才能 读下一个地址的数 据。如果想结束本次读过程, CPU 发送一位响应信号(高电平)后再产生停止信号。

BL5372 第三种读数据实例

#### 5. 9. 6 特殊条件下的数据传输

为了保证读写数据的有效性,BL5372的两线通信开始到结束仅在 0.5 秒到 1 秒之内,如果超过这一时间范围,时钟就会产生秒进位以及其它的时间进位,会导致所读写的数据与预想的不一致,从而导致数据出错。

在 BL5372 中,两线通信方式支持在通信过程中改变数据传输方向,在这种传输方式下,会在第一个起始信号到来之后的 0.5 秒到 1 秒之内自动终止本次通信。 简而言之,注意以下三点:

- (1) 从起始信号开始读/写数据,直到停止信号到来时,才结束本次通信过程。

- (2) 读/写操作过程必须在 0.5 秒到 1 秒之内完成。

- (3)每次读/写操作最好进行三次,尤其在读秒分时数据时,比较后两次数据,如果相等,则数据有效,如果不相等,则重新进行读数据。

#### BL5372 读数据出现的错误实例

(起始信号)→(读秒)→(读分)→(停止信号)→(起始信号)→(读时)→(停止信号) 假定读操作的起始时间为 09:59:59PM,当读完秒与分时,恰好产生时间进位为 10:00:00PM。这个时候读出的秒与分是 59:59,而读时时,刚变成了 10,故得到了错误的数据 10:59:59。

#### 5. 10 时钟走时精度调整

## 5. 10. 1 引子

一般的晶体振荡器是按照内部基频负载电容和振荡精度波动范围分类的(如: ±10ppm, ±20ppm 和±50ppm);因为晶体振荡器用在 IC 电路上频率的波动在室温下一般是±5~10ppm,这里的时钟精度在室温下是随着晶振自身特性的变化而改变的。

#### 5. 10. 2 电容微调频率

因为调整晶振的频率也就是调整时钟的频率。晶振频率的调整可以通过连接在晶体两边的电容 CIN和 COUT。因此 BL5372 时钟配合 CIN 和 COUT,振荡频率就可以以晶振的 CL 做为参考。 一般这种关系如下式:

$$CL = \frac{CG * CD}{CG + CD} + CS$$

CS: PCB 上的浮动电容。

电话: 86-21-64850700

网址:www.belling.com.cn

如果晶振频率偏高(时钟偏快)则减小 CL 电容值,反之,如果晶振频率偏慢(时钟偏慢)就要增大 CL 的电容值。

根据这个标准来选择最佳的 CL 来修正频率值达到时钟频率调整。如:频率偏高(时钟偏快)我们可以通过外加 COUT 电容来降低频率。考虑到 OSCIN 输入端无驱动能力,如果在 OSCIN 端外接电容可能会 造成晶体停振,建议只在 OSCOUT 输出端增加电容来调整频率 (见下图)。

#### 5. 10. 3 数字化时间精度调整电路

利用数字时间调整电路可以每 20 秒改变当前 1 秒内的脉冲计数的变化,从而达到时钟走时调整, 使 BL5372 保持高精度时钟走时。

(1) 当晶振频率\*1大于目标频率\*2(增加1秒内的计数脉冲)

调整数值\*

$$^3 = \frac{(晶振频率 - 目标频率 + 0.1)}{ 晶振频率 * \frac{2}{1} } = (晶振频率 - 目标频率) * 10 + 1$$

- 1) 晶振频率: 从 INTRB 引脚测出的脉冲频率。

- 2) 目标频率:标准的 32.768KHz 或者 32.000KHz 脉冲。

- 3) 调整数值:设置 F6~F0 的数值。该数值用二进制补码形式表示。

- (2) 当晶振频率等于目标频率(不需要改变 1 秒内的计数脉冲): 调整数值为 0、+1、-64、-63 或者缺省。

- (3) 当晶振频率小于目标频率(减少1秒内的计数脉冲):

计算调整数值大小实例

(1) 晶振频率=32770KHz; 目标频率=32768KHz。 调整数值=(32770-32768+0.1)

/(32770\*2/(32768\*20))=(32770-32768)\*10+1=21

故设置(F6, F5, F4, F3, F2, F1, F0) = (0, 0, 1, 0, 1, 0, 1)

(2) 晶振频率=32762KHz; 目标频=32768KHz。

调整数值=(32762-32768)/(32762\*2/(32768\*20))

= (32762 - 32768) \*10 = -60

因为-60 的七位二进制补码为 80h-3ch=44h, 故设置(F6, F5, F4, F3, F2, F1, F0) = (1, 0, 0, 0, 1, 0, 0)。 经过调整电路把时钟走调整后, 时钟走精度只与目标频率相差±1.5ppm(在室温下)。

#### 注意

- (1) 时间调整电路不能改变从 INTRB 输出的脉冲频率。

- (2) 最大调整范围:

- 1)振频率大于目标频率时,调整数值范围为(F6,F5,F4,F3,F2,F1,F0)=(0,0,0,0,0,0,1)到(0,1,1,1,1,1,1,1),实际可调范围将从-3.05ppm 到-189.2ppm(-3.125ppm 到-193.7ppm, 当使用 32.000KHz 晶振时)。

- 2)振频率小于目标频率时,调整数值范围为(F6, F5, F4, F3, F2, F1, F0)=(1, 1, 1, 1, 1, 1) 到(1, 0, 0, 0, 0, 1, 0),实际可调范围将从+3.05ppm 到+189.2ppm(+3.125ppm 到+193.8ppm, 当使用 32.000KHZ 晶振时)。

- (3) 当外接晶振与标准频率相差约±6Hz 时,均能使 BL5372 走时保持高精度。

- 5. 11 中断

- 5. 11. 1 中断系统

BL5372 的中断系统从 INTRA(INTRB)引脚输出波形有三种:

(1) 报时中断:

当报时寄存器预设值(星期、时、分)与时钟的走时吻合时,BL5372 就会向 CPU 产生报时中断,使 INTRA (INTRB)输出变为低电平。

- (2)周期性中断:根据不同周期性选择位,输出不同的波形。波形模式有脉冲模式与电平模式两种。

- (3) 32KHz 脉冲输出: 根据需要,可以有选择的输出 32KHz 时钟脉冲。

- 5. 11. 2 INTRA (INTRB) 输出控制(标志位,使能位,中断输出选择位) 上述三种中断方式,中断输出时,会产生中断标志位;中断使能位决定是否能够产生中断;中断选择位是选择中断从INTRA 还是从INTRB 输出。

|       | 标志位         | 使能位                  | 中断输出选择位(SL2, SL1)(D5, D4<br>EH) |        |        |        |  |

|-------|-------------|----------------------|---------------------------------|--------|--------|--------|--|

|       |             |                      |                                 | E.     | П)     |        |  |

|       |             |                      | (0, 0)                          | (0, 1) | (1, 0) | (1, 1) |  |

| 报时 A  | AAFG (D1FH) | AALE (D7EH)          | INTRA                           | INTRA  | INTRA  | INTRA  |  |

| 报时 B  | BAFG (DOFH) | BALE (D6EH)          | INTRA                           | INTRB  | INTRA  | INTRB  |  |

| 周期性   | CTFG (D2FH) | CT2 <sup>~</sup> CT0 | INTRA                           | INTRA  | INTRB  | INTRB  |  |

| 中断    |             | (D2~D0EH)            |                                 |        |        |        |  |

| 32KHz | NO          | CLEN_(D3FH)          | INTRB                           | INTRB  | INTRB  | INTRB  |  |

| 脉冲输   |             |                      |                                 |        |        |        |  |

| 出     |             |                      |                                 |        |        |        |  |

当上电(XSTP=1)时:

AALE=BALE=CT2=CT1=CT0=SL2=SL1=0。

INTRA 输出为高电平; INTRB 输出 32KHz 时钟脉冲。 当两个中断从同一个引脚输出时:

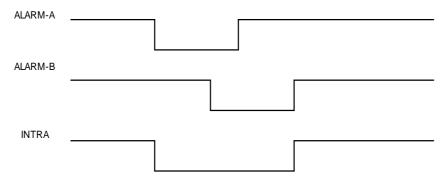

输出低电平波形会叠加,也就是两波形是逻辑或关系(见下图)。

#### 5. 11. 3 报时中断

设置报时时间应该在 AALE(BALE)为"0"时,设定报时时间(星期、时、分),之后设置 AALE(BALE)为"1",从此刻起到万年历走时与设定时间吻合时,则INTRA(INTRB)变成低电平。INTRA(INTRB)的输出与否是由 AALE(BALE)和 AAFG(BAFG)位来控制的。INTRA(INTRB)的输出情况请见下图。

#### 5. 11. 4 周期性中断

INTRA(INTRB)引脚通过中断周期选择位(CT2~CT0)和中断输出选择位(SL2,SL1)可以向 CPU 输出某个周期的中断信号。周期性中断周期选择位可以选择输出中断的模式:脉冲模式和电平模式。

| CT2 | CT1 | СТО | 描述   |                       |  |  |  |  |

|-----|-----|-----|------|-----------------------|--|--|--|--|

|     |     |     | 波形模式 | 周期与 INTRA(INTRB)下降沿时刻 |  |  |  |  |

| 0   | 0   | 0   | _    | INTRA(INTRB)为高电平      |  |  |  |  |

| 0   | 0   | 1   | -    | INTRA(INTRB)为低电平      |  |  |  |  |

| 0   | 1   | 0   | 脉冲模式 | 2Hz(占空比 50%)          |  |  |  |  |

| 0   | 1   | 1   | 脉冲模式 | 1Hz(占空比 50%)          |  |  |  |  |

| 1   | 0   | 0   | 电平模式 | 每秒(与秒计数同步)            |  |  |  |  |

| 1   | 0   | 1   | 电平模式 | 每分(00分:00秒)           |  |  |  |  |

| 1   | 1   | 0   | 电平模式 | 电平模式 每时(00时:00分:00秒)  |  |  |  |  |

| 1   | 1   | 1   | 电平模式 | 每月(每月第1天00时:00分:00秒)  |  |  |  |  |

脉冲模式:输出 2Hz,1HZ 时钟脉冲,波形关系图如下图。

2Hz 时钟脉冲输出模式: 0.496 秒时钟脉冲与 0.504 秒时钟交替输出。

1Hz 时钟脉冲输出模式:占空比为 50.4%。 电平模式:每秒,每分或者每月的周期性中断,可以从 INTRA (INTRB) 引脚输出低电平。 当时间调整电路作用时,每 20 秒会改变周期性中断脉冲大小。

脉冲模式: 脉冲的低电平最大变化范围±3.784ms (当选择 32KHz 晶振时, ± 3.875ms)。 例如 1Hz 脉冲输出时,占空比变化范围为 50±0.3784%

(当选择 32KHz 晶振时,50±0.3875%)。

电平模式:一秒最大变化范围±3.784ms(当选择 32KHz 晶振时, ±3.875ms)。

脉冲模式波形与 CTFG 位的关系图

电平模式波形与 CTFG 位的关系图

#### 5. 11. 5 32KHz 时钟脉冲输出

INTRB 能够输出晶体振荡器产生的 32KHz 时钟脉冲。当设置 CLEN\_为"1"时,INTRB 将为高。

32KHz 时钟脉冲的频率不受调整电路的影响(输出晶体振荡器的真实频率的脉冲)。 当上电时(XSTP=1),32KHz 时钟脉冲从 INTRB 输出。

## 5. 11. 6 晶振的停振检测功能

通过 XSTP 位可以判断晶振是否停振过,当检测到 XSTP="1"时,说明晶振曾经停振过,这时的读取的时钟数据是错误数据。

XSTP 变成"1"时,XSL\_,F6~F0,CT2,CT1,CT0,AALE,BALE,SL2,SL1,CLEN\_和 TEST 位全部 复位为"0"。

#### 注意

- (1) 上电复位时, XSTP 位置"1", 值得注意的是任何瞬间的断电可能使 XSTP 位置"1"。

- (2) 晶振停振后就会使 XSTP 位置"1",即使晶振再次起振,XSTP 位仍然保持"1",除非对内部地址 FH 进行写动作。

为了避免晶振停振现象, 应确保不发生下面情况

(1) 瞬间的掉电。

- (2) 晶振短接。

- (3) PCB 版上的噪声。

- (4) 供给电源电压超出于 BL5372 电压最值。

# 6. 电路特性参数

# 6.1 极限参数

| 符号   | 说明     | 条件           | 范围                    | 单位         |

|------|--------|--------------|-----------------------|------------|

| VDD  | 供给电压   |              | $-0.3^{\sim}+7.0$     | V          |

| VI   | 输入电压   | SCL, SDA     | $-0.3^{\sim}+7.0$     | V          |

| V01  | 输出电压1  | SDA          | $-0.3^{\sim}+7.0$     | V          |

| V02  | 输出电压 2 | INTRA, INTRB | $-0.3^{\sim}+12.0$    | V          |

| PD   | 电源功耗   | T0PT=25℃     | 300                   | mW         |

| TOPT | 工作温度   |              | -40 <sup>~</sup> +85  | $^{\circ}$ |

| TSTG | 储藏温度   |              | -55 <sup>~</sup> +125 | $^{\circ}$ |

# 6.2 直流参数

TOPT=-40°C~85°C

| 符号   | 说明    | 引脚           | 条件            | 最小值    | 典型值 | 最大值     | 单位 |

|------|-------|--------------|---------------|--------|-----|---------|----|

| VIH  | 输入高电平 | SCL, SDA     |               | 0.8VDD |     | 6. 0    | V  |

| VIL  | 输入低电平 | SCL, SDA     |               | -0.3   |     | 0. 3VDD | V  |

| IOL1 | 输出电流  | INTRA, INTRB | VOL1=0. 4V    | 1      |     |         | mA |

| I0L2 | 输出电流  | SDA          | VOL2=0.6V     | 7      |     |         | mA |

| IILK | 输入漏电流 | SCL          | VI=6V         | -1     |     | 1       | uA |

|      |       |              | VDD=6V        |        |     |         |    |

| IOZ  | 输出漏电流 | SDA, INTRA,  | V0=6V         | -1     |     | 1       | uА |

|      |       | INTRB        | VDD=6V        |        |     |         |    |

| VDD  | 工作电压  | VDD, GND     |               | 1.8    |     | 5. 5    | V  |

|      | 计时电压  |              |               | 1.8    |     | 5. 5    | V  |

| IDD  | 工作电流  | VDD          | VDD=3.6V,     |        | 0.4 |         | uA |

|      |       |              | T0PT=25℃      |        |     |         |    |

|      |       |              | SCL, SDA=3.6V |        |     |         |    |

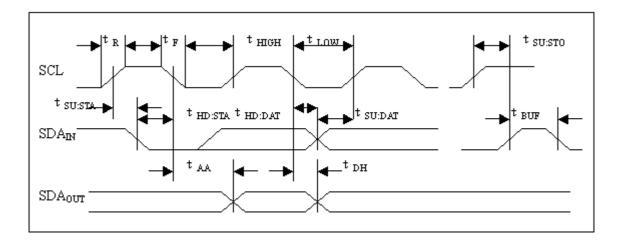

# 6.3 交流参数

$TA = -40^{\circ}C^{\sim} + 85^{\circ}C$ , VDD = 4.5 $V^{\sim}5.5V$

| 符号                                     | 参数             | 测试条件               | 最小值  | 最大值  | 单位  |

|----------------------------------------|----------------|--------------------|------|------|-----|

| $t_{\scriptscriptstyle{\mathtt{SCL}}}$ | SCL 时钟频率       |                    | 0    | 100  | KHz |

| $t_{\mathtt{low}}$                     | 时钟低周期          |                    | 4. 7 |      | us  |

| t <sub>HIGH</sub>                      | 时钟高周期          |                    | 5    |      | us  |

| $t_{\scriptscriptstyle{	ext{BUF}}}$    | 总线释放时间         | 在下一个数据传输之前         | 4. 7 |      | us  |

| t <sub>SU:STA</sub>                    | 起始条件建立时间       |                    | 4. 7 |      | us  |

| t <sub>SU:STO</sub>                    | 终止条件建立时间       |                    | 4. 7 |      | us  |

| t <sub>HD:STA</sub>                    | 起始条件保持时间       |                    | 4    |      | us  |

| t <sub>HD:STO</sub>                    | 终止条件保持时间       |                    | 4    |      | us  |

| t <sub>SU:DAT</sub>                    | 数据输入建立时间       |                    | 250  |      | ns  |

| t <sub>HD:DAT</sub>                    | 数据输入保持时间       |                    | 0    |      | ns  |

| $T_{\text{HD}}$                        | 数据输出保持时间       | SCL 下跳到 SDA 数据输出变化 | 0    |      | ns  |

| $t_{\scriptscriptstyleAA}$             | 时钟输出           | SCL 下跳到 SDA 数据输出有效 | 0.3  | 3. 5 | us  |

| $t_{\scriptscriptstyle R}$             | SCL 和 SDA 上升时间 |                    |      | 1    | us  |

| $t_{\scriptscriptstyle{F}}$            | SCL 和 SDA 下降时间 |                    |      | 300  | ns  |

| $t_{\mathtt{WR}}$                      | 写周期时间          |                    |      | 10   | ms  |

| $t_{\scriptscriptstyle \mathrm{I}}$    | 噪声尖波宽度         | SCL、SDA 输入的时间常数    |      | 100  | ns  |

总线时序图

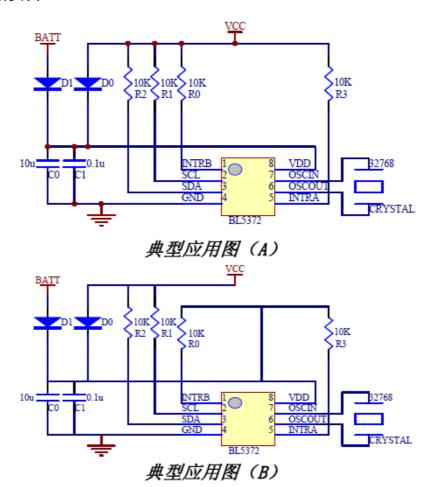

## 7. 典型应用

## 7. 1 典型应用实例

(1) C0、C1 分别是高频与低频的旁路电容(典型值 C0=10uF, C1=0.1uF)。

- (2) 限流电阻 R0-R3 的典型值为  $10K\Omega$ 。

- (3) BATT 与 VCC 电压关系满足:VBATT≤VVCC。

- (4) INTRA(INTRB)接上拉电阻 R 与两种接法: A、当备用电池供电时不使用 INTRA(B); B、当备用电 池供电时使用 INTRA(B)。

- (5) 为了提高 BL5372 的抗 EMC 干扰,可在系统电源与芯片 VDD 之间串接  $50\,\Omega\sim$ 100  $\Omega$  电阻

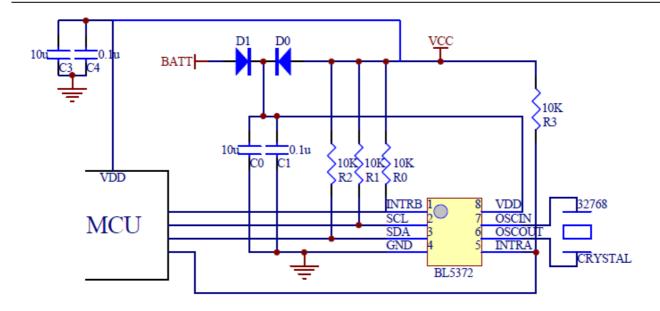

#### 7. 2 与 CPU 通信应用实例

(1) 用户在与 MCU 通信引脚之间串接  $20\,\Omega\sim30\,\Omega$  的电阻,能够提高 BL5372 在系统应用 中的抗电磁干扰

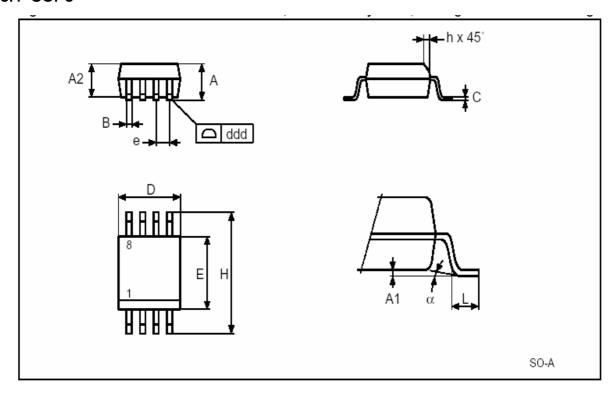

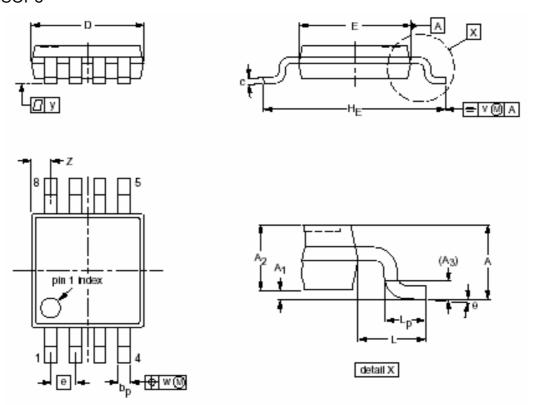

## 8. 封装尺寸

## 8.1 SOP8

| 符号  | mm    |       |       | inches |        |        |  |

|-----|-------|-------|-------|--------|--------|--------|--|

|     | min   | typ   | max   | min    | typ    | max    |  |

| A   | 1.35  | -     | 1. 75 | 0. 053 | -      | 0. 069 |  |

| A1  | 0. 10 | -     | 0. 25 | 0.004  | -      | 0. 010 |  |

| В   | 0. 33 | -     | 0. 51 | 0. 013 | -      | 0. 020 |  |

| С   | 0. 19 | -     | 0. 25 | 0.007  | -      | 0. 010 |  |

| D   | 4.80  | _     | 5. 00 | 0. 189 | -      | 0. 197 |  |

| ddd | -     | -     | 0. 10 | -      | -      | 0.004  |  |

| Е   | 3.80  | -     | 4. 00 | 0. 150 | -      | 0. 157 |  |

| е   | -     | 1. 27 | -     | _      | 0. 050 | -      |  |

| Н   | 5. 80 | -     | 6. 20 | 0. 228 | _      | 0. 244 |  |

| h   | 0. 25 | _     | 0. 50 | 0. 010 | _      | 0. 020 |  |

| L   | 0.40  | _     | 0. 90 | 0. 016 | _      | 0. 035 |  |

| α   | 0°    | -     | 8°    | 0°     | _      | 8°     |  |

# 8.2 TSSOP8

| 单位 | A max. | A1   | A2    | А3    | Вр    | С     | D <sup>(1)</sup> | E (2) | е    |

|----|--------|------|-------|-------|-------|-------|------------------|-------|------|

| mm | 1.10   | 0.15 | 0. 95 | 0. 25 | 0.32  | 0. 25 | 3. 10            | 4. 60 | 0.65 |

|    |        | 0.05 | 0.80  |       | 0. 12 | 0.10  | 2. 90            | 4. 20 |      |

| 单位 | HE    | L    | Lp    | v    | W   | у   | Z <sup>(1)</sup> | θ   |

|----|-------|------|-------|------|-----|-----|------------------|-----|

| mm | 6.70  | 0.94 | 0.80  | 0. 1 | 0.1 | 0.1 | 0.70             | 10° |

|    | 6. 10 |      | 0. 20 |      |     |     | 0.35             | 00  |

注: (1) 不包括每边塑料或者金属伸出的尺寸 0.15mm(最大值)

(2) 不包括每边塑料或者金属伸出的尺寸 0.25mm(最大值)

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Real Time Clock category:

Click to view products by Belling manufacturer:

Other Similar products are found below:

DS1302Z-LF 710029X MCP79400T-I/SN 879047C 405800G RX8900SA UA3 PURE SN RX8900SA UB3 PURE SN RX8130CE B0

RX8130CE BX PCF85263AUKZ RX-4035LC:B3 PURE SN RX-8564LC:B PURE SN RX-4571LC:B PURE SN RX-8803LCUB PURE SN BULK RX6110SA:B0 PURE SN RX8010SJ:B3 PURE SN RX-8035SA:AA PURE SN RX-8025SA:AC0 RX-8571SA:B0 PURE SN RX-8571LCB0 PURE SN RTC-8564JE:BB ROHS MCP79401-I/SN MCP7940N-E/SN RTC-8564JE RX4045SAA MCP7940M-I/P

BU9873FVT-GE2 DS3232SN# DS3231SN#T&R DS1743-100IND+ RX-8564LC:B3 PURE SN PT7C4307WEX PT7C4337WEX PCF85063TP/1Z PCF85063ATTAJ DS12CR887-5+ RX-4571SA:B3 PURE SN RX-8025NB:AA3 PURE SN RX8900CE UA3 RX-8571LC:B3 PURE SN PCF8583T/5.518 S-35190A-I8T1U 1339-2DVGI8 RX-8564LC:B0 PURE SN 1338-18DVGI8 R2051S01-E2-F RX8900CE:UB3 S-35390A-T8T1U R2043T-E2-F R2262L01-E2