# High Voltage High Current Controller for Battery Charging and Power Management

# **FEATURES**

- Complete High Performance Battery Charger When Paired with a DC/DC Converter

- Wide Input and Output Voltage Range: 3V to 60V

- Input Ideal Diode for Low Loss Reverse Blocking and Load Sharing

- Output Ideal Diode for Low Loss PowerPath™ and Load Sharing with the Battery

- Instant-On Operation with Heavily Discharged Battery

- Programmable Input and Charge Current: ±1% Accuracy

- ±0.25% Accurate Programmable Float Voltage

- Programmable C/X or Timer Based Charge Termination

- NTC Input for Temperature Qualified Charging

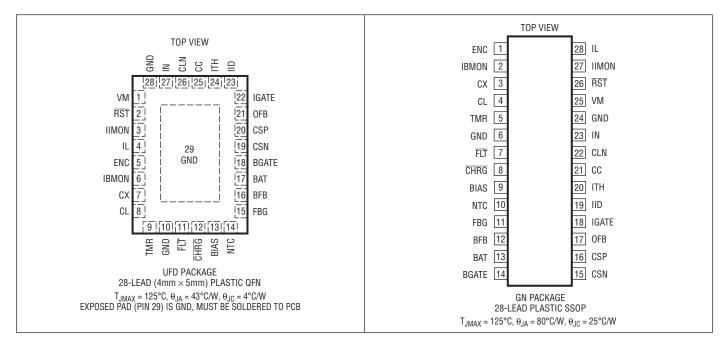

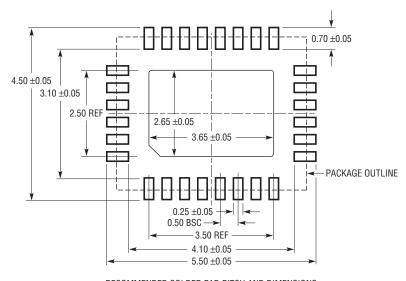

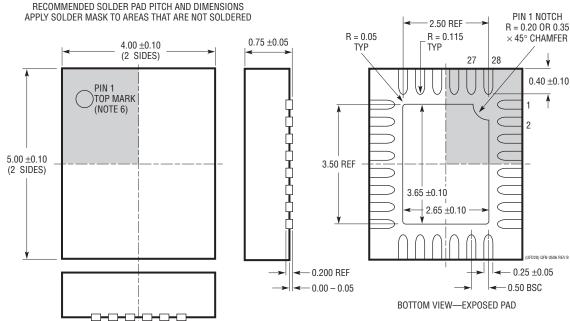

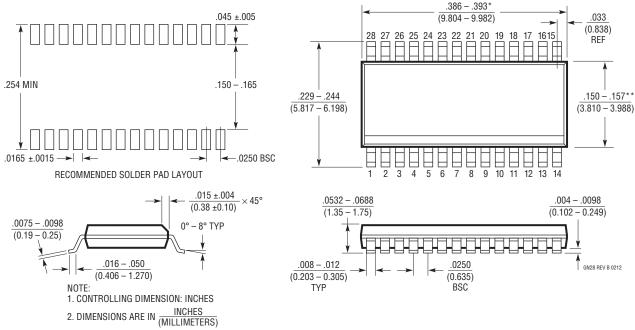

- 28-Lead 4mm × 5mm QFN or SSOP Packages

# **APPLICATIONS**

- High Power Battery Charger Systems

- High Performance Portable Instruments

- Industrial Battery Equipped Devices

- Notebook/Subnotebook Computers

# DESCRIPTION

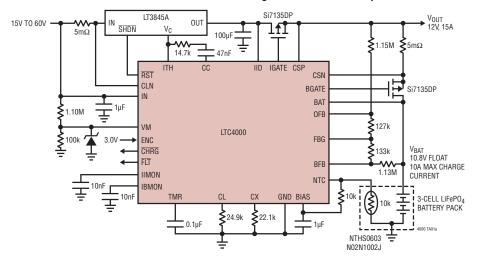

The LTC®4000 is a high voltage, high performance controller that converts many externally compensated DC/DC power supplies into full-featured battery chargers.

Features of the LTC4000's battery charger include: accurate ( $\pm 0.25\%$ ) programmable float voltage, selectable timer or current termination, temperature qualified charging using an NTC thermistor, automatic recharge, C/10 trickle charge for deeply discharged cells, bad battery detection and status indicator outputs. The battery charger also includes precision current sensing that allows lower sense voltages for high current applications.

The LTC4000 supports intelligent PowerPath control. An external PFET provides low loss reverse current protection. Another external PFET provides low loss charging or discharging of the battery. This second PFET also facilitates an instant-on feature that provides immediate downstream system power even when connected to a heavily discharged or short faulted battery.

The LTC4000 is available in a low profile 28-lead 4mm  $\times$  5mm QFN and SSOP packages.

$\overline{\mathcal{L}}$ , LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and PowerPath is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

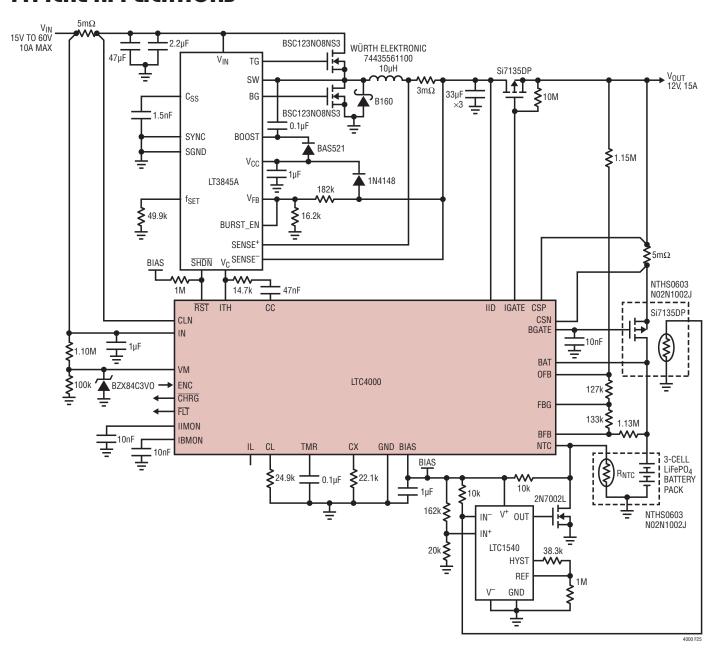

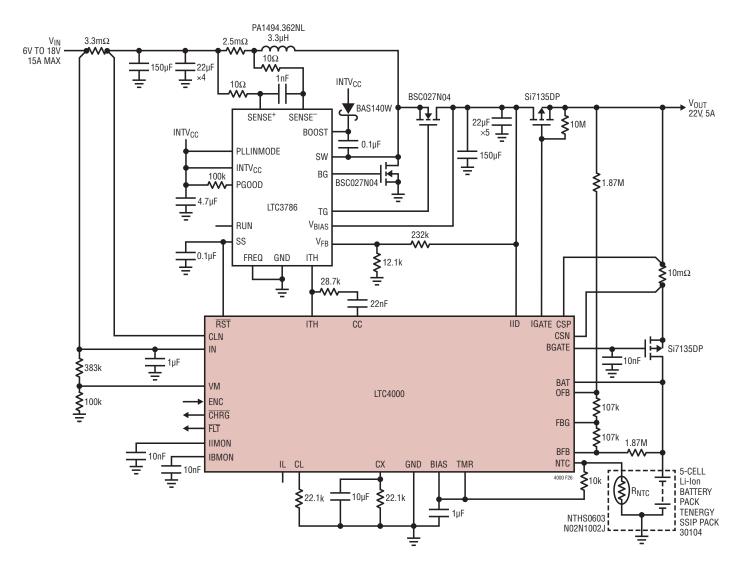

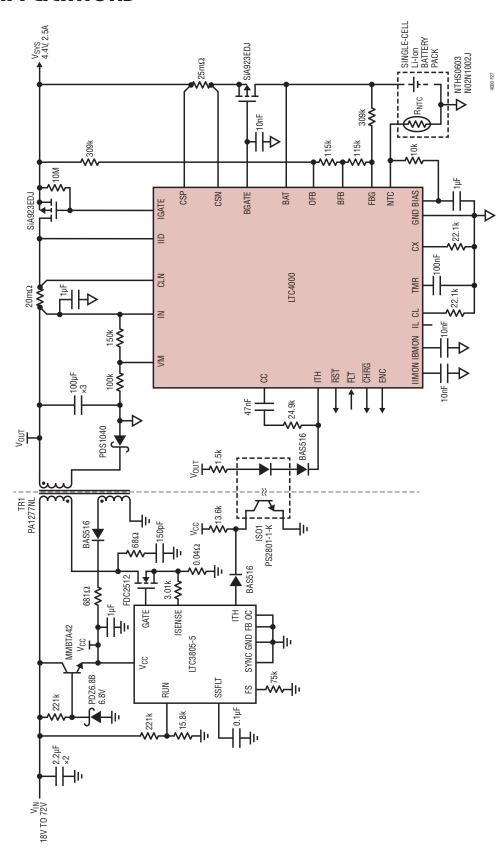

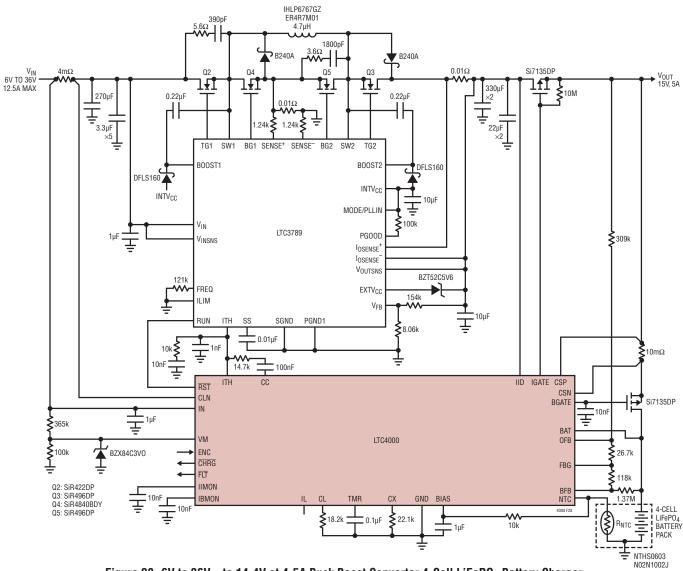

# TYPICAL APPLICATION

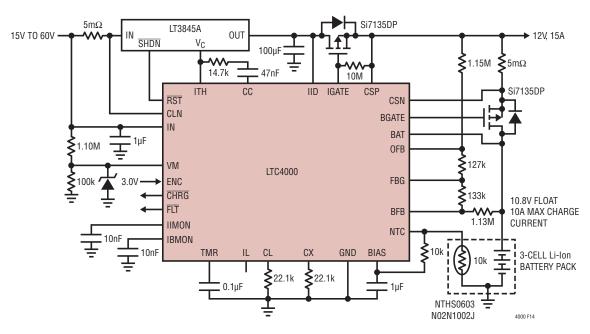

48V to 10.8V at 10A Buck Converter Charger for Three LiFePO4 Cells

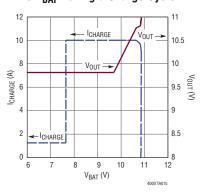

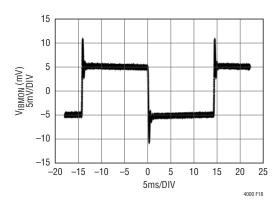

# Charge Current and V<sub>OUT</sub> Profile vs V<sub>BAT</sub> During a Charge Cycle

# **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| IN, CLN, IID, CSP, CSN, BAT                       | 0.3V to 62V                                               |

|---------------------------------------------------|-----------------------------------------------------------|

| IN-CLN, CSP-CSN                                   | –1V to 1V                                                 |

| OFB, BFB, FBG                                     | 0.3V to 62V                                               |

| FBG                                               | –1mA to 2mA                                               |

| IGATEMax (V <sub>IID</sub> , V <sub>CSP</sub> )   | - 10V to Max (V <sub>IID</sub> , V <sub>CSP</sub> )       |

| BGATEMax (V <sub>BAT</sub> , V <sub>CSN</sub> ) - | $\cdot$ 10V to Max (V <sub>BAT</sub> , V <sub>CSN</sub> ) |

| ENC, CX, NTC, VM                                  | 0.3V to $V_{BIAS}$                                        |

| IL, CL, TMR, IIMON, CC                            | 0.3V to V <sub>BIAS</sub>                                 |

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-------------------|---------------|---------------------------------|-------------------|

| LTC4000EUFD#PBF  | LTC4000EUFD#TRPBF | 4000          | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

| LTC4000IUFD#PBF  | LTC4000IUFD#TRPBF | 4000          | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

| LTC4000EGN#PBF   | LTC4000EGN#TRPBF  | LTC4000GN     | 28-Lead Plastic SSOP            | -40°C to 125°C    |

| LTC4000IGN#PBF   | LTC4000IGN#TRPBF  | LTC4000GN     | 28-Lead Plastic SSOP            | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

> LINEAR TECHNOLOGY

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25\,^{\circ}\text{C}$ .  $V_{IN} = V_{CLN} = 3V$  to 60V unless otherwise noted (Notes 2, 3).

| SYMBOL                    | PARAMETER                                                                              | CONDITIONS                                                                                         |   | MIN            | TYP            | MAX            | UNITS |

|---------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---|----------------|----------------|----------------|-------|

| $V_{IN}$                  | Input Supply Operating Range                                                           |                                                                                                    | • | 3              |                | 60             | V     |

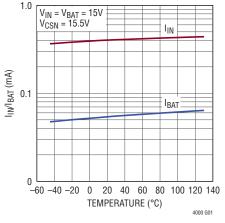

| I <sub>IN</sub>           | Input Quiescent Operating Current                                                      |                                                                                                    |   |                | 0.4            |                | mA    |

| I <sub>BAT</sub>          | Battery Pin Operating Current                                                          | $V_{IN} \ge 3V$ , $V_{CSN} = V_{CSP} \ge V_{BAT}$                                                  | • |                | 50             | 100            | μА    |

|                           | Battery Only Quiescent Current                                                         | $V_{IN} = 0V$ , $V_{CSN} = V_{CSP} \le V_{BAT}$                                                    | • |                | 10             | 20             | μА    |

| Shutdown                  |                                                                                        |                                                                                                    |   |                | ,              |                |       |

|                           | ENC Input Voltage Low                                                                  |                                                                                                    | • |                |                | 0.4            | V     |

|                           | ENC Input Voltage High                                                                 |                                                                                                    | • | 1.5            |                |                | V     |

|                           | ENC Pull-Up Current                                                                    | V <sub>ENC</sub> = 0V                                                                              |   | -4             | -2             | -0.5           | μА    |

|                           | ENC Open Circuit Voltage                                                               | V <sub>ENC</sub> = Open                                                                            | • | 1.5            | 2.5            |                | V     |

| Voltage Regulat           | ion                                                                                    | 1                                                                                                  |   |                | ,              |                |       |

| $V_{BFB\_REG}$            | Battery Feedback Voltage                                                               |                                                                                                    | • | 1.133<br>1.120 | 1.136<br>1.136 | 1.139<br>1.147 | V     |

|                           | BFB Input Current                                                                      | V <sub>BFB</sub> = 1.2V                                                                            |   |                | ± 0.1          |                | μА    |

| V <sub>OFB REG</sub>      | Output Feedback Voltage                                                                |                                                                                                    | • | 1.176          | 1.193          | 1.204          | V     |

|                           | OFB Input Current                                                                      | V <sub>OFB</sub> = 1.2V                                                                            |   |                | ± 0.1          |                | μА    |

| R <sub>FBG</sub>          | Ground Return Feedback Resistance                                                      | ***                                                                                                | • |                | 100            | 400            | Ω     |

| V <sub>RECHRG(RISE)</sub> | Rising Recharge Battery Threshold Voltage                                              | % of V <sub>BFB REG</sub>                                                                          | • | 96.9           | 97.6           | 98.3           | %     |

| V <sub>RECHRG(HYS)</sub>  | Recharge Battery Threshold Voltage Hysteresis                                          | % of V <sub>BFB_REG</sub>                                                                          |   |                | 0.5            |                | %     |

| V <sub>OUT(INST_ON)</sub> | Instant-On Battery Voltage Threshold                                                   | % of V <sub>BFB REG</sub>                                                                          | • | 82             | 86             | 90             | %     |

| $\overline{V_{LOBAT}}$    | Falling Low Battery Threshold Voltage                                                  | % of V <sub>BFB_REG</sub>                                                                          | • | 65             | 68             | 71             | %     |

| V <sub>LOBAT(HYS)</sub>   | Low Battery Threshold Voltage Hysteresis                                               | % of V <sub>BFB_REG</sub>                                                                          |   |                | 3              |                | %     |

| <b>Current Regulat</b>    | ion                                                                                    |                                                                                                    |   |                |                |                |       |

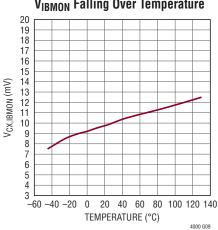

|                           | Ratio of Monitored-Current Voltage to Sense Voltage                                    | $V_{IN,CLN} \le 50$ mV, $V_{IIMON}/V_{IN,CLN}$<br>$V_{CSP,CSN} \le 50$ mV, $V_{IBMON}/V_{CSP,CSN}$ | • | 18.5           | 20             | 21             | V/V   |

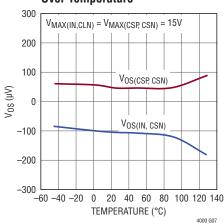

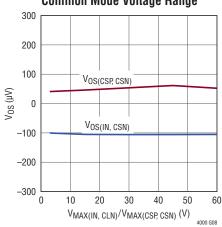

| $\overline{V_{0S}}$       | Sense Voltage Offset                                                                   | $V_{CSP,CSN} \le 50$ mV, $V_{CSP} = 60$ V or $V_{IN,CLN} \le 50$ mV, $V_{IN} = 60$ V (Note 4)      |   | -300           |                | 300            | μV    |

|                           | CLN, CSP, CSN Common Mode Range                                                        | (Note 4)                                                                                           | • | 3              |                | 60             | V     |

|                           | CLN Pin Current                                                                        |                                                                                                    |   |                | ±1             |                | μА    |

|                           | CSP Pin Current                                                                        | V <sub>IGATE</sub> = Open, V <sub>IID</sub> = 0V                                                   |   |                | 90             |                | μА    |

|                           | CSN Pin Current                                                                        | V <sub>BGATE</sub> = Open, V <sub>BAT</sub> = 0V                                                   |   |                | 45             |                | μA    |

| I <sub>IL</sub>           | Pull-Up Current for the Input Current Limit<br>Programming Pin                         |                                                                                                    | • | <b>-</b> 55    | -50            | -45            | μА    |

| I <sub>CL</sub>           | Pull-Up Current for the Charge Current Limit<br>Programming Pin                        |                                                                                                    | • | <b>-</b> 55    | -50            | -45            | μА    |

| I <sub>CL_TRKL</sub>      | Pull-Up Current for the Charge Current Limit<br>Programming Pin in Trickle Charge Mode | V <sub>BFB</sub> < V <sub>LOBAT</sub>                                                              | • | -5.5           | -5.0           | -4.5           | μА    |

|                           | Input Current Monitor Resistance to GND                                                |                                                                                                    |   | 40             | 90             | 140            | kΩ    |

|                           | Charge Current Monitor Resistance to GND                                               |                                                                                                    |   | 40             | 90             | 140            | kΩ    |

|                           | A4, A5 Error Amp Offset for the Current Loops<br>(See Figure 1)                        | V <sub>CL</sub> = 0.8V, V <sub>IL</sub> = 0.8V                                                     | • | -10            | 0              | 10             | mV    |

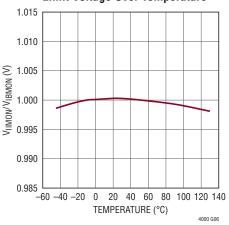

|                           | Maximum Programmable Current Limit<br>Voltage Range                                    |                                                                                                    | • | 0.985          | 1.0            | 1.015          | V     |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ . $V_{IN} = V_{CLN} = 3V$ to 60V unless otherwise noted (Notes 2, 3).

| SYMBOL                             | PARAMETER                                                    | CONDITIONS                                                                                                                                                                          |   | MIN   | TYP   | MAX   | UNITS |

|------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|-------|-------|-------|

| Charge Termination                 | on                                                           |                                                                                                                                                                                     |   |       |       |       |       |

|                                    | CX Pin Pull-Up Current                                       | V <sub>CX</sub> = 0.1V                                                                                                                                                              | • | -5.5  | -5.0  | -4.5  | μΑ    |

| V <sub>CX,IBMON(OS)</sub>          | CX Comparator Offset Voltage, IBMON Falling                  | V <sub>CX</sub> = 0.1V                                                                                                                                                              | • | 0.5   | 10    | 25    | m۷    |

| V <sub>CX,IBMON(HYS)</sub>         | CX Comparator Hysteresis Voltage                             |                                                                                                                                                                                     |   |       | 5     |       | m۷    |

| ,                                  | TMR Pull-Up Current                                          | V <sub>TMR</sub> = 0V                                                                                                                                                               |   |       | -5.0  |       | μА    |

|                                    | TMR Pull-Down Current                                        | V <sub>TMR</sub> = 2V                                                                                                                                                               |   |       | 5.0   |       | μА    |

|                                    | TMR Pin Frequency                                            | C <sub>TMR</sub> = 0.01μF                                                                                                                                                           |   | 400   | 500   | 600   | Hz    |

|                                    | TMR Threshold for CX Termination                             |                                                                                                                                                                                     | • |       | 2.1   | 2.5   | V     |

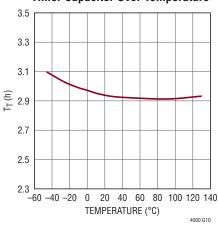

| t <sub>T</sub>                     | Charge Termination Time                                      | C <sub>TMR</sub> = 0.1µF                                                                                                                                                            | • | 2.3   | 2.9   | 3.5   | h     |

| t <sub>T</sub> /t <sub>BB</sub>    | Ratio of Charge Terminate Time to Bad Battery Indicator Time | C <sub>TMR</sub> = 0.1μF                                                                                                                                                            | • | 3.95  | 4     | 4.05  | h/h   |

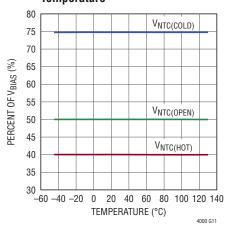

| V <sub>NTC(COLD)</sub>             | NTC Cold Threshold                                           | V <sub>NTC</sub> Rising, % of V <sub>BIAS</sub>                                                                                                                                     | • | 73    | 75    | 77    | %     |

| V <sub>NTC(HOT)</sub>              | NTC Hot Threshold                                            | V <sub>NTC</sub> Falling, % of V <sub>BIAS</sub>                                                                                                                                    | • | 33    | 35    | 37    | %     |

| V <sub>NTC(HYS)</sub>              | NTC Thresholds Hysteresis                                    | % of V <sub>BIAS</sub>                                                                                                                                                              |   |       | 5     |       | %     |

| V <sub>NTC(OPEN)</sub>             | NTC Open Circuit Voltage                                     | % of V <sub>BIAS</sub>                                                                                                                                                              | • | 45    | 50    | 55    | %     |

| R <sub>NTC(OPEN)</sub>             | NTC Open Circuit Input Resistance                            |                                                                                                                                                                                     |   |       | 300   |       | kΩ    |

| Voltage Monitorin                  | g and Open Drain Status Pins                                 |                                                                                                                                                                                     |   |       |       |       |       |

| $\overline{V_{VM(TH)}}$            | VM Input Falling Threshold                                   |                                                                                                                                                                                     | • | 1.176 | 1.193 | 1.204 | V     |

| V <sub>VM(HYS)</sub>               | VM Input Hysteresis                                          |                                                                                                                                                                                     |   |       | 40    |       | mV    |

|                                    | VM Input Current                                             | V <sub>VM</sub> = 1.2V                                                                                                                                                              |   |       | ±0.1  |       | μA    |

| I <sub>RST,CHRG,FLT</sub> (LKG)    | Open Drain Status Pins Leakage Current                       | V <sub>PIN</sub> = 60V                                                                                                                                                              |   | ±1    |       |       | μА    |

| V <sub>RST</sub> , CHRG, FLT (VOL) | Open Drain Status Pins Voltage Output Low                    | I <sub>PIN</sub> = 1mA                                                                                                                                                              | • |       |       | 0.4   | V     |

| Input PowerPath (                  | Control                                                      |                                                                                                                                                                                     |   |       |       |       | -     |

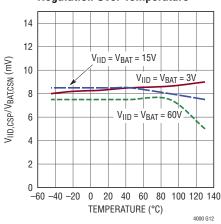

|                                    | Input PowerPath Forward Regulation Voltage                   | $V_{IID,CSP}$ , $3V \le V_{CSP} \le 60V$                                                                                                                                            | • | 0.1   | 8     | 20    | mV    |

|                                    | Input PowerPath Fast Reverse Turn-Off<br>Threshold Voltage   | $ \begin{aligned} &V_{IID,CSP},3V \leq V_{CSP} \leq 60V, \\ &V_{IGATE} = V_{CSP} - 2.5V, \\ &\Delta I_{IGATE}/\DeltaV_{IID,CSP} \geq 100\mu\text{A/mV} \end{aligned} $              | • | -90   | -50   | -20   | mV    |

|                                    | Input PowerPath Fast Forward Turn-On<br>Threshold Voltage    | $ \begin{aligned} &V_{IID,CSP},  3V \leq V_{CSP} \leq 60V, \\ &V_{IGATE} = V_{IID} - 1.5V, \\ &\Delta I_{IGATE}/\Delta   V_{IID,CSP} \geq 100 \mu \text{A/mV} \end{aligned} $       | • | 40    | 80    | 130   | mV    |

|                                    | Input Gate Turn-Off Current                                  | $V_{IID} = V_{CSP}, V_{IGATE} = V_{CSP} - 1.5V$                                                                                                                                     |   |       | -0.3  |       | μА    |

|                                    | Input Gate Turn-On Current                                   | $V_{CSP} = V_{IID} - 20mV,$<br>$V_{IGATE} = V_{IID} - 1.5V$                                                                                                                         |   |       | 0.3   |       | μА    |

| IGATE(FASTOFF)                     | Input Gate Fast Turn-Off Current                             | $\begin{aligned} V_{CSP} &= V_{IID} + 0.1V, \\ V_{IGATE} &= V_{CSP} - 3V \end{aligned}$                                                                                             |   |       | -0.5  |       | mA    |

| I <sub>IGATE</sub> (FASTON)        | Input Gate Fast Turn-On Current                              | $V_{CSP} = V_{IID} - 0.2V,$<br>$V_{IGATE} = V_{IID} - 1.5V$                                                                                                                         |   |       | 0.7   |       | mA    |

| V <sub>IGATE(ON)</sub>             | Input Gate Clamp Voltage                                     | $ \begin{aligned} I_{IGATE} &= 2\mu A,  V_{IID} = 12 V \text{ to } 60 V, \\ V_{CSP} &= V_{IID} - 0.5 V,  Measure \\ V_{IID} &- V_{IGATE} \end{aligned} $                            | • |       | 13    | 15    | V     |

|                                    | Input Gate Off Voltage                                       | $ \begin{aligned} &I_{IGATE} = -2\mu\text{A}, \ V_{IID} = 3\text{V to } 59.9\text{V}, \\ &V_{CSP} = V_{IID} + 0.5\text{V}, \ \text{Measure} \\ &V_{CSP} - V_{IGATE} \end{aligned} $ | • |       | 0.45  | 0.7   | V     |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{IN} = V_{CLN} = 3V$  to 60V unless otherwise noted (Notes 2, 3).

| SYMBOL                       | PARAMETER                                                    | PARAMETER CONDITIONS                                                                                                                                                                                 |   | MIN | TYP  | MAX | UNITS |

|------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|------|-----|-------|

| Battery PowerPa              | th Control                                                   |                                                                                                                                                                                                      |   |     |      |     |       |

|                              | Battery Discharge PowerPath Forward<br>Regulation Voltage    | $V_{BAT,CSN}$ , $2.8V \le V_{BAT} \le 60V$                                                                                                                                                           | • | 0.1 | 8    | 20  | mV    |

|                              | Battery PowerPath Fast Reverse Turn-Off<br>Threshold Voltage | $\begin{array}{l} V_{BAT,CSN}, \ 2.8V \leq V_{BAT} \leq 60V, \ Not \\ Charging, \ V_{BGATE} = V_{CSN} - 2.5V, \\ \Delta I_{BGATE}/\Delta V_{BAT,CSN} \geq 100 \mu A/mV \end{array}$                  | • | -90 | -50  | -20 | mV    |

|                              | Battery PowerPath Fast Forward Turn-On<br>Threshold Voltage  | $\begin{split} &V_{BAT,CSN}, \ 2.8V \leq V_{CSN} \leq 60V, \\ &V_{BGATE} = V_{BAT} - 1.5V, \\ &\Delta I_{BGATE}/\Delta \ V_{BAT,CSN} \geq 100 \mu A/mV \end{split}$                                  | • | 40  | 80   | 130 | mV    |

|                              | Battery Gate Turn-Off Current                                | $\begin{split} &V_{BGATE} = V_{CSN} - 1.5V, \ V_{CSN} \geq V_{BAT}, \\ &V_{OFB} < V_{OUT(INST\_ON)} \ and \ Charging \\ ∈ \ Progress, \ or \ V_{CSN} = V_{BAT} \ and \ Not \\ &Charging \end{split}$ |   |     | -0.3 |     | μА    |

|                              | Battery Gate Turn-On Current                                 | $\begin{array}{l} V_{BGATE} = V_{BAT} - 1.5V, \ V_{CSN} \geq V_{BAT}, \\ V_{OFB} > V_{OUT(INST\_ON)} \ and \ Charging \ in \\ Progress, \ or \ V_{CSN} = V_{BAT} - 20mV \end{array}$                 |   |     | 0.3  |     | μА    |

| I <sub>BGATE</sub> (FASTOFF) | Battery Gate Fast Turn-Off Current                           | $V_{CSN} = V_{BAT} + 0.1V$ and Not Charging, $V_{BGATE} = V_{CSN} - 3V$                                                                                                                              |   |     | -0.5 |     | mA    |

| I <sub>BGATE</sub> (FASTON)  | Battery Gate Fast Turn-On Current                            | $V_{CSN} = V_{BAT} - 0.2V,$<br>$V_{BGATE} = V_{BAT} - 1.5V$                                                                                                                                          |   |     | 0.7  |     | mA    |

| V <sub>BGATE(ON)</sub>       | Battery Gate Clamp Voltage                                   | $I_{BGATE}$ = 2 $\mu$ A, $V_{BAT}$ = 12V to 60V, $V_{CSN}$ = $V_{BAT}$ – 0.5V, Measure $V_{BAT}$ – $V_{BGATE}$                                                                                       | • |     | 13   | 15  | V     |

|                              | Battery Gate Off Voltage                                     | $\begin{split} I_{BGATE} &= -2\mu\text{A},  V_{BAT} = 2.8 \text{V to 60V}, \\ V_{CSN} &= V_{BAT} + 0.5 \text{V and not Charging}, \\ \text{Measure } V_{CSN} - V_{BGATE} \end{split}$                | • |     | 0.45 | 0.7 | V     |

| BIAS Regulator (             | Output and Control Pins                                      |                                                                                                                                                                                                      |   |     |      |     |       |

| V <sub>BIAS</sub>            | BIAS Output Voltage                                          | No Load                                                                                                                                                                                              | • | 2.4 | 2.9  | 3.5 | V     |

| $\Delta V_{BIAS}$            | BIAS Output Voltage Load Regulation                          | $I_{BIAS} = -0.5$ mA                                                                                                                                                                                 |   |     | -0.5 | -10 | %     |

|                              | BIAS Output Short-Circuit Current                            | V <sub>BIAS</sub> = 0V                                                                                                                                                                               |   |     | -12  |     | mA    |

|                              | Transconductance of Error Amp                                | CC = 1V                                                                                                                                                                                              |   |     | 0.5  |     | mA/V  |

|                              | Open Loop DC Voltage Gain of Error Amp                       | CC = Open                                                                                                                                                                                            |   |     | 80   |     | dB    |

| I <sub>ITH(PULL_UP)</sub>    | Pull-Up Current on the ITH Pin                               | V <sub>ITH</sub> = 0V, CC = 0V                                                                                                                                                                       |   | -6  | -5   | -4  | μA    |

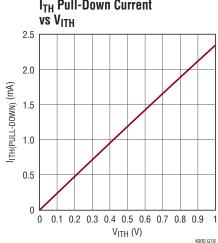

| ITH(PULL_DOWN)               | Pull-Down Current on the ITH Pin                             | V <sub>ITH</sub> = 0.4V, CC = Open                                                                                                                                                                   | • | 0.5 | 1    |     | mA    |

|                              | Open Loop DC Voltage Gain of ITH Driver                      | ITH = Open                                                                                                                                                                                           |   |     | 60   |     | dB    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC4000 is tested under conditions such that  $T_J \approx T_A$ . The LTC4000E is guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC4000I is guaranteed over the full -40°C to 125°C operating junction temperature range. Note that the maximum ambient temperature consistent with these specifications is

determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors. The junction temperature ( $T_J$ , in °C) is calculated from the ambient temperature ( $T_A$ , in °C) and power dissipation ( $P_D$ , in Watts) according to the following formula:

$T_J = T_A + (P_D \bullet \theta_{JA})$ , where  $\theta_{JA}$  (in °C/W) is the package thermal impedance.

**Note 3:** All currents into pins are positive; all voltages are referenced to GND unless otherwise noted.

Note 4: These parameters are guaranteed by design and are not 100% tested.

# TYPICAL PERFORMANCE CHARACTERISTICS

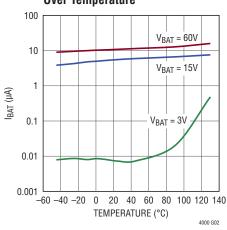

#### Input Quiescent Current and Battery Quiescent Current Over Temperature

#### Battery Only Quiescent Current Over Temperature

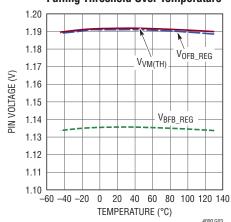

Battery Float Voltage Feedback, Output Voltage Regulation Feedback and VM Falling Threshold Over Temperature

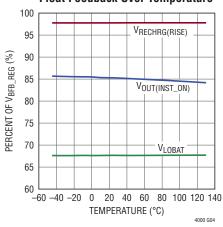

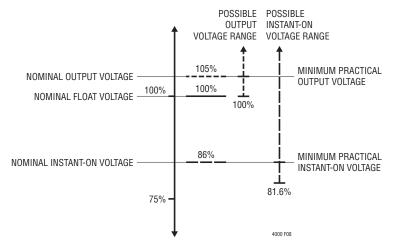

Battery Thresholds: Rising Recharge, Instant-On Regulation and Falling Low Battery As a Percentage of Battery Float Feedback Over Temperature

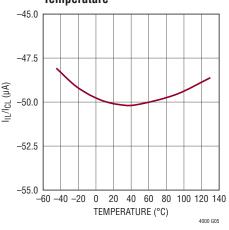

IL and CL Pull-Up Current Over Temperature

Maximum Programmable Current Limit Voltage Over Temperature

Current Sense Offset Voltage Over Temperature

Current Sense Offset Voltage Over Common Mode Voltage Range

CX Comparator Offset Voltage with V<sub>IBMON</sub> Falling Over Temperature

# TYPICAL PERFORMANCE CHARACTERISTICS

#### Charge Termination Time with 0.1µF **Timer Capacitor Over Temperature**

#### NTC Thresholds Over **Temperature**

PowerPath Forward Voltage **Regulation Over Temperature**

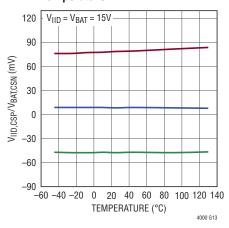

#### PowerPath Fast Off, Fast On and Forward Regulation Over **Temperature**

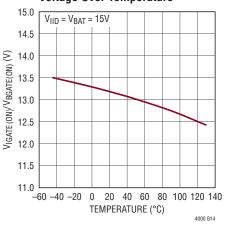

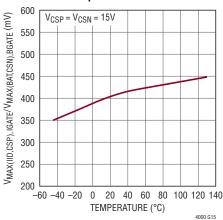

#### PowerPath Turn-On Gate Clamp **Voltage Over Temperature**

PowerPath Turn-Off Gate Voltage **Over Temperature**

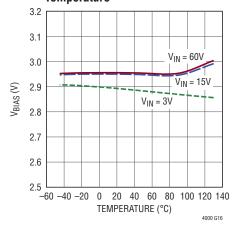

#### BIAS Voltage at 0.5mA Load Over **Temperature**

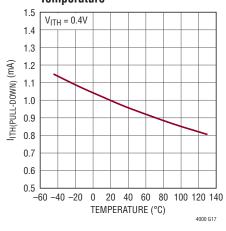

#### I<sub>TH</sub> Pull-Down Current Over Temperature

# I<sub>TH</sub> Pull-Down Current

# PIN FUNCTIONS (QFN/SSOP)

**VM (Pin 1/Pin 25):** Voltage Monitor Input. High impedance input to an accurate comparator with a 1.193V threshold (typical). This pin controls the state of the  $\overline{RST}$  output pin. Connect a resistor divider ( $R_{VM1}$ ,  $R_{VM2}$ ) between the monitored voltage and GND, with the center tap point connected to this pin. The falling threshold of the monitored voltage is calculated as follows:

$$V_{VM\_RST} = \frac{R_{VM1} + R_{VM2}}{R_{VM2}} \bullet 1.193V$$

where  $R_{VM2}$  is the bottom resistor between the VM pin and GND. Tie to the BIAS pin if voltage monitoring function is not used.

RST (Pin 2/Pin 26): High Voltage Open Drain Reset Output. When the voltage at the VM pin is below 1.193V, this status pin is pulled low. When driven low, this pin can disable a DC/DC converter when connected to the converter's enable pin. This pin can also drive an LED to provide a visual status indicator of a monitored voltage. Short this pin to GND when not used.

**IIMON (Pin 3/Pin 27):** Input Current Monitor. The voltage on this pin is 20 times (typical) the sense voltage ( $V_{IN,CLN}$ ) across the input current sense resistor( $R_{IS}$ ), therefore providing a voltage proportional to the input current. Connect an appropriate capacitor to this pin to obtain a voltage representation of the time-average input current. Short this pin to GND to disable input current limit feature.

**IL** (**Pin 4/Pin 28**): Input Current Limit Programming. Connect the input current programming resistor ( $R_{IL}$ ) to this pin. This pin sources  $50\mu A$  of current. The regulation loop compares the voltage on this pin with the input current monitor voltage ( $V_{IIMON}$ ), and drives the ITH pin accordingly to ensure that the programmed input current limit is not exceeded. The input current limit is determined using the following formula:

$$I_{ILIM} = 2.5 \mu A \cdot \left(\frac{R_{IL}}{R_{IS}}\right)$$

where  $R_{IS}$  is the sense resistor connected to the IN and the CLN pins. Leave the pin open for the maximum input current limit of  $50 \text{mV/R}_{IS}$ .

**ENC (Pin 5/Pin 1):** Enable Charging Pin. High impedance digital input pin. Pull this pin above 1.5V to enable charging and below 0.5V to disable charging. Leaving this pin open causes the internal  $2\mu A$  pull-up current to pull the pin to 2.5V (typical).

**IBMON** (Pin 6/Pin 2): Battery Charge Current Monitor. The voltage on this pin is 20 times (typical) the sense voltage ( $V_{CSP,CSN}$ ) across the battery current sense resistor ( $R_{CS}$ ), therefore providing a voltage proportional to the battery charge current. Connect an appropriate capacitor to this pin to obtain a voltage representation of the time-average battery charge current. Short this pin to GND to disable charge current limit feature.

**CX** (**Pin 7/Pin 3**): Charge Current Termination Programming. Connect the charge current termination programming resistor ( $R_{CX}$ ) to this pin. This pin is a high impedance input to a comparator and sources  $5\mu A$  of current. When the voltage on this pin is greater than the charge current monitor voltage ( $V_{IBMON}$ ), the  $\overline{CHRG}$  pin turns high impedance indicating that the CX threshold is reached. When this occurs, the charge current is immediately terminated if the TMR pin is shorted to the BIAS pin, otherwise charging continues until the charge termination timer expires. The charge current termination value is determined using the following formula:

$$I_{C/X} = \frac{\left(0.25\mu\text{A} \cdot R_{CX}\right) - 0.5\text{mV}}{R_{CS}}$$

Where  $R_{CS}$  is the sense resistor connected to the CSP and the CSN pins. Note that if  $R_{CX} = R_{CL} \le 19.1 k\Omega$ , where  $R_{CL}$  is the charge current programming resistor, then the charge current termination value is one tenth the full charge current, more familiarly known as C/10. Short this pin to GND to disable CX termination.

**CL (Pin 8/Pin 4):** Charge Current Limit Programming. Connect the charge current programming resistor ( $R_{CL}$ ) to this pin. This pin sources 50µA of current. The regulation loop compares the voltage on this pin with the charge current monitor voltage ( $V_{IBMON}$ ), and drives the ITH pin accordingly to ensure that the programmed charge current limit

LINEAR TECHNOLOGY

# PIN FUNCTIONS (QFN/SSOP)

is not exceeded. The charge current limit is determined using the following formula:

$$I_{CLIM} = 2.5 \mu A \cdot \left(\frac{R_{CL}}{R_{CS}}\right)$$

Where  $R_{CS}$  is the sense resistor connected to the CSP and the CSN pins. Leave the pin open for the maximum charge current limit of  $50 \text{mV/R}_{CS}$ .

**TMR (Pin 9/Pin 5):** Charge Timer. Attach 1nF of external capacitance ( $C_{TMR}$ ) to GND for each 104 seconds of charge termination time and 26 seconds of bad battery indicator time. Short to GND to prevent bad battery indicator time and charge termination time from expiring — allowing a continuous trickle charge and top off float voltage regulation charge. Short to BIAS to disable bad battery detect and enable C/X charging termination.

**GND** (Pins 10, 28, 29/Pins 6, 24): Device Ground Pins. Connect the ground pins to a suitable PCB copper ground plane for proper electrical operation. The QFN package exposed pad must be soldered to PCB ground for rated thermal performance.

FLT, CHRG (Pin 11, Pin 12/Pin 7, Pin 8): Charge Status Indicator Pins. These pins are high voltage open drain pull down pins. The FLT pin pulls down when there is an under or over temperature condition during charging or when the voltage on the BFB pin stays below the low battery threshold during charging for a period longer than the bad battery indicator time. The CHRG pin pulls down during a charging cycle. Please refer to the application information section for details on specific modes indicated by the combination of the states of these two pins. Pull up each of these pins with an LED in series with a resistor to a voltage source to provide a visual status indicator. Short these pins to GND when not used.

**BIAS (Pin 13/Pin 9):** 2.9V Regulator Output. Connect a capacitor of at least 470nF to bypass this 2.9V regulated voltage output. Use this pin to bias the resistor divider to set up the voltage at the NTC pin.

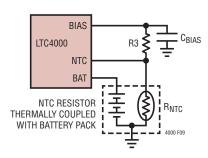

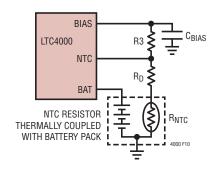

NTC (Pin 14/Pin 10): Thermistor Input. Connect a thermistor from NTC to GND, and a corresponding resistor from BIAS to NTC. The voltage level on this pin determines

if the battery temperature is safe for charging. The charge current and charge timer are suspended if the thermistor indicates a temperature that is unsafe for charging. Once the temperature returns to the safe region, charging resumes. Leave the pin open or connected to a capacitor to disable the temperature qualified charging function.

**FBG (Pin 15/Pin 11):** Feedback Ground Pin. This is the ground return pin for the resistor dividers connected to the BFB and OFB pins. As soon as the voltage at IN is valid (>3V typical), this pin has a  $100\Omega$  resistance to GND. When the voltage at IN is not valid, this pin is disconnected from GND to ensure that the resistor dividers connected to the BFB and OFB pins do not continue to drain the battery when the battery is the only available power source.

**BFB** (Pin 16/Pin 12): Battery Feedback Voltage Pin. This pin is a high impedance input pin used to sense the battery voltage level. In regulation, the battery float voltage loop sets the voltage on this pin to 1.136V (typical). Connect this pin to the center node of a resistor divider between the BAT pin and the FBG pin to set the battery float voltage. The battery float voltage can then be obtained as follows:

$$V_{FLOAT} = \frac{R_{BFB2} + R_{BFB1}}{R_{BFB2}} \bullet 1.136V$$

**BAT (Pin 17/Pin 13):** Battery Pack Connection. Connect the battery to this pin. This pin is the anode of the battery ideal diode driver (the cathode is the CSN pin).

**BGATE (Pin 18/Pin 14):** External Battery PMOS Gate Drive Output. When not charging, the BGATE pin drives the external PMOS to behave as an ideal diode from the BAT pin (anode) to the CSN pin (cathode). This allows efficient delivery of any required additional power from the battery to the downstream system connected to the CSN pin.

When charging a heavily discharged battery, the BGATE pin is regulated to set the output feedback voltage (OFB pin) to 86% of the battery float voltage (0.974V typical). This allows the instant-on feature, providing an immediate valid voltage level at the output when the LTC4000 is charging a heavily discharged battery. Once the voltage on the OFB pin is above the 0.974V typical value, then the BGATE pin is driven low to ensure an efficient charging path from the CSN pin to the BAT pin.

# PIN FUNCTIONS (QFN/SSOP)

**CSN (Pin 19/Pin 15):** Charge Current Sense Negative Input and Battery Ideal Diode Cathode. Connect a sense resistor between this pin and the CSP pin. The LTC4000 senses the voltage across this sense resistor and regulates it to a voltage equal to 1/20th (typical) of the voltage set at the CL pin. The maximum regulated sense voltage is 50mV. The CSN pin is also the cathode input of the battery ideal diode driver (the anode input is the BAT pin). Tie this pin to the CSP pin if no charge current limit is desired. Refer to the Applications Information section for complete details.

**CSP** (**Pin 20/Pin 16**): Charge Current Sense Positive Input and Input Ideal Diode Cathode. Connect a sense resistor between this pin and the CSN pin for charge current sensing and regulation. This input should be tied to CSN to disable the charge current regulation function. This pin is also the cathode of the input ideal diode driver (the anode is the IID pin).

**OFB** (**Pin 21/Pin 17**): Output Feedback Voltage Pin. This pin is a high impedance input pin used to sense the output voltage level. In regulation, the output voltage loop sets the voltage on this feedback pin to 1.193V. Connect this pin to the center node of a resistor divider between the CSP pin and the FBG pin to set the output voltage when battery charging is terminated and all the output load current is provided from the input. The output voltage can then be obtained as follows:

$$V_{OUT} = \frac{R_{OFB2} + R_{OFB1}}{R_{OFB2}} \bullet 1.193V$$

When charging a heavily discharged battery (such that  $V_{OFB} < V_{OUT(INST\_ON)}$ ), the battery PowerPath PMOS connected to BGATE is regulated to set the voltage on this feedback pin to 0.974V (approximately 86% of the battery float voltage). The instant-on output voltage is then as follows:

$$V_{OUT(INST\_ON)} = \frac{R_{OFB2} + R_{OFB1}}{R_{OFB2}} \bullet 0.974V$$

**IGATE (Pin 22/Pin 18):** Input PMOS Gate Drive Output. The IGATE pin drives the external PMOS to behave as an ideal diode from the IID pin (anode) to the CSP pin (cathode)

when the voltage at the IN pin is within its operating range (3V to 60V). To ensure that the input PMOS is turned off when the IN pin voltage is not within its operating range, connect a 10M resistor from this pin to the CSP pin.

**IID (Pin 23/Pin 19):** Input Ideal Diode Anode. This pin is the anode of the input ideal diode driver (the cathode is the CSP pin).

ITH (Pin 24/Pin 20): High Impedance Control Voltage Pin. When any of the regulation loops (input current, charge current, battery float voltage or the output voltage) indicate that its limit is reached, the ITH pin will sink current (up to 1mA) to regulate that particular loop at the limit. In many applications, this ITH pin is connected to the control/compensation node of a DC/DC converter. Without any external pull-up, the operating voltage range on this pin is GND to 2.5V. With an external pull-up, the voltage on this pin can be pulled up to 6V. Note that the impedance connected to this pin affects the overall loop gain. For details, refer to the Applications Information section.

**CC (Pin 25/Pin 21):** Converter Compensation Pin. Connect an R-C network from this pin to the ITH pin to provide a suitable loop compensation for the converter used. Refer to the Applications Information section for discussion and procedure on choosing an appropriate R-C network for a particular DC/DC converter.

**CLN (Pin 26/Pin 22):** Input Current Sense Negative Input. Connect a sense resistor between this pin and the IN pin. The LTC4000 senses the voltage across this sense resistor and regulates it to a voltage equal to 1/20th (typical) of the voltage set at the IL pin. Tie this pin to the IN pin if no input current limit is desired. Refer to the Applications Information section for complete details.

IN (Pin 27/Pin 23): Input Supply Voltage: 3V to 60V. Supplies power to the internal circuitry and the BIAS pin. Connect the power source to the downstream system and the battery charger to this pin. This pin is also the positive sense pin for the input current limit. Connect a sense resistor between this pin and the CLN pin. Tie this pin to CLN if no input current limit is desired. A local  $0.1\mu F$  bypass capacitor to ground is recommended on this pin.

LINEAR TECHNOLOGY

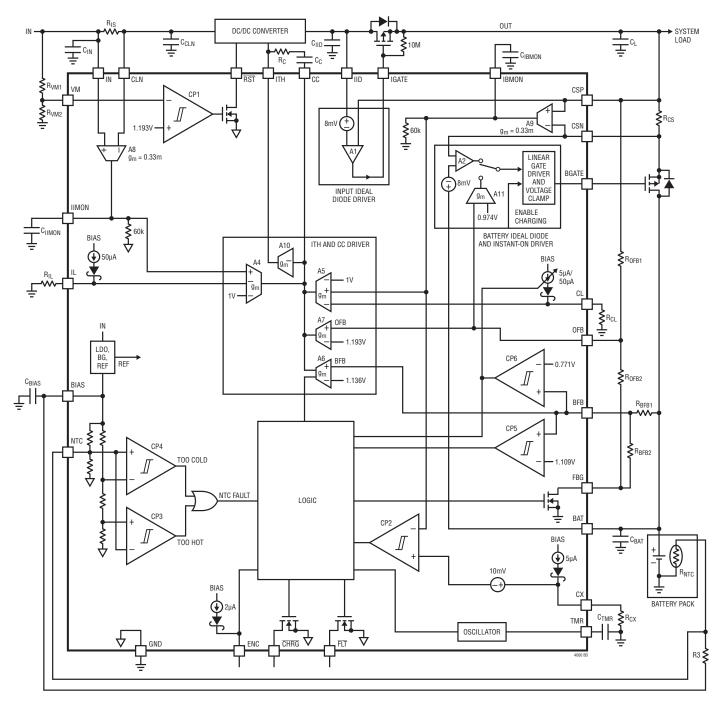

# **BLOCK DIAGRAM**

Figure 1. LTC4000 Functional Block Diagram

#### Overview

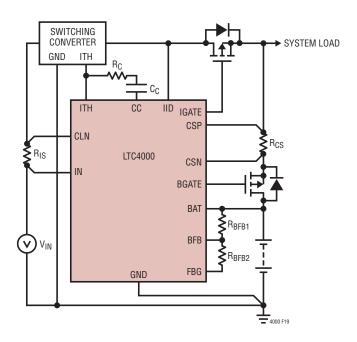

The LTC4000 is designed to simplify the conversion of any externally compensated DC/DC converter into a high performance battery charger with PowerPath control. It only requires the DC/DC converter to have a control or external-compensation pin (usually named VC or ITH) whose voltage level varies in a positive monotonic way with its output. The output variable can be either output voltage or output current. For the following discussion, refer to the Block Diagram in Figure 1.

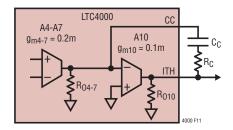

The LTC4000 includes four different regulation loops: input current, charge current, battery float voltage and output voltage (A4-A7). Whichever loop requires the lowest voltage on the ITH pin for its regulation controls the external DC/DC converter.

The input current regulation loop ensures that the programmed input current limit (using a resistor at IL) is not exceeded at steady state. The charge current regulation loop ensures that the programmed battery charge current limit (using a resistor at CL) is not exceeded. The float voltage regulation loop ensures that the programmed battery stack voltage (using a resistor divider from BAT to FBG via BFB) is not exceeded. The output voltage regulation loop ensures that the programmed system output voltage (using a resistor divider from CSP to FBG via OFB) is not exceeded. The LTC4000 also provides monitoring pins for the input current and charge current at the IIMON and IBMON pins respectively.

The LTC4000 features an ideal diode controller at the input from the IID pin to the CSP pin and a PowerPath controller at the output from the BAT pin to the CSN pin. The output PowerPath controller behaves as an ideal diode controller when not charging. When charging, the output PowerPath controller has two modes of operation. If  $V_{OFB}$  is greater than  $V_{OUT(INST\_ON)}$ , BGATE is driven low. When  $V_{OFB}$  is less than  $V_{OUT(INST\_ON)}$ , a linear regulator implements the instant-on feature. This feature provides regulation of the BGATE pin so that a valid voltage level is immediately available at the output when the LTC4000 is charging an over-discharged, dead or short faulted battery.

The state of the ENC pin determines whether charging is enabled. When ENC is grounded, charging is disabled and

the battery float voltage loop is disabled. Charging is enabled when the ENC pin is left floating or pulled high ( $\geq$ 1.5V)

The LTC4000 offers several user configurable battery charge termination schemes. The TMR pin can be configured for either C/X termination, charge timer termination or no termination. After a particular charge cycle terminates, the LTC4000 features an automatic recharge cycle if the battery voltage drops below 97.6% of the programmed float voltage.

Trickle charge mode drops the charge current to one tenth of the normal charge current (programmed using a resistor from the CL pin to GND) when charging into an over discharged or dead battery. When trickle charging, a capacitor on the TMR pin can be used to program a time out period. When this bad battery timer expires and the battery voltage fails to charge above the low battery threshold ( $V_{LOBAT}$ ), the LTC4000 will terminate charging and indicate a bad battery condition through the status pins (FLT and CHRG).

The LTC4000 also includes an NTC pin, which provides temperature qualified charging when connected to an NTC thermistor thermally coupled to the battery pack. To enable this feature, connect the thermistor between the NTC and the GND pins, and a corresponding resistor from the BIAS pin to the NTC pin. The LTC4000 also provides a charging status indicator through the FLT and the CHRG pins.

Aside from biasing the thermistor-resistor network, the BIAS pin can also be used for a convenient pull up voltage. This pin is the output of a low dropout voltage regulator that is capable of providing up to 0.5mA of current. The regulated voltage on the BIAS pin is available as soon as the IN pin is within its operating range ( $\geq 3V$ ).

#### **Input Ideal Diode**

The input ideal diode feature provides low loss conduction and reverse blocking from the IID pin to the CSP pin. This reverse blocking prevents reverse current from the output (CSP pin) to the input (IID pin) which causes unnecessary drain on the battery and in some cases may result in unexpected DC/DC converter behavior.

The ideal diode behavior is achieved by controlling an external PMOS connected to the IID pin (drain) and the

CSP pin (source). The controller (A1) regulates the external PMOS by driving the gate of the PMOS device such that the voltage drop across IID and CSP is 8mV (typical). When the external PMOS ability to deliver a particular current with an 8mV drop across its source and drain is exceeded, the voltage at the gate clamps at  $V_{IGATE(ON)}$  and the PMOS behaves like a fixed value resistor ( $R_{DS(ON)}$ ).

Note that this input ideal diode function is only enabled when the voltage at the IN pin is within its operating range (3V to 60V). To ensure that the external PMOS is turned off when the voltage at the IN pin is not within its operating range, a 10M pull-up resistor between the IGATE and the CSP pin is recommended.

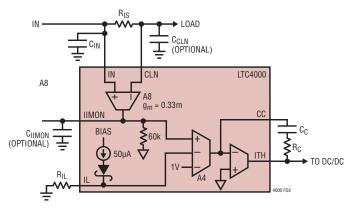

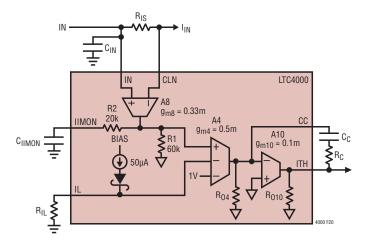

#### **Input Current Regulation and Monitoring**

One of the loops driving the ITH and CC pins is the input current regulation loop (Figure 2). This loop prevents the input current sensed through the input current sense resistor ( $R_{IS}$ ) from exceeding the programmed input current limit.

Figure 2. Input Current Regulation Loop

#### **Battery Charger Overview**

In addition to the input current regulation loop, the LTC4000 regulates charge current, battery voltage and output voltage.

When a battery charge cycle begins, the battery charger first determines if the battery is over-discharged. If the battery feedback voltage is below  $V_{LOBAT}$ , an automatic trickle charge feature uses the charge current regulation loop to set the battery charge current to 10% of the programmed full scale value. If the TMR pin is connected to a capacitor

or open, the bad battery detection timer is enabled. When this bad battery detection timer expires and the battery voltage is still below  $V_{LOBAT}$ , the battery charger automatically terminates and indicates, via the  $\overline{FLT}$  and  $\overline{CHRG}$  pins, that the battery was unresponsive to charge current.

Once the battery voltage is above  $V_{LOBAT}$ , the charge current regulation loop begins charging in full power constant-current mode. In this case, the programmed full charge current is set with a resistor on the CL pin.

Depending on available input power and external load conditions, the battery charger may not be able to charge at the full programmed rate. The external load is always prioritized over the battery charge current. The input current limit programming is always observed, and only additional power is available to charge the battery. When system loads are light, battery charge current is maximized.

Once the float voltage is achieved, the battery float voltage regulation loop takes over from the charge current regulation loop and initiates constant voltage charging. In constant voltage charging, charge current slowly declines.

Charge termination can be configured with the TMR pin in several ways. If the TMR pin is tied to the BIAS pin, C/X termination is selected. In this case, charging is terminated when constant voltage charging reduces the charge current to the C/X level programmed at the CX pin. Connecting a capacitor to the TMR pin selects the charge timer termination and a charge termination timer is started at the beginning of constant voltage charging. Charging terminates when the termination timer expires. When continuous charging at the float voltage is desired, tie the TMR pin to GND to disable termination.

Upon charge termination, the PMOS connected to BGATE behaves as an ideal diode from BAT to CSN. The diode function prevents charge current but provides current to the system load as needed. If the system load can be completely supplied from the input, the battery PMOS turns off. While terminated, if the input current limit is not in regulation, the output voltage regulation loop takes over to ensure that the output voltage at CSP remains in control. The output voltage regulation loop regulates the voltage at the CSP pin such that the output feedback voltage at the OFB pin is 1.193V.

If the system load requires more power than is available from the input, the battery ideal diode controller provides supplemental power from the battery. When the battery voltage discharges below 97.1% of the float voltage ( $V_{BFB} < V_{RECHRG(FALL)}$ ), the automatic recharge feature initiates a new charge cycle.

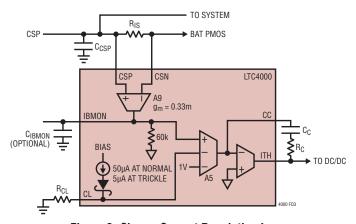

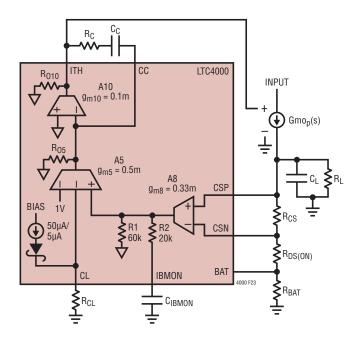

#### **Charge Current Regulation**

The first loop involved in a normal charging cycle is the charge current regulation loop (Figure 3). As with the input current regulation loop, this loop also drives the ITH and CC pins. This loop ensures that the charge current sensed through the charge current sense resistor ( $R_{CS}$ ) does not exceed the programmed full charge current.

Figure 3. Charge Current Regulation Loop

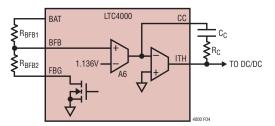

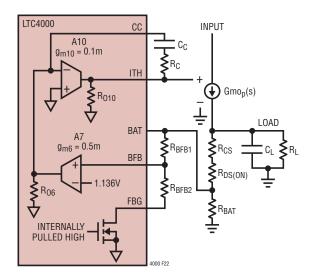

#### **Battery Voltage Regulation**

Once the float voltage is reached, the battery voltage regulation loop takes over from the charge current regulation loop (Figure 4).

The float voltage level is programmed using the feedback resistor divider between the BAT pin and the FBG pin with the center node connected to the BFB pin. Note that the ground return of the resistor divider is connected to the FBG pin. The FBG pin disconnects the resistor divider load when  $V_{\text{IN}} < 3V$  to ensure that the float voltage resistor divider does not consume battery current when the battery is the only available power source. For  $V_{\text{IN}} \geq 3V$ , the typical resistance from the FBG pin to GND is  $100\Omega$ .

Figure 4. Battery Float Voltage Regulation Loop with FBG

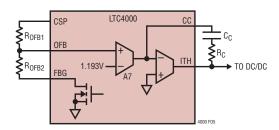

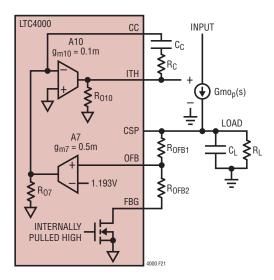

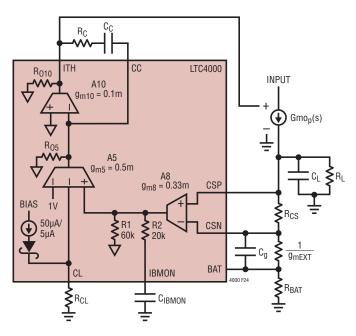

#### **Output Voltage Regulation**

When charging terminates and the system load is completely supplied from the input, the PMOS connected to BGATE is turned off. In this scenario, the output voltage regulation loop takes over from the battery float voltage regulation loop (Figure 5). The output voltage regulation loop regulates the voltage at the CSP pin such that the output feedback voltage at the OFB pin is 1.193V.

Figure 5. Output Voltage Regulation Loop with FBG

#### **Battery Instant-On and Ideal Diode**

The LTC4000 controls the external PMOS connected to the BGATE pin with a controller similar to the input ideal diode controller driving the IGATE pin. When not charging, the PMOS behaves as an ideal diode between the BAT (anode) and the CSN (cathode) pins. The controller (A2) regulates the external PMOS to achieve low loss conduction by driving the gate of the PMOS device such that the voltage drop from the BAT pin to the CSN pin is 8mV. When the ability to deliver a particular current with an 8mV drop across the PMOS source and drain is exceeded, the voltage at the gate clamps at  $V_{BGATE(ON)}$  and the PMOS behaves like a fixed value resistor ( $R_{DS(ON)}$ ).

The ideal diode behavior allows the battery to provide current to the load when the input supply is in current limit or the DC/DC converter is slow to react to an immediate load increase at the output. In addition to the ideal diode

behavior, BGATE also allows current to flow from the CSN pin to the BAT pin during charging.

There are two regions of operation when current is flowing from the CSN pin to the BAT pin. The first is when charging into a battery whose voltage is below the instant-on threshold ( $V_{OFB} < V_{OUT(INST\_ON)}$ ). In this region of operation, the controller regulates the voltage at the CSP pin to be approximately 86% of the final float voltage level ( $V_{OUT(INST\_ON)}$ ). This feature provides a CSP voltage significantly higher than the battery voltage when charging into a heavily discharged battery. This instant-on feature allows the LTC4000 to provide sufficient voltage at the output (CSP pin), independent of the battery voltage.

The second region of operation is when the battery feedback voltage is greater than or equal to the instant-on threshold  $(V_{OUT(INST\_ON)})$ . In this region, the BGATE pin is driven low and clamped at  $V_{BGATE(ON)}$  to allow the PMOS to turn completely on, reducing any power dissipation due to the charge current.

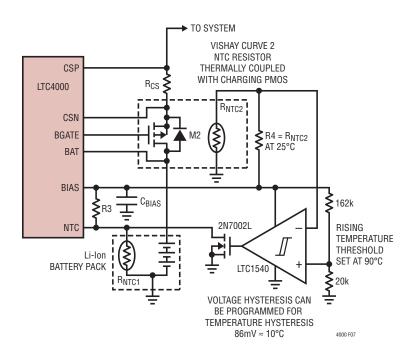

#### **Battery Temperature Qualified Charging**

The battery temperature is measured by placing a negative temperature coefficient (NTC) thermistor close to the battery pack. The comparators CP3 and CP4 implement the temperature detection as shown in the Block Diagram in Figure 1. The rising threshold of CP4 is set at 75% of  $V_{BIAS}$  (cold threshold) and the falling threshold of CP3 is set at 35% of  $V_{BIAS}$  (hot threshold). When the voltage at the NTC pin is above 75% of  $V_{BIAS}$  or below 35% of  $V_{BIAS}$  then the LTC4000 pauses any charge cycle in progress. When the voltage at the NTC pin returns to the range of 40% to 70% of  $V_{BIAS}$ , charging resumes.

When charging is paused, the external charging PMOS turns off and charge current drops to zero. If the LTC4000 is charging in the constant voltage mode and the charge termination timer is enabled, the timer pauses until the thermistor indicates a return to a valid temperature. If the battery charger is in the trickle charge mode and the bad battery detection timer is enabled, the bad battery timer pauses until the thermistor indicates a return to a valid temperature.

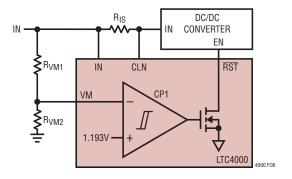

#### Input UVLO and Voltage Monitoring

The regulated voltage on the BIAS pin is available as soon as  $V_{IN} \geq 3V$ . When  $V_{IN} \geq 3V$ , the FBG pin is pulled low to GND with a typical resistance of  $100\Omega$  and the rest of the chip functionality is enabled.

When the IN pin is high impedance and a battery is connected to the BAT pin, the BGATE pin is pulled down with a  $2\mu A$  (typical) current source to hold the battery PMOS gate voltage at  $V_{BGATE(ON)}$  below  $V_{BAT}$ . This allows the battery to power the output. The total quiescent current consumed by LTC4000 from the battery when IN is not valid is typically  $\leq 10\mu A$ .

When the IN pin is high impedance, the input ideal diode function for the external FET connected to the IGATE pin is disabled. To ensure that this FET is completely turned off when the voltage at the IN pin is not within its operating range, connect a 10M pull-up resistor between the IGATE pin and the CSP pin.

Besides the internal input UVLO, the LTC4000 also provides voltage monitoring through the VM pin. The  $\overline{RST}$  pin is pulled low when the voltage on the VM pin falls below 1.193V (typical). On the other hand, when the voltage on the VM pin rises above 1.233V (typical), the  $\overline{RST}$  pin is high impedance.

One common use of this voltage monitoring feature is to ensure that the converter is turned off when the voltage at the input is below a certain level. In this case, connect the  $\overline{RST}$  pin to the DC/DC converter chip select or enable pin (see Figure 6).

Figure 6. Input Voltage Monitoring with  $\overline{\text{RST}}$  Connected to the EN Pin of the DC/DC Converter

#### Input Ideal Diode PMOS Selection

The input external PMOS is selected based on the expected maximum current, power dissipation and reverse voltage drop. The PMOS must be able to withstand a gate to source voltage greater than  $V_{IGATE(ON)}$  (15V maximum) or the maximum regulated voltage at the IID pin, whichever is less. A few appropriate external PMOS for a number of different requirements are shown at Table 1.

Table 1. PMOS

| PART NUMBER | $R_{DS(ON)}$ AT $V_{GS} = 10V$ $(\Omega)$ | MAX ID (A) | MAX VDS<br>(V) | MANUFACTURER |

|-------------|-------------------------------------------|------------|----------------|--------------|

| SiA923EDJ   | 0.054                                     | 4.5        | -20            | Vishay       |

| Si9407BDY   | 0.120                                     | 4.7        | -60            | Vishay       |

| Si4401BDY   | 0.014                                     | 10.5       | -40            | Vishay       |

| Si4435DDY   | 0.024                                     | 11.4       | -30            | Vishay       |

| SUD19P06-60 | 0.060                                     | 18.3       | -60            | Vishay       |

| Si7135DP    | 0.004                                     | 60         | -30            | Vishay       |

Note that in general the larger the capacitance seen on the IGATE pin, the slower the response of the ideal diode driver. The fast turn off and turn on current is limited to -0.5mA and 0.7mA typical respectively ( $I_{IGATE(FASTOFF)}$ ) and  $I_{IGATE(FASTON)}$ ). If the driver can not react fast enough to a sudden increase in load current, most of the extra current is delivered through the body diode of the external PMOS. This increases the power dissipation momentarily. It is important to ensure that the PMOS is able to withstand this momentary increase in power dissipation.

The operation section also mentioned that an external 10M pull-up resistor is recommended between the IGATE pin and the CSP pin when the IN pin voltage is expected to be out of its operating range, at the same time that the external input ideal diode PMOS is expected to be completely turned off. Note that this additional pull-up resistor increases the forward voltage regulation of the ideal diode function ( $V_{IID,CSP}$ ) from the typical value of 8mV.

The increase in this forward voltage is calculated according to the following formula:

$$\Delta V_{IID,CSP REG} = V_{GSON} \cdot 20k/R_{IGATE}$$

where  $V_{GSON}$  is the source to gate voltage required to achieve the desired ON resistance of the external PMOS and  $R_{IGATE}$  is the external pull-up resistor from the IGATE

pin to the CSP pin. Therefore, for a 10M  $R_{IGATE}$  resistor and assuming a 10V  $V_{GSON}$ , the additional forward voltage regulation is  $\Delta V_{IID,CSP\;REG}$  = 20mV, and the total forward voltage regulation is 28mV (typ). It is recommended to set the  $R_{IGATE}$  such that this additional forward voltage regulation value does not exceed 40mV.

### **Input Current Limit Setting and Monitoring**

The regulated input current limit is set using a resistor at the IL pin according to the following formula:

$$R_{IS} = \frac{V_{IL}}{20 \bullet I_{ILIM}}$$

where  $V_{IL}$  is the voltage on the IL pin. The IL pin is internally pulled up with an accurate current source of  $50\mu A$ . Therefore an equivalent formula to obtain the input current limit is:

$$R_{IL} = \frac{I_{LIM} \bullet R_{IS}}{2.5 \mu A} \Rightarrow I_{ILIM} = \frac{R_{IL}}{R_{IS}} \bullet 2.5 \mu A$$

The input current through the sense resistor is available for monitoring through the IIMON pin. The voltage on the IIMON pin varies with the current through the sense resistor as follows:

$$V_{IIMON} = 20 \bullet I_{RIS} \bullet R_{IS} = 20 \bullet (V_{IN} - V_{CLN})$$

The regulation voltage level at the IIMON pin is clamped at 1V with an accurate internal reference. At 1V on the IIMON pin, the input current limit is regulated at the following value:

$$I_{\text{ILIM(MAX)}}(A) = \frac{0.050V}{R_{IS}(\Omega)}$$

When this maximum current limit is desired, leave the IL pin open or set it to a voltage >1.05V such that amplifier A4 can regulate the IIMON voltage accurately to the internal reference of 1V.

If the input current is noisy, add a filter capacitor to the CLN pin to reduce the AC content. For example, when using a buck DC/DC converter, the use of a  $C_{CLN}$  capacitor is strongly recommended. Where the highest accuracy is important, pick the value of  $C_{CLN}$  such that the AC content is less than or equal to 50% of the average voltage across the sense resistor.

The voltage on the IIMON pin can be filtered further by putting a capacitor on the pin ( $C_{IIMON}$ ). The voltage on the IIMON pin is also the feedback input to the input current regulation error amplifier. Any capacitor connected to this pin places a pole in the input current regulation loop. Therefore, this filter capacitor should NOT be arbitrarily large as it will slow down the overall compensated loop. For details on loop compensation please refer to the Compensation section.

### **Charge Current Limit Setting and Monitoring**

The regulated full charge current is set according to the following formula:

$$R_{CS} = \frac{V_{CL}}{20 \bullet I_{CLIM}}$$

where  $V_{CL}$  is the voltage on the CL pin. The CL pin is internally pulled up with an accurate current source of 50 $\mu$ A. Therefore, an equivalent formula to obtain the input current limit is:

$$R_{CL} = \frac{I_{CLIM} \bullet R_{CS}}{2.5 \mu A} \Rightarrow I_{CLIM} = \frac{R_{CL}}{R_{CS}} \bullet 2.5 \mu A$$

The charge current through the sense resistor is available for monitoring through the IBMON pin. The voltage on the IBMON pin varies with the current through the sense resistor as follows:

$$V_{IBMON} = 20 \bullet I_{RCS} \bullet R_{CS} = 20 \bullet (V_{CSP} - V_{CSN})$$

Similar to the IIMON pin, the regulation voltage level at the IBMON pin is clamped at 1V with an accurate internal reference. At 1V on the IBMON pin, the charge current limit is regulated to the following value:

$$I_{\text{CLIM(MAX)}}(A) = \frac{0.050V}{R_{\text{CS}}(\Omega)}$$

When this maximum charge current limit is desired, leave the CL pin open or set it to a voltage >1.05V such that amplifier A5 can regulate the IBMON pin voltage accurately to the internal reference of 1V.

When the output current waveform of the DC/DC converter or the system load current is noisy, it is recommended that a capacitor is connected to the CSP pin ( $C_{CSP}$ ). This is to

reduce the AC content of the current through the sense resistor ( $R_{CS}$ ). Where the highest accuracy is important, pick the value of  $C_{CSP}$  such that the AC content is less than or equal to 50% of the average voltage across the sense resistor. Similar to the IIMON pin, the voltage on the IBMON pin is filtered further by putting a capacitor on the pin ( $C_{IBMON}$ ). This filter capacitor should *not* be arbitrarily large as it will slow down the overall compensated charge current regulation loop. For details on the loop compensation, refer to the Compensation section.

### **Battery Float Voltage Programming**

When the value of  $R_{BFB1}$  is much larger than  $100\Omega$ , the final float voltage is determined using the following formula:

$$R_{BFB1} = \left(\frac{V_{FLOAT}}{1.136V} - 1\right) R_{BFB2}$$

When higher accuracy is important, a slightly more accurate final float voltage can be determined using the following formula:

$$V_{FLOAT} = \left(\frac{R_{BFB1} + R_{BFB2}}{R_{BFB2}} \bullet 1.136V\right) - \left(\frac{R_{BFB1}}{R_{BFB2}} \bullet V_{FBG}\right)$$

where  $V_{FBG}$  is the voltage at the FBG pin during float voltage regulation, which accounts for all the current from all resistor dividers that are connected to this pin  $(R_{FBG} = 100\Omega \text{ typical})$ .

## Low Battery Trickle Charge Programming and Bad Battery Detection

When charging into an over-discharged or dead battery  $(V_{BFB} < V_{LOBAT})$ , the pull-up current at the CL pin is reduced to 10% of the normal pull-up current. Therefore, the trickle charge current is set using the following formula:

$$R_{CL} = \frac{I_{CLIM(TRKL)} \bullet R_{CS}}{0.25 \mu A} \Rightarrow I_{CLIM(TRKL)} = 0.25 \mu A \bullet \frac{R_{CL}}{R_{CS}}$$

Therefore, when  $50\mu A \cdot R_{CL}$  is less than 1V, the following relation is true:

$$I_{\text{CLIM}(\text{TRKL})} = \frac{I_{\text{CLIM}}}{10}$$

Once the battery voltage rises above the low battery voltage threshold, the charge current level rises from the trickle charge current level to the full charge current level.

The LTC4000 also features bad battery detection. This detection is disabled if the TMR pin is grounded or tied to BIAS. However, when a capacitor is connected to the TMR pin, a bad battery detection timer is started as soon as trickle charging starts. If at the end of the bad battery detection time the battery voltage is still lower than the low battery threshold, charging is terminated and the part indicates a bad battery condition by pulling the FLT pin low and leaving the CHRG pin high impedance.

The bad battery detection time can be programmed according to the following formula:

$$C_{TMR}(nF) = t_{BADBAT}(h) \cdot 138.5$$

Note that once a bad battery condition is detected, the condition is latched. In order to re-enable charging, remove the battery and connect a new battery whose voltage causes BFB to rise above the recharge battery threshold (V<sub>RECHRG(RISE)</sub>). Alternatively toggle the ENC pin or remove and reapply power to IN.

# C/X Detection, Charge Termination and Automatic Recharge

Once the constant voltage charging is reached, there are two ways in which charging can terminate. If the TMR pin is tied to BIAS, the battery charger terminates as soon as the charge current drops to the level programmed by the CX pin. The C/X current termination level is programmed according to the following formula:

$$R_{CX} = \frac{\left(I_{C/X} \bullet R_{CS}\right) + 0.5 mV}{0.25 \mu A} \Longrightarrow I_{C/X} = \frac{\left(0.25 \mu A \bullet R_{CX}\right) - 0.5 mV}{R_{CS}}$$

where  $R_{CS}$  is the charge current sense resistor connected between the CSP and the CSN pins.

When the voltage at BFB is higher than the recharge threshold (97.6% of float), the C/X comparator is enabled. In order to ensure proper C/X termination coming out of a paused charging condition, connect a capacitor on the CX pin according to the following formula:

$$C_{CX} = 100C_{BGATE}$$

where  $C_{\mbox{\footnotesize{BGATE}}}$  is the total capacitance connected to the BGATE pin.

For example, a typical capacitance of 1nF requires a capacitor greater than 100nF connected to the CX pin to ensure proper C/X termination behavior.

If a capacitor is connected to the TMR pin, as soon as the constant voltage charging is achieved, a charge termination timer is started. When the charge termination timer expires, the charge cycle terminates. The total charge termination time can be programmed according to the following formula:

$$C_{TMR}(nF) = t_{TERMINATE}(h) \cdot 34.6$$

If the TMR pin is grounded, charging never terminates and the battery voltage is held at the float voltage. Note that regardless of which termination behavior is selected, the  $\overline{\text{CHRG}}$  and  $\overline{\text{FLT}}$  pins will both assume a high impedance state as soon as the charge current falls below the programmed C/X level.

After the charger terminates, the LTC4000 automatically restarts another charge cycle if the battery feedback voltage drops below 97.1% of the programmed final float voltage ( $V_{RECHRG(FALL)}$ ). When charging restarts, the  $\overline{CHRG}$  pin pulls low and the  $\overline{FLT}$  pin remains high impedance.

#### **Output Voltage Regulation Programming**

The output voltage regulation level is determined using the following formula:

$$R_{OFB1} = \left(\frac{V_{OUT}}{1.193} - 1\right) \cdot R_{OFB2}$$

As in the battery float voltage calculation, when higher accuracy is important, a slightly more accurate output is determined using the following formula:

$$V_{OUT} = \left(\frac{R_{OFB1} + R_{OFB2}}{R_{OFB2}} \bullet 1.193V\right) - \left(\frac{R_{OFB1}}{R_{OFB2}} \bullet V_{FBG}\right)$$

where V<sub>FBG</sub> is the voltage at the FBG pin during output voltage regulation, which accounts for all the current from all resistor dividers that are connected to this pin.

# Battery Instant-On and Ideal Diode External PMOS Consideration

The instant-on voltage level is determined using the following formula:

$$V_{OUT(INST\_ON)} = \frac{R_{OFB1} + R_{OFB2}}{R_{OFB2}} \bullet 0.974V$$

Note that  $R_{OFB1}$  and  $R_{OFB2}$  are the same resistors that program the output voltage regulation level. Therefore, the output voltage regulation level is always 122.5% of the instant-on voltage level.

During instant-on operation, it is critical to consider the charging PMOS power dissipation. When the battery voltage is below the low battery threshold ( $V_{LOBAT}$ ), the power dissipation in the PMOS can be calculated as follows:

$$P_{TRKL} = [0.86 \bullet V_{FLOAT} - V_{BAT}] \bullet I_{CLIM(TRKL)}$$

where I<sub>CLIM(TRKL)</sub> is the trickle charge current limit.

On the other hand, when the battery voltage is above the low battery threshold but still below the instant-on threshold, the power dissipation can be calculated as follows:

$$P_{INST-ON} = [0.86 \bullet V_{FLOAT} - V_{BAT}] \bullet I_{CLIM}$$

where I<sub>CLIM</sub> is the full scale charge current limit.

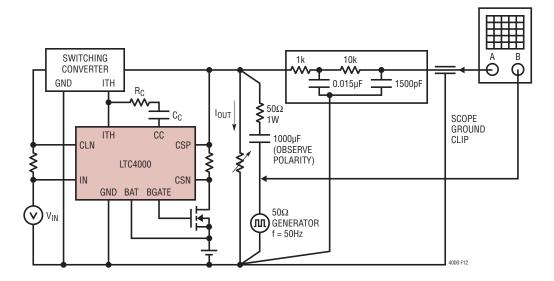

For example, when charging a 3-cell Lithium Ion battery with a programmed full charged current of 1A, the float voltage is 12.6V, the bad battery voltage level is 8.55V and the instant-on voltage level is 10.8V. During instant-on operation and in the trickle charge mode, the worst case maximum power dissipation in the PMOS is 1.08W. When the battery voltage is above the bad battery voltage level, then the worst case maximum power dissipation is 2.25W.