# S-34HTS08AB

#### www.ablic.com

## DDR5 SPD EEPROM WITH HUB BUILT-IN TEMPERATURE SENSOR

© ABLIC Inc., 2023-2024

Rev.1.1\_00

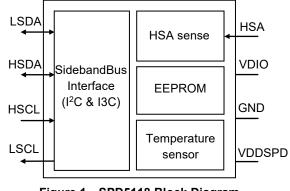

This IC is a DDR5 Serial Presence Detect EEPROM with Hub function (SPD5 Hub) built in temperature sensor.

The Hub feature allows isolation of a local bus from a controller host bus. This IC contains 1024 bytes (8K-bit) of EEPROM arranged as 16 blocks of 64 bytes (512 bit) per block. Each block can be write protected via software command. Page write and sequential read are available. This IC operates with 1.8 V VDDSPD and 1.0 V VDDIO and the SidebandBus (I<sup>2</sup>C & I3C) at 12.5 MHz maximum.

Caution This product is intended to use in general electronic devices such as consumer electronics, office equipment, and communications devices. Before using the product in medical equipment or automobile equipment including car audio, keyless entry and engine control unit, contact to ABLIC Inc. is indispensable.

#### Features

- JEDEC standard compliant: SPD5118

- Two-wire I<sup>2</sup>C or I3C bus serial interface

- Operation voltage range (V<sub>DDSPD</sub>): 1.7 V to 1.98 V

- Operation voltage range (V<sub>DDIO</sub>): 0.95 V to 1.05 V

- Operation frequency: I<sup>2</sup>C: 1.0 MHz max. (V<sub>DDSPD</sub> = 1.7 V to 1.98 V) I3C: 12.5 MHz max. (V<sub>DDSPD</sub> = 1.7 V to 1.98V)

- 1.0 V Push Pull I/O levels

- 1.0 V and 3.3 V Open Drain I/O levels

- Operation temperature range: Ta = -40°C to +125°C

- Operation temperature range (NVM Write Operation): Ta = -40°C to +95°C

#### EEPROM

- Page write:16 bytes / page

- Sequential read

- Write protect function during low power supply voltage

- Write protect: Individual software data protection for each of 16 blocks of 64-bytes per block

- Endurance: 10<sup>5</sup> cycle / word<sup>\*1</sup> (Ta = -40°C to +95°C)

- Memory capacity: 8 K-bit

- Initial delivery state: FFh

#### Temperature sensor

- Temperature accuracy: 0.5°C typ. (Ta = +75°C to +95°C) 1.0°C typ. (Ta = +40°C to +125°C)

- Temperature sample rate: 8 samples / s min.

- hysteresis width: 1.0°C

#### **Hub Function**

- Interfaces to I<sup>2</sup>C/I3C buses which have multiple devices on a shared bus

- Uniquely addressed with fixed addressing on the same bus.

- All Hubs respond to specific predefined I<sup>2</sup>C/I3C device select codes on a host interface bus

- Integrates a second local I<sup>2</sup>C/I3C bus and passes through of commands from host bus onto local bus for addressing of I<sup>2</sup>C/I3C devices on local bus

#### Overall

- Current consumption: EEPROM in standby mode and temperature sensor in active mode: 0.15 mA max.\*<sup>2</sup> EEPROM in read operation mode and temperature sensor in active mode: 2.0 mA max.\*<sup>2</sup> EEPROM in write operation mode and temperature sensor in active mode: 3.0 mA max.\*<sup>2</sup>

- Noise suppression: Schmitt trigger on input pins (HSCL, HSDA, LSDA) Noise filter on input pins at I<sup>2</sup>C (HSCL, HSDA)

- Packet Error Check (PEC) function

- Parity Error check function

- In Band Interrupt (IBI)

- Bus Reset function

- Up to 8 unique addressing

- 9-pin thermally enhanced DFN package

- \*1. For each address (Word: 8-bit)

- \*2. V<sub>DDSPD</sub> = 1.8V

## Block Diagram

Figure 1 SPD5118 Block Diagram

## Package

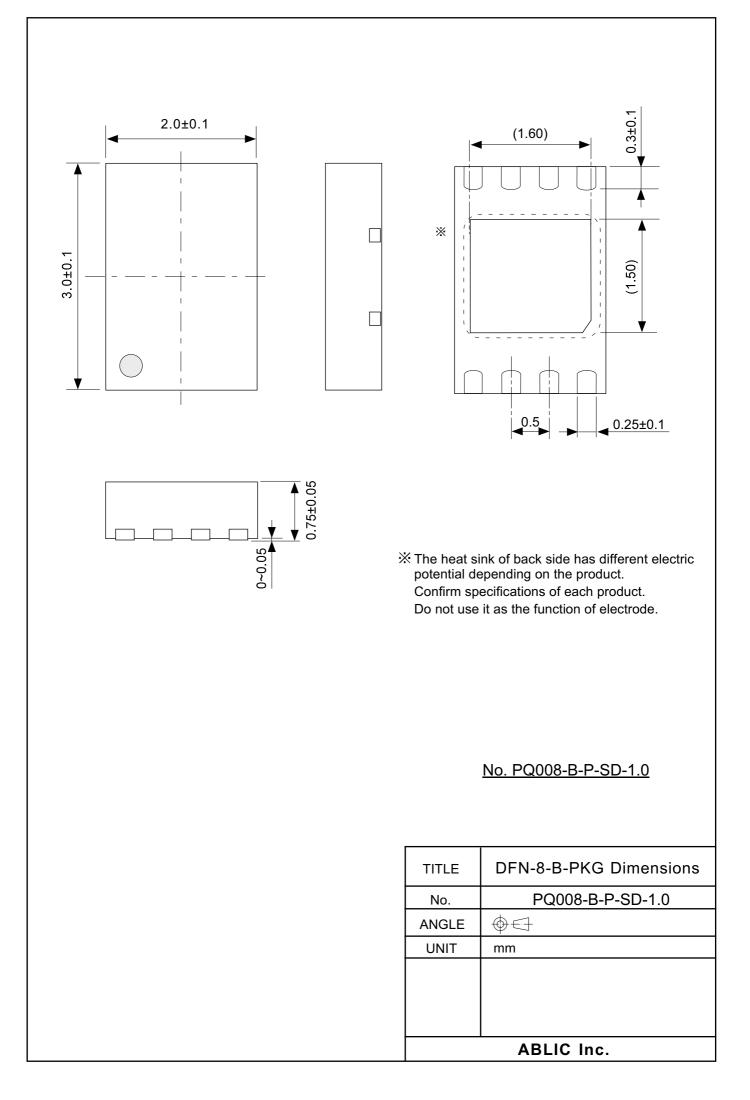

• DFN-8(2030)B

ABLIC Inc.

# DDR5 SPD EEPROM WITH HUB BUILT-IN TEMPERATURE SENSOR S-34HTS08AB

#### Contents

|   | Prod  | luct Name Structure                                                                          | 4  |

|---|-------|----------------------------------------------------------------------------------------------|----|

|   | 1. F  | Product name                                                                                 | 4  |

| 2 | 2. F  | Product name list                                                                            | 4  |

| 3 | 3. F  | Package                                                                                      | 4  |

|   | Pin ( | Configuration                                                                                | 5  |

|   | 1. C  | DFN-8(2030)B                                                                                 | 5  |

|   |       | ction Description                                                                            |    |

|   | 1. C  | Dverview                                                                                     | 6  |

| 2 | 2. F  | Power-up, Reset and Initialization                                                           | 6  |

|   | 2. 1  |                                                                                              |    |

|   | 2. 2  | 2 Device Reset and Initialization                                                            | 7  |

|   | 2.3   | Bus Clear                                                                                    | 7  |

|   | 2. 4  |                                                                                              |    |

| 3 | 3. C  | Device Interface - IO Voltage Configuration                                                  | 8  |

|   | 3. 1  | Open Drain Interface                                                                         | 8  |

|   | 3. 2  | 2 Push Pull Interface                                                                        | 9  |

|   | 3. 3  | 3 IO Operation                                                                               | 9  |

| 4 | 1. C  | Device Interface - Protocol                                                                  | 10 |

|   | 4. 1  | I I <sup>2</sup> C and I3C Protocol                                                          | 10 |

|   | 4. 2  | 2 Switch from I <sup>2</sup> C Mode to I3C Basic Mode                                        | 10 |

|   | 4.3   | 3 Switch from I3C Basic Mode to I <sup>2</sup> C Mode                                        | 10 |

|   | 4.4   | 7-bit Serial Address                                                                         | 10 |

|   | 4.5   | 5 Device Selection on I <sup>2</sup> C / I3C Bus                                             | 11 |

|   | 4.6   | 6 I <sup>2</sup> C Target Protocol - Host to SPD5 Hub Device                                 | 13 |

|   | 4.7   | <sup>7</sup> I <sup>2</sup> C Target Protocol - Host to Local Device through SPD5 Hub Device | 15 |

|   | 4.8   | 3 I3C Basic Target Protocol - Host to SPD5 Hub Device                                        | 17 |

|   | 4.9   | I3C Basic Target Protocol - Host to Local Device through SPD5 Hub                            | 23 |

| Ę | 5. V  | Vrite and Read Access                                                                        | 24 |

|   | 5. 1  | Write and Read Access - NVM Memory                                                           | 24 |

|   | 5. 2  | 2 Write and Read Access - Register                                                           | 24 |

| 6 | 5. V  | Vrite Protection of Non Volatile Memory                                                      |    |

|   | 6. 1  |                                                                                              |    |

|   | 6. 2  |                                                                                              |    |

|   | 6.3   |                                                                                              |    |

| 7 | 7. 13 | 3C Basic Common Command Codes (CCC)                                                          |    |

|   | 7. 1  |                                                                                              |    |

|   | 7.2   |                                                                                              |    |

|   | 7.3   |                                                                                              |    |

|   | 7.4   |                                                                                              | -  |

|   | 7.5   |                                                                                              | -  |

|   | 7.6   |                                                                                              |    |

|   | 7.7   |                                                                                              |    |

|   | 7.8   | B DEVCTRL CCC                                                                                |    |

| 8 | 3. C  | Command Truth Table                                                                          |    |

| ç |       | n Band Interrupt (IBI)                                                                       |    |

|   | 9.1   |                                                                                              |    |

|   | 9.2   |                                                                                              |    |

|   | 9.3   |                                                                                              |    |

|   | 9.4   |                                                                                              |    |

|   | 9.5   |                                                                                              |    |

|   | 9.6   |                                                                                              |    |

|   |       | Error Check Function                                                                         |    |

|   | 10.   |                                                                                              |    |

|   | 10.   |                                                                                              |    |

|   | 10.   | •                                                                                            |    |

|   |       | isters                                                                                       |    |

|   |       | Register Map                                                                                 |    |

|   |       |                                                                                              |    |

# DDR5 SPD EEPROM WITH HUB BUILT-IN TEMPERATURE SENSOR S-34HTS08AB

Rev.1.1\_00

| 2.   | Re    | gister Attribute Definition                                            | 51 |

|------|-------|------------------------------------------------------------------------|----|

| 3.   | Re    | gister Description                                                     | 51 |

| 3    | . 1   | Register MR0 & MR1                                                     | 51 |

| 3    | . 2   | Register MR2                                                           |    |

| 3    | . 3   | Register MR3 & MR4                                                     |    |

| 3    | . 4   | Register MR5                                                           | 53 |

| 3    | . 5   | Register MR6                                                           | 53 |

| 3    | . 6   | Register MR11                                                          |    |

| 3    | . 7   | Register MR12 & MR13                                                   |    |

| 3    | . 8   | Register MR14                                                          |    |

| 3    | . 9   | Register MR18                                                          | 57 |

| 3    | . 10  | Register MR19                                                          |    |

| 3    | . 11  | Register MR20                                                          |    |

| 3    | . 12  | Register MR26                                                          | 59 |

| 3    | . 13  | Register MR27                                                          | 60 |

| 3    | . 14  | Register MR28 & MR29                                                   |    |

| 3    | . 15  | Register MR30 & MR31                                                   | 61 |

| 3    | . 16  | Register MR32 & MR33                                                   | 62 |

| 3    | . 17  | Register MR34 & MR35                                                   | 62 |

| 3    | . 18  | Thermal Sensor Registers Read Out Mechanism                            | 63 |

| 3    | . 19  | Register MR36                                                          | 64 |

| 3    | . 20  | Register MR37                                                          |    |

| 3    | . 21  | Register MR48                                                          |    |

| 3    | . 22  | Register MR49 & MR50                                                   |    |

| 3    | . 23  | Register MR51                                                          |    |

| 3    | . 24  | Register MR52                                                          |    |

|      | . 25  | Register MR53                                                          |    |

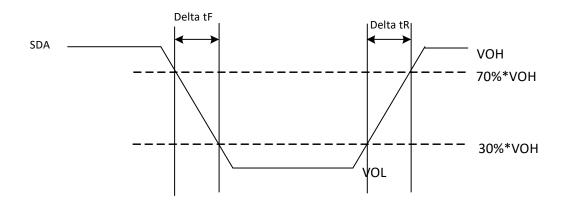

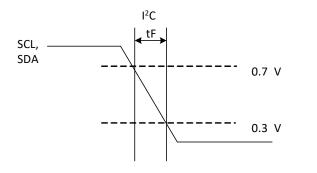

| A    | C Tir | ning Definition                                                        |    |

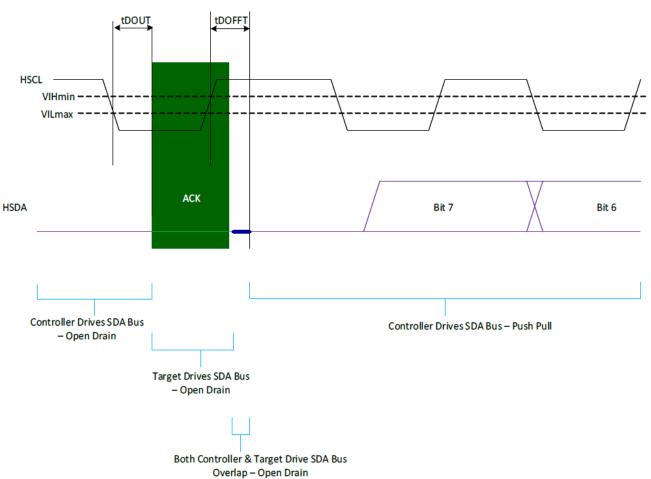

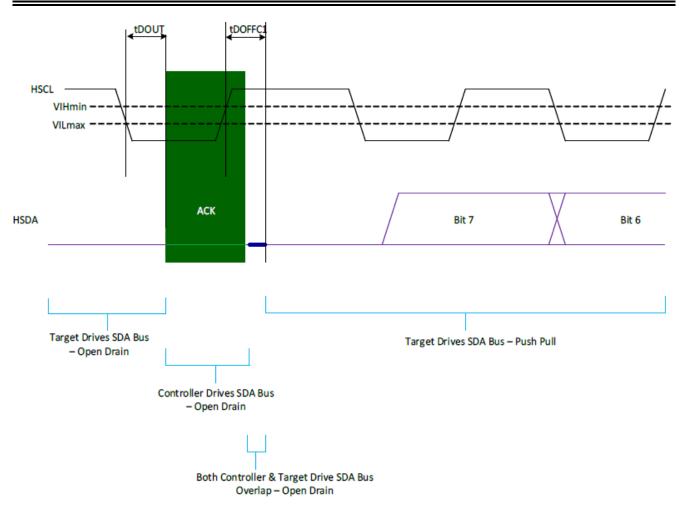

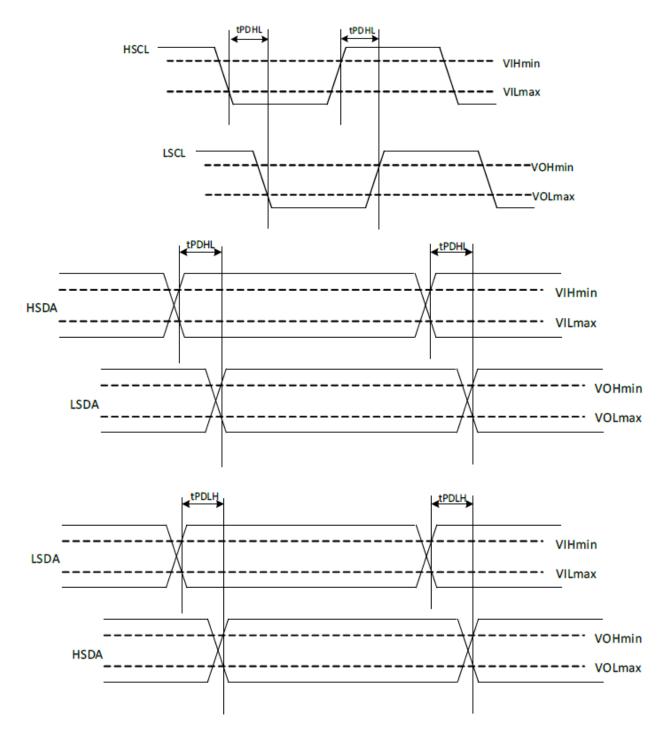

| 1.   |       | en Drain to Push Pull Timing                                           |    |

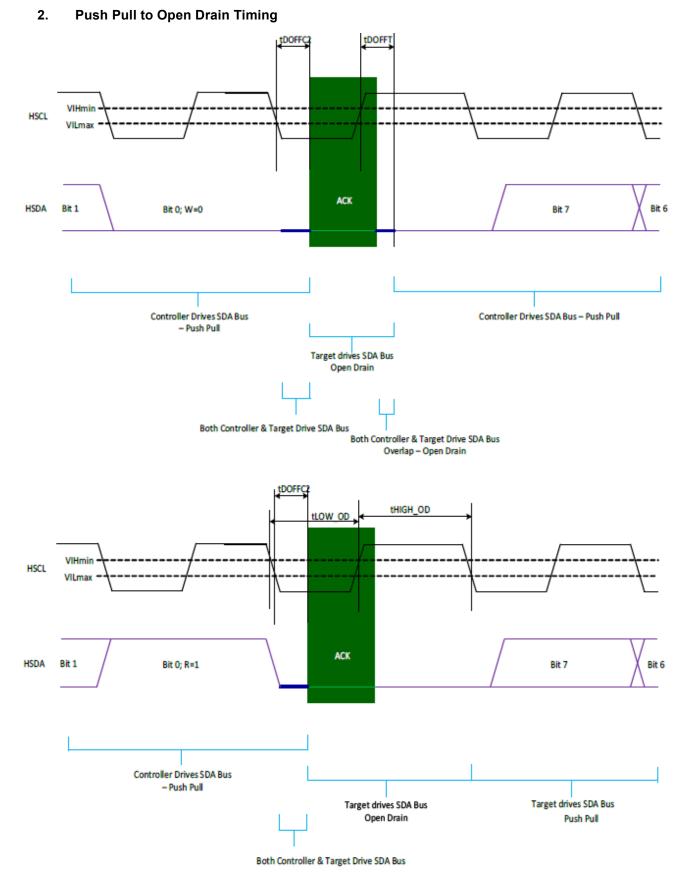

| 2.   |       | sh Pull to Open Drain Timing                                           |    |

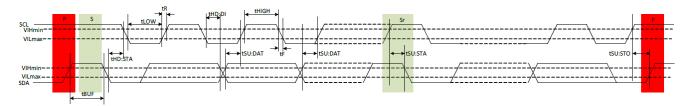

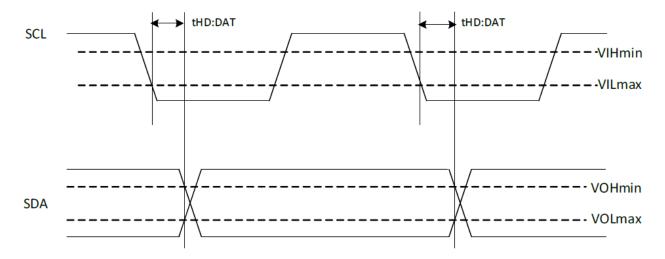

| 3.   | ST    | ART and STOP Timing                                                    | 72 |

| 4.   |       | or I3C Basic Bus Timing                                                |    |

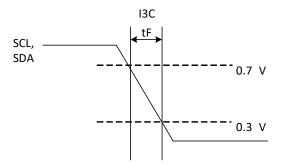

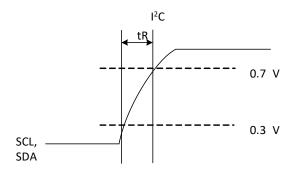

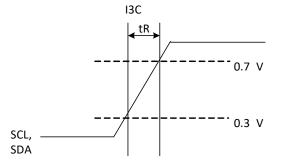

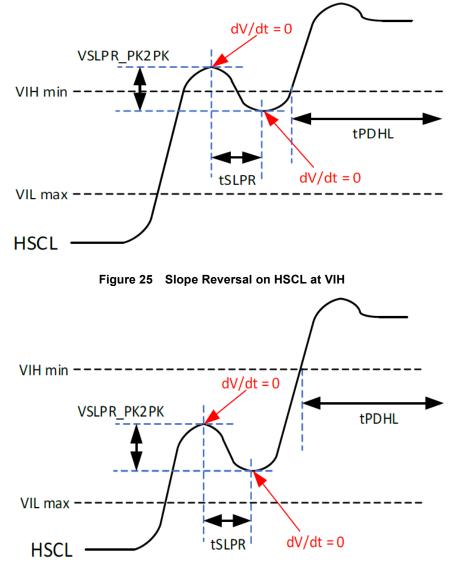

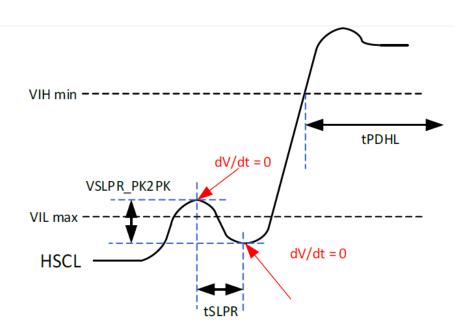

| 5.   |       | CL Non Monotonicity                                                    |    |

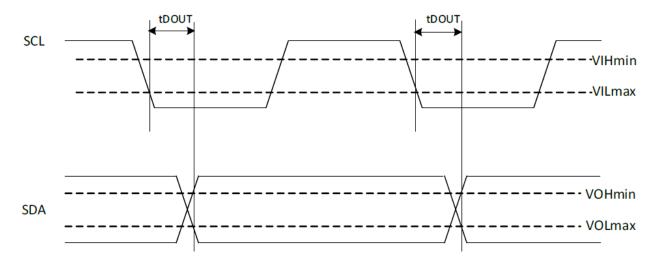

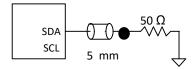

| 6.   |       | b Propagation Delay                                                    |    |

| ■ El |       | cal Characteristics                                                    |    |

| 1.   |       | solute Maximum Ratings                                                 |    |

| 2.   | Ор    | erating Conditions, Measurement Conditions & DC and AC Characteristics |    |

| 2    | . 1   | Operating Conditions                                                   | 79 |

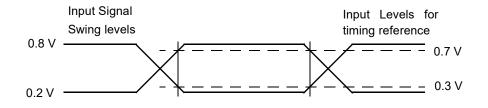

|      | . 2   | AC Measurement Conditions                                              |    |

| _    | . 3   | DC Electrical Characteristics                                          |    |

|      | . 4   | AC Electrical Characteristic                                           |    |

| 3.   |       | mperature Sensor Performance                                           |    |

| ■ Pr | ecau  | utions                                                                 | 85 |

# DDR5 SPD EEPROM WITH HUB BUILT-IN TEMPERATURE SENSOR S-34HTS08AB

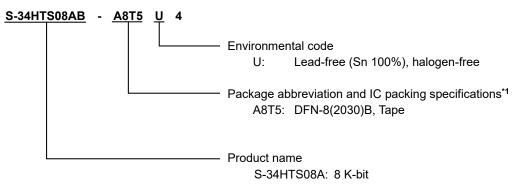

## Product Name Structure

### 1. Product name

#### \*1. Refer to the tape drawing.

## 2. Product name list

| Та                 | ble 1 Product name list |              |

|--------------------|-------------------------|--------------|

| Product Name       | Capacity                | Package Name |

| S-34HTS08AB-A8T5U4 | 8 K-bit                 | DFN-8(2030)B |

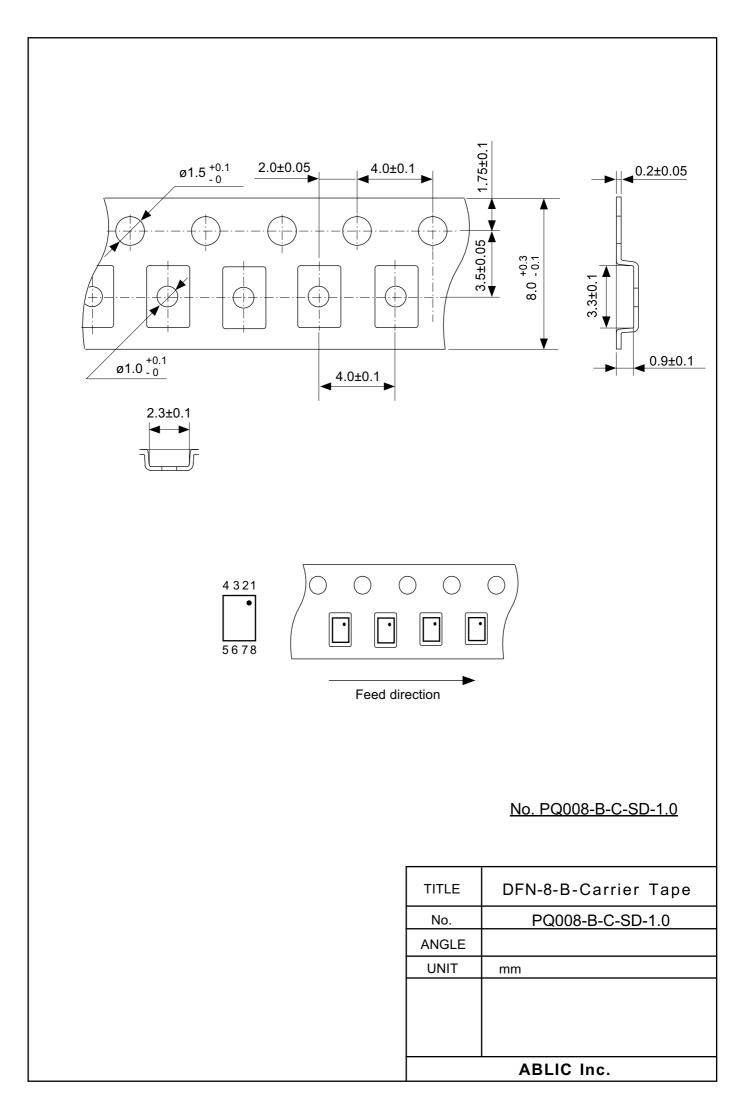

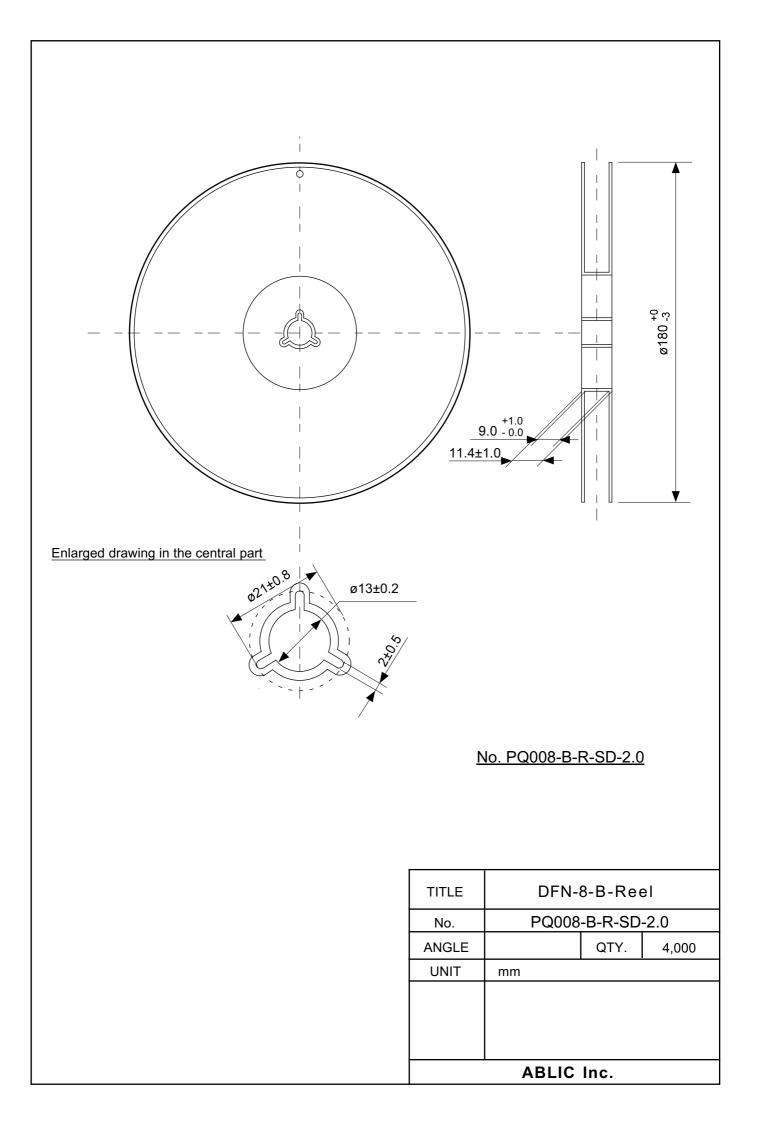

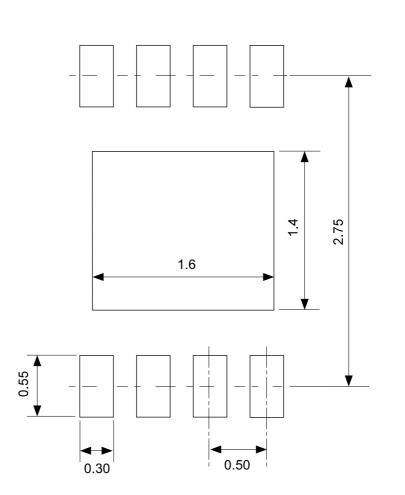

#### 3. Package

| Table 2 | Package |

|---------|---------|

|         | ruchuge |

| Package Name | Dimension    | Таре         | Reel         | Land         |

|--------------|--------------|--------------|--------------|--------------|

| DFN-8(2030)B | PQ008-B-P-SD | PQ008-B-C-SD | PQ008-B-R-SD | PQ008-B-L-SD |

Rev.1.1 00

#### Pin Configuration

#### DFN-8(2030)B 1.

|                 |            |   |            |        | Tal                                                                                                   | ble 3 Pin Configuration                                                  |  |  |

|-----------------|------------|---|------------|--------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|

|                 | Top view   |   | Pin<br>No. | Symbol | Pin Type                                                                                              | Description                                                              |  |  |

| 1               | $\bigcirc$ | 8 | 1          | LSDA   | I/O                                                                                                   | Local Bus - I <sup>2</sup> C/I3C Basic Bus Data Input/Output             |  |  |

| 2               | $\bigcirc$ | 7 | 2          | HSDA   | I/O                                                                                                   | Host Bus - I <sup>2</sup> C/I3C Basic Bus Data Input/Output              |  |  |

| 3               |            | 6 | 3          | HSCL   |                                                                                                       | Host Bus - I <sup>2</sup> C/I3C Basic Bus Input Clock                    |  |  |

| -               |            |   | 4          | LSCL   | 0                                                                                                     | Local Bus - I <sup>2</sup> C/I3C Basic Bus Output Clock                  |  |  |

| 4 5<br>Figure 2 |            | 5 | 5          | VDDSPD | Power                                                                                                 | 1.8 V Input Power Supply.<br>Connect minimum of 1.0 μF capacitor to GND. |  |  |

|                 |            |   | 6          | GND    | GND                                                                                                   | Ground                                                                   |  |  |

|                 |            |   | 7          | VDDIO  | Power                                                                                                 | 1.0 V Input Power Supply.<br>Connect minimum of 1.0 μF capacitor to GND. |  |  |

|                 |            | 8 | HSA        | I      | Host Bus - I <sup>2</sup> C/I3C Basic Bus Address Pin.<br>Refer to <b>Table 4</b> for HID definition. |                                                                          |  |  |

Remark For DFN-8(2030)B package, connect the heatsink of back side to the board, and set electric potential open or GND. However, do not use it as the function of electrode.

| HSA Pin Connection   | 3-bit HID | Comment                                       |

|----------------------|-----------|-----------------------------------------------|

| 10.0 kΩ to GND       | 000       |                                               |

| 15.4 kΩ to GND       | 001       |                                               |

| 23.2 kΩ to GND       | 010       |                                               |

| 35.7 kΩ to GND       | 011       |                                               |

| 54.9 kΩ to GND       | 100       | 1% Resistor                                   |

| 84.5 kΩ to GND       | 101       |                                               |

| 127 kΩ to GND        | 110       |                                               |

| 196 kΩ to GND        | 111       |                                               |

| Tied directly to GND | 000       | Offline Mode: Write protect override enabled. |

The table above shows the HSA pin resistor values and corresponding 3-bit HID for the SPD5 Hub device.

## Function Description

#### 1. Overview

The SPD5 Hub device S-34HTS08AB contains 1024 bytes of non-volatile memory arranged as 16 blocks of 64 bytes per block. Each block may optionally be write-protected via software command. Write protection for each block may be overridden in an offline programmer environment while overrides are prevented in normal use. The SPD5 Hub device operates from 1.8 V nominal power supply input. The SPD5 Hub device is intended to operate up to 12.5 MHz on a 1.0 V I3C Basic bus or up to 1 MHz on a 1.0 V to 3.3 V I<sup>2</sup>C bus. It is designed to interface to I<sup>2</sup>C/I3C Basic buses which have multiple devices on a shared bus and must be uniquely addressed with fixed addressing on the same bus. All SPD5 Hub devices respond to specific pre-defined I<sup>2</sup>C/I3C Basic device select codes on a host interface bus. The device also incorporates a second local I<sup>2</sup>C/I3C Basic bus and passes through of commands from the host bus onto the local bus for addressing I<sup>2</sup>C/I3C Basic devices on the local bus (Hub function).

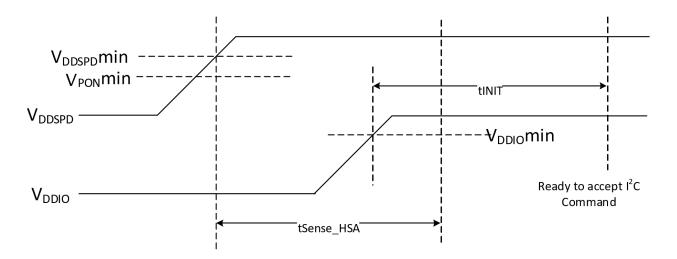

#### 2. Power-up, Reset and Initialization

#### 2.1 Device Power Up

The SPD5 Hub device has one VDDSPD power supply input.

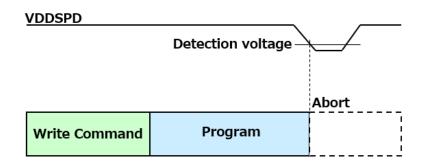

In order to prevent inadvertent operations during power up, a Power On Reset (POR) circuit is included. On cold power on, V<sub>DDSPD</sub> input supply must rise monotonically between V<sub>PON</sub> and V<sub>DDSPD</sub>min.

And meanwhile, V<sub>DDIO</sub> input supply must rise monotonically to V<sub>DDIO</sub>min without ring back to ensure proper startup. The SPD5 Hub device uses the V<sub>DDIO</sub> supply for its I/O levels and it must reach V<sub>DDIO</sub>min to ensure proper operation of I<sup>2</sup>C or I3C bus interface.

Once the V<sub>DDSPD</sub> and V<sub>DDIO</sub> supply is valid and stable, the SPD5 Hub device shall:

- Once V<sub>DDSPD</sub> supply is valid and stable, within t<sub>Sense\_HSA</sub> time, sense its HSA pin to determine if SPD5 Hub device is in application environment or in an offline tester program mode. Depending on what it senses on HSA pin, the SPD5 Hub device configures its HID code automatically based on what it detects on HSA pin at power up.

- 2. Enable I<sup>2</sup>C interface within t<sub>INIT</sub> time and be ready to receive the command from the host. The SPD5 Hub device is ready for operation after t<sub>INIT</sub> time.

Figure 3 Device Power Up Sequence

#### 2.2 Device Reset and Initialization

At power down (phase during which  $V_{DDSPD}$  input supply decreases continuously), as soon as  $V_{DDSPD}$  input supply drops below the  $V_{DDSPD}$ min, the SPD5 Hub device does not guarantee the operation.

On warm power cycling, the V<sub>DDSPD</sub> and V<sub>DDIO</sub> input supply must remain below V<sub>POFF</sub> for t<sub>POFF</sub> and must meet cold power on reset timing when restoring the power.

#### 2.3 Bus Clear

Rev.1.1 00

The SPD Hub device supports the following described Bus Clear feature in I<sup>2</sup>C mode only. Any attempt by host to perform I<sup>2</sup>C Bus clear on a target device in I3C mode may result in an active drive bus contention on the SDA data line.

There may be abnormal circumstances when the host abruptly stops clocking SCL while the target device is in the middle of outputting data for read operation. For these types of events, the SDA data line may appear as stuck low as the device is expecting to receive more clock pulses from the host. Eventually when the host has control of the SCL clock, the host may optionally clear the device that is stuck low on the SDA data line by sending continuous 18 clock pulses without driving the SDA data line followed by STOP operation. The device floats the SDA line within 18 clock pulses and returns to the Idle state. The device is ready for normal new transaction with Start condition.

#### 2.4 Bus Reset

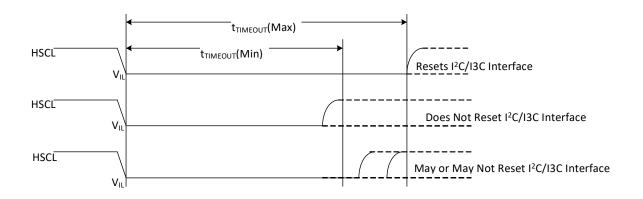

To prevent a malfunctioning device from locking up the I<sup>2</sup>C bus or I3C Basic bus, a bus reset mechanism is defined. It uses a timeout mechanism on HSCL as shown in **Figure 4** to force a device bus reset.

All devices (i.e., all SPD5 Hub devices and all local target devices behind the Hub) on I<sup>2</sup>C or I3C Basic bus reset simultaneously. Bus reset operation works in the same way regardless of whether the device is operating in I<sup>2</sup>C mode or I3C mode.

To guarantee the device resets the I<sup>2</sup>C or I3C Basic bus, the HSCL clock input Low time has to be greater than or equal to trimeout (Max).

The SPD5 Hub device will not reset I<sup>2</sup>C or I3C Basic bus if the HSCL clock input Low time is less than t<sub>TIMEOUT</sub> (Min). Besides, if the HSCL clock input Low time is between t<sub>TIMEOUT</sub> (Min) and t<sub>TIMEOUT</sub> (Max), the SPD5 Hub device may or may not reset the I<sup>2</sup>C / I3C Basic bus.

When RESET, the SPD5 Hub device takes the following actions:

- 1. Interface and any pending commands or transactions are cleared.

- 2. All internal register values are preserved unless noted otherwise in item # 3 below.

- Device returns to I<sup>2</sup>C mode of operation; Register MR18[7:5] resets to '000'; MR27[4] resets to '0'; MR52[1:0] resets to '00'.

- 4. Device does not re-sample HSA pin.

- 5. Device floats HSDA such that it gets pulled High by external/other pullup. The device pulls LSDA pin High.

- 6. Device treats bus resets as STOP operation.

Figure 4 I<sup>2</sup>C or I3C Basic Bus Reset

#### 3. Device Interface - IO Voltage Configuration

The SPD5 Hub device supports configurable Open Drain and Push Pull IO levels to accommodate broad range of DDR5 platform.

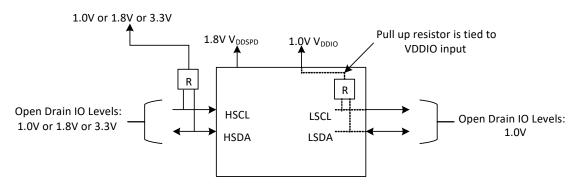

#### 3.1 Open Drain Interface

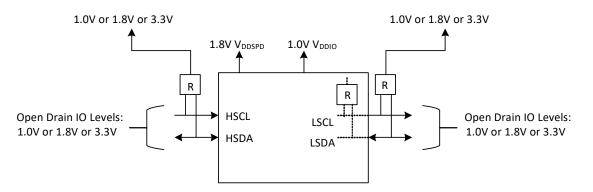

The SPD5 Hub device supports two configuration options for Open Drain interface for both Host side and Local side of the device. In this configuration, the SPD5 Hub device supports Open Drain IO levels on both Host and Local sides. However, the I/O voltage levels on Host side and Local side are independent and can be different. On Host side, the SPD5 device can support IO levels from 1.0 V to 3.3 V depending on the supply rail Host may have pulled up the resistor to. The host side pullup resistor should be hung externally on motherboard. On Local side, the LSCL level ranges from 1.0 V to 3.3 V depending on the supply rail Host may have pulled up the resistor to, and LSDA supports two I/O level options which depend on whether the pullup resistor selects the internal

(on die) or external (on board) mode.

When register MR14[5] is configured to '0', the internal (on die) pullup resistor mode is selected (See Figure 5). When register MR14[5] is configured to '1', the external (on board) pullup resistor mode is selected (See Figure 6).

Figure 5 Open Drain Interface (Internal Pullup Resistor)

Figure 6 Open Drain Interface (External Pullup Resistor)

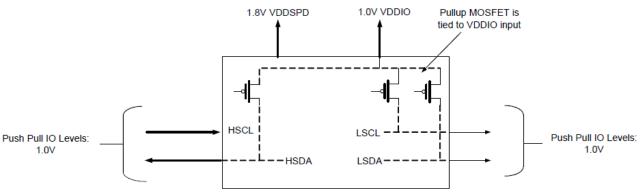

# 3. 2 Push Pull Interface

Rev.1.1 00

The Push Pull IO configuration is only supported when device is in I3C mode.

**Figure 7** below shows the SPD5 Hub device configuration options for Push Pull interface for both Host side and local side of the device.

In this configuration, the SPD5 Hub device supports Push Pull IO levels on both Host and Local sides.

Figure 7 Push Pull Interface

#### 3.3 IO Operation

The SPD5 Hub device supports configurable IO operation scheme of either Open Drain or Push-Pull on its Host side of the interface (HSCL and HSDA) and Local side of the interface (LSCL and LSDA).

Further, the SPD5 Hub device supports independent IO configuration on Host side and Local side of the interface. At power on, by default, the SPD5 Hub device comes up in legacy I<sup>2</sup>C mode of operation with Open Drain IO for both its Host side and Local side of the interface. The maximum speed is limited to 1 MHz and supported IO voltage levels are from 1.0 V to 3.3 V.

After power on, the host may put the SPD5 Hub device in I3C mode of operation.

In I3C Basic mode, the host may drive the HSCL clock input of the SPD5 device using either Push-Pull output driver or using the open-drain output driver. It is expected that for all DDR5 DIMM family environment, the host may always drive the HSCL clock input using a Push-Pull output driver.

To support in band interrupt, the SPD5 device supports dynamic switching between Open Drain mode and Push Pull mode on its HSDA and LSDA bus for various event. **Table 5** below describes the different mode of operation by the SPD5 device for each cycle.

| ,                                                |                 |                |

|--------------------------------------------------|-----------------|----------------|

| Supported Features                               | Open Drain Mode | Push Pull Mode |

| Start + Device Select Code                       | Yes             | No             |

| Start + 7'h7E IBI Header byte                    | Yes             | No             |

| Repeat Start + Device Select Code                | No              | Yes            |

| Repeat Start + 7'h7E IBI Header byte             | No              | Yes            |

| CCC Bytes                                        | No              | Yes            |

| Stop                                             | No              | Yes            |

| ACK/NACK Response                                | Yes             | No             |

| Command, Block Address, Address Operation        | No              | Yes            |

| Interrupt Request by Target + Device Select Code | Yes             | No             |

| IBI Payload                                      | No              | Yes            |

| Write Data, T-bit sequence                       | No              | Yes            |

| Read Data, T-bit sequence                        | No              | Yes            |

| PEC, T-bit sequence                              | No              | Yes            |

Table 5 SPD5 Hub Device Dynamic IO Operation Mode Switching

#### 4. Device Interface - Protocol

#### 4.1 I<sup>2</sup>C and I3C Protocol

This SPD5 Hub device supports both I<sup>2</sup>C and I3C interfaces. At power on, the device comes up in I<sup>2</sup>C mode of operation by default. It shall operate in I<sup>2</sup>C mode until I3C Basic mode is selected via SETAASA CCC command.

| Supported Features      | I <sup>2</sup> C mode | I3C mode |  |  |  |  |  |

|-------------------------|-----------------------|----------|--|--|--|--|--|

| Maximum operation speed | 1 MHz                 | 12.5 MHz |  |  |  |  |  |

| In-band interrupts      | No                    | Yes      |  |  |  |  |  |

| Bus reset               | Yes                   | Yes      |  |  |  |  |  |

| Parity check            | No <sup>*1</sup>      | Yes*2    |  |  |  |  |  |

| Packet Error check      | No                    | Yes*3    |  |  |  |  |  |

| Table 6 Supp | orted Features | in I <sup>2</sup> C and I3 | C Basic Modes |

|--------------|----------------|----------------------------|---------------|

|--------------|----------------|----------------------------|---------------|

\*1. Parity check is not supported except for the supported CCCs.

\*2. Parity check is always enabled by default in I3C Basic mode.

**\*3.** Packet error check is supported and by default is disabled in I3C Basic mode.

#### 4. 2 Switch from I<sup>2</sup>C Mode to I3C Basic Mode

By default, when the SPD5 Hub device first powers on, it operates in I<sup>2</sup>C mode. It shall operate in I<sup>2</sup>C mode until being put into I3C Basic mode via command.

In I<sup>2</sup>C mode, only 3 CCCs (DEVCTRL, SETHID and SETAASA) are allowed to be issued. All other CCCs are not supported. The I3C mode is selected by issuing SETAASA CCC. DEVCTRL & SETHID CCC must be issued first (if required) followed by SETAASA CCC.

When SETAASA CCC is registered by the SPD5 Hub device, it updates the register MR18[5] to '1'.

When SETHID CCC is registered by the SPD5 Hub device, it stops the 3-bit HID translation for the local Target device as explained in "4. 5. 2 Local Device Selection (Before SETHID CCC)".

#### 4.3 Switch from I3C Basic Mode to I<sup>2</sup>C Mode

The RSTDAA CCC command can put the SPD5 Hub device back in I2C mode from I3C Basic mode at any time. When RSTDAA CCC is registered by the SPD5 Hub device, the register MR18[5] is updated to '0'.

#### 4.4 7-bit Serial Address

The 7-bit serial address of the SPD5 Hub device and all local devices behind the Hub applies to both I<sup>2</sup>C mode and I3C Basic mode of operation identically.

The host identifier value (HID) is merged with the SPD5 Hub Device Type ID or the local Device Type ID to establish the 7-bit address for the device on the I<sup>2</sup>C or I3C Basic bus as shown in **Table 7**.

The SPD5 Hub Device Type ID is a 4-bit binary value of 1010b. The SPD5 Hub device samples the status of the HSA pin on power up. The sampled status of the HSA pin determines the unique host ID (HID) of the device. For example, if the value sensed on HSA pin identifier is 2 (010b), then the unique 7-bit address of this device is 1010 010b.

Each local device behind the SPD5 Hub device has a unique 4-bit local device ID (LID) code. For example, the PMIC local device type ID is 1001b. The 3 HID bits of the target local device type has a default value of '111'. Thus 7-bit address of the local device, e.g., PMIC, is 1001 111b.

| Table 7 7-bit Address of the SFD5 Hub Device and Local Devices |                |        |         |               |        |        |        |            |

|----------------------------------------------------------------|----------------|--------|---------|---------------|--------|--------|--------|------------|

| Catagoni                                                       | Bit 7          | Bit 6  | Bit 5   | Bit 4         | Bit 3  | Bit 2  | Bit 1  | Bit 0      |

| Category                                                       | Device Type ID |        |         | Host ID (HID) |        |        | R/W    |            |

| SPD5 Hub Device                                                | 1              | 0      | 1       | 0             | HID[2] | HID[1] | HID[0] | Read/Write |

| Local Device behind the Hub                                    | Local          | Device | Type ID | (LID)         | 1      | 1      | 1      | Read/Write |

Table 7

7-bit Address of the SPD5 Hub Device and Local Devices

#### 4. 5 Device Selection on I<sup>2</sup>C / I3C Bus

#### 4. 5. 1 SPD5 Hub Device Selection

Up to eight SPD Hub devices can be connected on a single I<sup>2</sup>C/I3C bus as shown in **Table 8**. The host can access any SPD5 Hub device in both I<sup>2</sup>C mode and I3C Basic mode. The last 3 bits of the 7-bit address represent the HID bits.

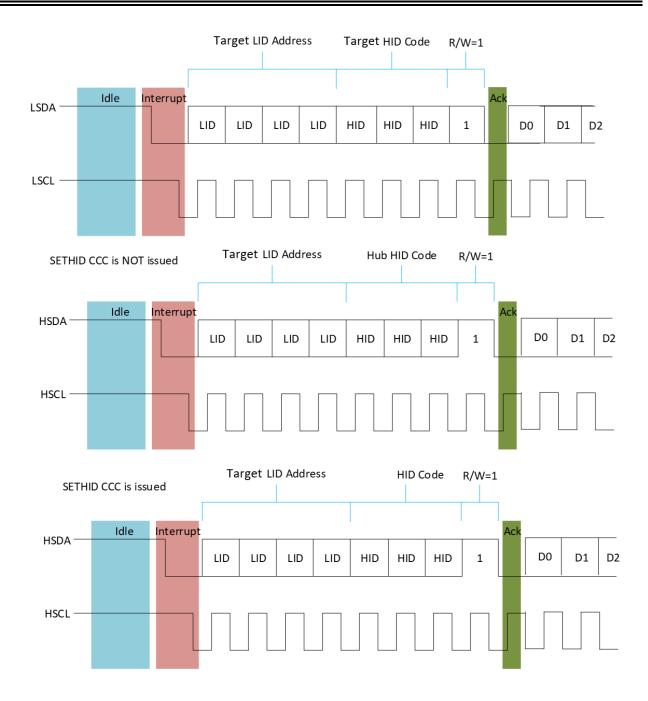

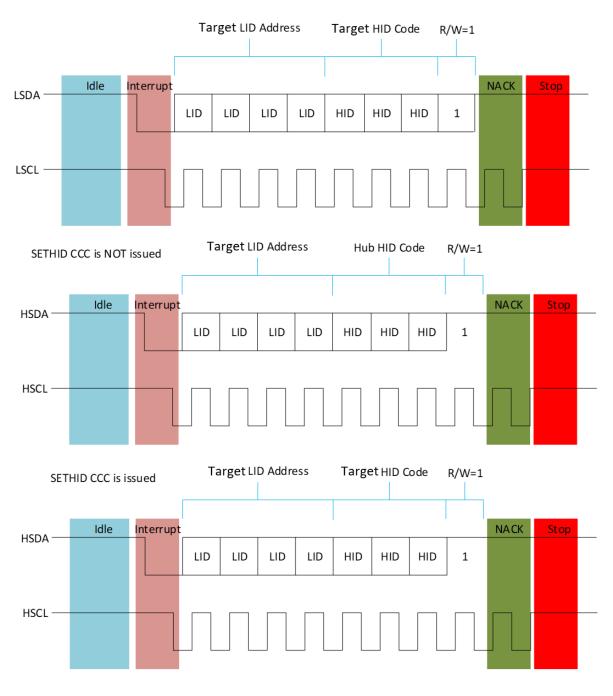

#### 4. 5. 2 Local Device Selection (Before SETHID CCC)

Under I<sup>2</sup>C Mode (Prior to Host issuing SETHID CCC) the host can access any local device behind the SPD5 Hub device. **Table 8** shows an example of four different local device address codes behind the SPD5 Hub device on each DIMM.

The SPD5 Hub device monitors the LID code coming from the host. When it detects the host access is for the Target device, it compares the last 3 bits of the HID information coming from the host against its own unique HID code that it has stored at power on. It compares each 3 bits one at a time. If there is a match, the SPD5 Hub device substitutes that bit with '1' and forwards it to the local device interface. If there is a mismatch, the SPD5 Hub device substitutes that bit with '0' and forwards it to the local device interface. As a result, only the targeted local device will see its last three HID bits as '111' and all non-targeted local devices will see its last three HID bits as anything other than '111' which is not a valid code.

|                | 7-bit Address |        |                          |     |      |         |         |     |      |     |

|----------------|---------------|--------|--------------------------|-----|------|---------|---------|-----|------|-----|

| Host Access to | SF            | PD     |                          |     |      | Local E | Devices |     |      |     |

| HOST ACCESS TO | Hub D         | )evice | RC                       | D   | PM   | /IC     | Т       | 50  | т    | S1  |

|                | LID           | HID    | LID                      | HID | LID  | HID     | LID     | HID | LID  | HID |

| DIMM0          |               | 000    |                          | 000 |      | 000     |         | 000 |      | 000 |

| DIMM1          |               | 001    |                          | 001 |      | 001     |         | 001 |      | 001 |

| DIMM2          |               | 010    | 1011                     | 010 |      | 010     |         | 010 | 0110 | 010 |

| DIMM3          | 1010          | 011    |                          | 011 | 1001 | 011     | 0010    | 011 |      | 011 |

| DIMM4          | 1010          | 100    | 1011                     | 100 | 1001 | 100     | 0010    | 100 |      | 100 |

| DIMM5          |               | 101    | 100<br>101<br>110<br>111 |     | 101  |         | 101     |     | 101  |     |

| DIMM6          |               | 110    |                          | 110 |      | 110     |         | 110 |      | 110 |

| DIMM7          |               | 111    |                          | 111 |      | 111     |         | 111 |      | 111 |

#### Table 8 Device Selection on I<sup>2</sup>C / I3C Bus (Multiple Devices)

There are two exceptions where S-34HTS08AB does not substitute its own HID code when it forwards it to the Target interface:

- 1. Host issues Start followed by 7'h7E with W=0 (or Host issues Start followed by 0xFC).

- 2. After the SPD5 Hub device executes SETHID CCC command that Host issues.

**Figure 8** gives an example of Host accessing Local RCD Device on DIMM0. The figure shows Host sends 7-bit address '1011 000'. Each SPD5 Hub device receives this address and then forwards the first four bits of binary address '1011' (LID) on the local device interface. Each SPD5 Hub device compares the last 3 bits of binary address '000' from the host against its own unique HID code and substitutes the bit on the local device interface.

# DDR5 SPD EEPROM WITH HUB BUILT-IN TEMPERATURE SENSOR S-34HTS08AB

Rev.1.1\_00

|            |          |    | DCD                    |    | DMICO                  |    | DN4IC1                 |    | DNALCO                 |    | тсо                    |    | TC 1     |    |

|------------|----------|----|------------------------|----|------------------------|----|------------------------|----|------------------------|----|------------------------|----|----------|----|

|            | Hub SPD  | 50 | RCD                    |    | PMIC0                  | 45 | PMIC1                  | 47 | PMIC2                  | 67 | TS0                    | 47 | TS1      | 27 |

| DIMMO      | 101 0000 | 50 | 101 1111               | 5F | 100 1111               | 4F | 100 0111               | 47 | 110 0111               | 67 | 001 0111               | 17 | 011 0111 | 37 |

| Host Sends | 101 1000 | 58 |                        |    |                        |    |                        |    | <u> </u>               |    | <u> </u>               |    |          |    |

| Hub Sends  |          |    | 101 1111               | 5F | 101 1111 | 5F |

|            |          |    |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| DIMM1      | 101 0001 | 51 | 101 1111               | 5F | 100 1111               | 4F | 100 0111               | 47 | 110 0111               | 67 | 001 0111               | 17 | 011 0111 | 37 |

| Host Sends | 101 1000 | 58 |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| Hub Sends  |          |    | 101 1110               | 5E | 101 1110 | 5E |

|            |          |    |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| DIMM2      | 101 0010 | 52 | 101 1 <mark>111</mark> | 5F | 100 1 <mark>111</mark> | 4F | 100 0 <mark>111</mark> | 47 | 110 0 <mark>111</mark> | 67 | 001 0 <mark>111</mark> | 17 | 011 0111 | 37 |

| Host Sends | 101 1000 | 58 |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| Hub Sends  | -        |    | 101 1101               | 5D | 101 1101 | 5D |

|            |          |    |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| DIMM3      | 101 0011 | 53 | 101 1 <mark>111</mark> | 5F | 100 1111               | 4F | 100 0 <b>111</b>       | 47 | 110 0 <b>111</b>       | 67 | 001 0 <mark>111</mark> | 17 | 011 0111 | 37 |

| Host Sends | 101 1000 | 58 |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| Hub Sends  | L        |    | 101 1100               | 5C | 101 1100 | 5C |

|            |          |    |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| DIMM4      | 101 0100 | 54 | 101 1 <mark>111</mark> | 5F | 100 1111               | 4F | 100 0111               | 47 | 110 0 <b>111</b>       | 67 | 001 0111               | 17 | 011 0111 | 37 |

| Host Sends | 101 1000 | 58 |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| Hub Sends  | L        |    | 101 1011               | 5B | 101 1011 | 5B |

|            |          |    |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| DIMM5      | 101 0101 | 55 | 101 1111               | 5F | 100 1111               | 4F | 100 0111               | 47 | 110 0111               | 67 | 001 0111               | 17 | 011 0111 | 37 |

| Host Sends | 101 1000 | 58 |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| Hub Sends  |          |    | 101 1010               | 5A | 101 1010 | 5A |

|            |          |    |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| DIMM6      | 101 0110 | 56 | 101 1111               | 5F | 100 1111               | 4F | 100 0111               | 47 | 110 0111               | 67 | 001 0111               | 17 | 011 0111 | 37 |

| Host Sends | 101 1000 | 58 |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| Hub Sends  |          |    | 101 1001               | 59 | 101 1001               | 59 | 101 1001               | 59 | 101 1001               | 59 | 101 1001               | 59 | 101 1001 | 59 |

|            |          |    | 101 1001               | 55 | 101 1001               | 35 | 101 1001               | 55 | 101 1001               | 55 | 101 1001               | 55 | 101 1001 | 33 |

| DIMM7      | 101 0111 | 57 | 101 1111               | 5F | 100 1111               | 4F | 100 0111               | 47 | 110 0111               | 67 | 001 0111               | 17 | 011 0111 | 37 |

| Host Sends | 101 1000 | 58 |                        |    |                        |    |                        |    |                        |    |                        |    |          |    |

| Hub Sends  | 101 1000 | 50 | 101 1000               | 58 | 101 1000               | 58 | 101 1000               | 58 | 101 1000               | 58 | 101 1000               | 58 | 101 1000 | 58 |

|            |          |    | 101 1000               | 20 | 101 1000               | 20 | 101 1000               | 58 | 101 1000               | 58 | 101 1000               | 28 | 101 1000 | 28 |

#### Figure 8 Example: Host Accessing Local Device (RCD) on DIMM0

#### 4. 5. 3 Local Device Selection (After SETHID CCC)

When SETHID CCC is registered by the SPD5 Hub device, it stops the 3-bit HID translation for the local Target device. After Host sends SETHID CCC, the Host still accesses all the Target devices behind the SPD5 Hub device as shown in **Table 8**. There is no change in how Host access the SPD5 Hub device and all local Target devices behind the SPD Hub device before or after SETHID CCC.

#### 4.6 I<sup>2</sup>C Target Protocol - Host to SPD5 Hub Device

Rev.1.1 00

The SPD5 Hub device behaves as a Target device in the I<sup>2</sup>C Bus protocol, with all operations synchronized by the serial clock. Read and Write operations are initiated by a START condition, generated by the Host. The START condition is followed by a 7-bit serial address (as described in **Table 7**), then a write or read bit (R/W) and terminated by an acknowledge bit (ACK). The SPD5 Hub device may NACK when it is busy performing internal write operation to EEPROM.

To allow compatibility with legacy I<sup>2</sup>C host controller, the SPD5 Hub device offers two ways to address 1024 bytes of non-volatile memory when it is operating in I<sup>2</sup>C mode only. 1 byte addressing mode is by default to access the first 128 bytes of the main array. Register MR11[2:0] is a page pointer register, which is used to configure which page to access and covers the entire 1024 bytes of the main array.

Alternatively, there is another way to access the main array, i.e., 2 bytes addressing mode. At initial power on, when register MR11[3] is set to '1', the 2 bytes addressing mode is selected to address the entire memory and hence the host is not required to go through page selection to address the entire non-volatile memory.

Moreover, 1 byte addressing mode is only applicable to the SPD5 Hub device and not applicable to the local device such as PMIC or TS or RCD device in I<sup>2</sup>C mode.

The SPD5 Hub device volatile register space does not require the page selection process as all volatile registers are within the first 128 bytes.

#### 4. 6. 1 Write Operation – Data Packet

The MemReg bit determines if the target of the transaction is an NVM location (MemReg = '1') or an internal register (MemReg = '0'). When MemReg = '0', there is no concept of "Block Address"; Block Address bits are treated simply as Upper Address bits.

**Table 9** and **Table 10** list the write command data packet format when register MR11[3] = 0 and MR11[3] = 1 respectively.

|                       | Table 9 Write Command Data Packet, MR11[3] = 0 |              |                            |                           |  |  |   |       |     |      |  |  |  |

|-----------------------|------------------------------------------------|--------------|----------------------------|---------------------------|--|--|---|-------|-----|------|--|--|--|

| Start                 | Bit 7                                          | Bit 6        | Bit 5                      | Bit 5 Bit 4 Bit 3 Bit 2 E |  |  |   | Bit 0 | A/N | Stop |  |  |  |

| S or Sr <sup>*1</sup> | 1                                              | 0            | 0 1 0 HID W=0 A            |                           |  |  | Α |       |     |      |  |  |  |

|                       | MemReg                                         | Blk Addr [0] | Blk Addr [0] Address [5:0] |                           |  |  |   |       |     |      |  |  |  |

|                       |                                                | Data         |                            |                           |  |  |   |       |     |      |  |  |  |

|                       |                                                |              |                            |                           |  |  |   |       |     |      |  |  |  |

|                       |                                                |              | Α                          | Sr or P                   |  |  |   |       |     |      |  |  |  |

### Table 9 Write Command Data Packet, MR11[3] = 0

| Start                 | Bit 7  | Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit |           |                      |  |  | Bit 0 | A/N | Stop |         |  |

|-----------------------|--------|-----------------------------------------|-----------|----------------------|--|--|-------|-----|------|---------|--|

| S or Sr <sup>*1</sup> | 1      | 0                                       | 0 1 0 HID |                      |  |  | W=0   | Α   |      |         |  |

|                       | MemReg | MemReg Blk Addr [0] Address [5:0]       |           |                      |  |  |       |     | Α    |         |  |

|                       | 0      | 0                                       | 0         | 0 0 Blk Addr [4:1]*2 |  |  |       |     |      |         |  |

|                       |        | Data                                    |           |                      |  |  |       |     | Α    |         |  |

|                       |        |                                         |           |                      |  |  |       |     |      |         |  |

|                       |        | Data                                    |           |                      |  |  |       |     |      | Sr or P |  |

|                       |        |                                         |           |                      |  |  |       | A   |      |         |  |

- \*1. In I<sup>2</sup>C mode, Start or Repeat Start operation followed by 7'h7E command is only allowed for the purpose of issuing CCCs that are allowed in I<sup>2</sup>C mode. Any other operation including another Repeat Start is considered as an illegal operation.

- \*2. The memory size of SPD5 Hub device is limited to 1024 Bytes. SPD5 Hub device ignores Blk Addr [4] bit.

#### 4. 6. 2 Read Operation – Data Packet

The MemReg bit determines if the target of the transaction is an NVM location (MemReg = '1') or an internal register (MemReg = '0'). When MemReg = '0', there is no concept of "Block Address"; Block Address bits are treated simply as Upper Address bits.

Table 11 and Table 12 show the read command data packet when MR11[3] = 0 and MR11[3] = 1 respectively.

|                       | Table 11         Read Command Data Packet, MR11[3] = 0 |              |           |             |          |       |       |       |     |      |  |  |  |

|-----------------------|--------------------------------------------------------|--------------|-----------|-------------|----------|-------|-------|-------|-----|------|--|--|--|

| Start                 | Bit 7                                                  | Bit 6        | Bit 5     | Bit 4       | Bit 3    | Bit 2 | Bit 1 | Bit 0 | A/N | Stop |  |  |  |

| S or Sr <sup>*1</sup> | 1                                                      | 0            | 1 0 HID W |             |          |       |       |       | Α   |      |  |  |  |

|                       | MemReg                                                 | Blk Addr [0] |           |             | A<br>A*2 |       |       |       |     |      |  |  |  |

| Sr                    | 1                                                      | 0            | 1         | 1 0 HID R=1 |          |       |       |       |     |      |  |  |  |

|                       |                                                        |              | Data      |             |          |       |       |       |     |      |  |  |  |

|                       |                                                        |              |           |             |          |       |       |       |     |      |  |  |  |

|                       |                                                        | Data         |           |             |          |       |       |       |     |      |  |  |  |

## d Data Daakat MD44[2]

#### Table 12 Read Command Data Packet, MR11[3] = 1

| Start                 | Bit 7  | Bit 6                    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | A/N | Stop    |

|-----------------------|--------|--------------------------|-------|-------|-------|-------|-------|-------|-----|---------|

| S or Sr <sup>*1</sup> | 1      | 0                        | 1     | 0     | HID   |       |       | W=0   | Α   |         |

|                       | MemReg |                          |       |       |       |       |       |       | Α   |         |

|                       | 0      | 0 0 0 0 Blk Addr [4:1]*3 |       |       |       |       |       | Α     |     |         |

| Sr                    | 1      | 0                        | 1     | 0     | R=1   | A*2   |       |       |     |         |

|                       |        |                          |       | Data  |       |       |       |       | Α   |         |

|                       |        |                          |       |       |       |       |       |       |     |         |

|                       |        | Data                     |       |       |       |       |       |       |     | Sr or P |

- \*1. In I<sup>2</sup>C mode, Start or Repeat Start operation followed by 7'h7E command is only allowed for the purpose of issuing CCCs that are allowed in I<sup>2</sup>C mode. Any other operation including another Repeat Start is considered as an illegal operation.

- \*2. If Target device NACKs during Repeat Start for any reason, the host may re-try Repeat Start again. The host can do the Repeat Start as many times it may desire. The device may eventually ACK.

- The memory size of SPD5 Hub device is limited to 1024 Bytes. SPD5 Hub device ignores Blk Addr [4] bit. \*3.

#### 4. 6. 3 Default Read Address Pointer Mode

During the normal operation of DDR5 DIMM, the host periodically may poll critical information from the same location. To help improve the efficiency of the I<sup>2</sup>C bus protocol, the SPD5 Hub device offers a default read address pointer mode so that whenever the Hub device sees the STOP operation on its HSCL and HSDA bus, its read address pointer is always reset to default address.

The default read pointer address mode is enabled through register MR18[4] and the default starting address for read operation is selectable through register MR18[3:2]. The starting address for default read pointer address mode should be reset by Stop to the address selected through register MR18[3:2]. Compared to the standard read command data packet (shown as Table 12), the default read address pointer mode reduces the packet overhead by 3 bytes. The host typically enables this mode when the normal operation of the DDR5 DIMM begins. The default read address pointer mode is only applicable to the volatile register space.

| Table 13 | Read Command Data Packet with Default Address Pointer Mode |

|----------|------------------------------------------------------------|

|          |                                                            |

| Start   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 0 | A/N | Stop |   |  |  |

|---------|-------|-------|-------|-------|---------|-------|-----|------|---|--|--|

| S or Sr | 1     | 0     | 1     | 0     |         | HID   |     | R=1  | Α |  |  |

|         |       | Data  |       |       |         |       |     |      |   |  |  |

|         |       |       |       |       |         |       |     |      |   |  |  |

|         |       |       |       | Ν     | Sr or P |       |     |      |   |  |  |

#### Rev.1.1\_00

#### 4.7 I<sup>2</sup>C Target Protocol - Host to Local Device through SPD5 Hub Device

The tables below list the write and read command data packets of some typical Local Devices such as TS, PMIC, and RCD behind the SPD5 Hub device. The SPD5 Hub device simply treats all the inputs as Data and just transmits the Data to the target Local Device.

#### 4. 7. 1 Write Operation – Data Packet

The SPD5 Hub device does not check for the PEC for its Local Devices.

| -                     |         |            |           |         |       |       |       |     |      |         |  |  |

|-----------------------|---------|------------|-----------|---------|-------|-------|-------|-----|------|---------|--|--|

| Start                 | Bit 7   | Bit 6      | Bit 4     | Bit 3   | Bit 2 | Bit 1 | Bit 0 | A/N | Stop |         |  |  |

| S or Sr <sup>*1</sup> | 0010(TS | 5), 1001(P | MIC), 101 | 11(RCD) |       | HID   |       | W=0 | Α    |         |  |  |

|                       |         | Data       |           |         |       |       |       |     | Α    |         |  |  |

|                       |         |            |           |         |       |       |       |     | Α    |         |  |  |

|                       |         | Data       |           |         |       |       |       |     | Α    | Sr or P |  |  |

#### Table 14 Write Command Data Packet - Local Device

\*1. In I<sup>2</sup>C mode, Start or Repeat Start operation followed by 7'h7E command is only allowed for the purpose of issuing CCCs that are allowed in I<sup>2</sup>C mode. Any other operation including another Repeat Start is considered as an illegal operation.

#### 4.7.2 Read Operation – Data Packet

#### Table 15 Read Command Data Packet - Local Device TS or PMIC Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 A/N Start Stop S or Sr<sup>\*1</sup> 0010(TS), 1001(PMIC) HID W=0 А Data (Address [7:0]) A R=1 A\*2 0010(TS), 1001(PMIC) Sr HID A Data Data А A Data Α Sr or P

\*1. In I<sup>2</sup>C mode, Start or Repeat Start operation followed by 7'h7E with W=0 is only allowed for the purpose of issuing CCCs that are allowed in I<sup>2</sup>C mode. Any other operation including another Repeat Start is considered as an illegal operation.

\*2. If Target device NACKs during Repeat Start for any reason, the host may re-try Repeat Start again. The host can do the Repeat Start as many times it may desire.

When Host makes any read request to the RCD device, the RCD protocol has PEC check for the RCD address information as well as data returned by the RCD. The SPD5 Hub simply treats the PEC information as data byte like any other data byte. The SPD5 Hub device does not check for the PEC. The RCD device requires valid stable input clock (DCK\_t, DCK\_c), Reset\_n and DCS\_n to allow any read or write access on its I<sup>2</sup>C interface.

#### Table 16 Read Command Data Packet - Local Device RCD (PEC Disabled, Legacy Format)

|                       |                        |                                     |                      |                      |          |       | - (: = ) |       |     | guogitor |

|-----------------------|------------------------|-------------------------------------|----------------------|----------------------|----------|-------|----------|-------|-----|----------|

| Start                 | Bit 7                  | Bit 6                               | Bit 5                | Bit 4                | Bit 3    | Bit 2 | Bit 1    | Bit 0 | A/N | Stop     |

| S or Sr <sup>*1</sup> | 1                      | 0                                   | 1                    | 1                    |          | W=0   | Α        |       |     |          |

|                       |                        | Data (I <sup>2</sup> C Bus Command) |                      |                      |          |       |          |       |     |          |

|                       |                        | Data (Byte Count=4)                 |                      |                      |          |       |          |       |     |          |

|                       | Data (Reserved;0x00)   |                                     |                      |                      |          |       |          |       | Α   |          |

|                       | Data (Dev/Channel Num) |                                     |                      |                      |          |       |          |       | Α   |          |

|                       | Data (Page_Num [7:0])  |                                     |                      |                      |          |       |          |       | Α   |          |

|                       |                        |                                     | Data (Reg_Num [7:0]) |                      |          |       |          |       |     | Р        |

| S                     | 1                      | 0                                   | 1 1 HID W=0          |                      |          |       |          |       |     |          |

|                       |                        |                                     | Data                 | (I <sup>2</sup> C Bu | s Comn   | nand) |          |       | Α   |          |

| Sr                    | 1                      | 0                                   | 1                    | 1                    |          | HID   |          | R=1   | A*2 |          |

|                       |                        |                                     | D                    | ata (By              | te Coun  | t)    |          |       | Α   |          |

|                       |                        | Data (Status)                       |                      |                      |          |       |          |       |     |          |

|                       | Data (Rd Data [31:24]) |                                     |                      |                      |          |       |          |       | Α   |          |

|                       | Data (Rd Data [23:16]) |                                     |                      |                      |          |       |          |       |     |          |

|                       | Data (Rd Data [15:8])  |                                     |                      |                      |          |       |          |       |     |          |

|                       |                        |                                     | Da                   | ta (Rd I             | Data [7: | 0])   |          |       | Α   | Sr or P  |

| Start    | Bit            | 7                                   | Bit 6 | Bit 5 | Bit 4                | Bit 3    | Bit 2 | Bit 1 | Bit 0 | A/N | Stop    |

|----------|----------------|-------------------------------------|-------|-------|----------------------|----------|-------|-------|-------|-----|---------|

| S or Sr* | <sup>1</sup> 1 |                                     | 0     | 1     | 1                    |          | HID   |       | W=0   | Α   |         |

|          |                | Data (I <sup>2</sup> C Bus Command) |       |       |                      |          |       |       |       |     |         |

|          |                |                                     |       | Da    | ita (Byte            | e Count= | =4)   |       |       | Α   |         |

|          |                |                                     |       | Dat   | a (Rese              | erved;0x | :00)  |       |       | Α   |         |

|          |                |                                     |       | Data  | (Dev/C               | hannel l | Num)  |       |       | Α   |         |

|          |                |                                     |       | Data  | a (Page              | _Num [7  | 7:0]) |       |       | Α   |         |

|          |                |                                     |       | Dat   | a (Reg_              | _Num [7  | [:0]  |       |       | Α   |         |

|          |                | Data (PEC [7:0])                    |       |       |                      |          |       |       |       | Α   | Р       |

| S        | 1              |                                     |       |       |                      |          |       |       |       | Α   |         |

|          |                |                                     |       | Data  | (I <sup>2</sup> C Bu | s Comn   | nand) |       |       | Α   |         |

| Sr       | 1              |                                     | 0     | 1     | 1                    |          | HID   |       | R=1   | Α   |         |

|          |                |                                     |       | D     | ata (By              | te Coun  | t)    |       |       | Α   |         |

|          |                |                                     |       |       | Data (S              | Status)  |       |       |       | Α   |         |

|          |                | Data (Rd Data [31:24])              |       |       |                      |          |       |       |       | Α   |         |

|          |                | Data (Rd Data [23:16])              |       |       |                      |          |       |       |       |     |         |

|          |                | Data (Rd Data [15:8])               |       |       |                      |          |       |       |       |     |         |

|          |                | Data (Rd Data [7:0])                |       |       |                      |          |       |       |       |     |         |

|          |                | Data (PEC [7:0])                    |       |       |                      |          |       |       |       |     | Sr or P |

# Table 17 Read Command Data Packet - Local Device RCD (PEC Enabled, Legacy Format) Start Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 A/N Stop

Table 18 Read Command Data Packet - Local Device RCD (PEC Disabled, Optimized Format)

| Start                 | Bit 7                  | Bit 6         | Bit 5 | Bit 4                | Bit 3    | Bit 2 | Bit 1 | Bit 0 | A/N | Stop    |

|-----------------------|------------------------|---------------|-------|----------------------|----------|-------|-------|-------|-----|---------|

| S or Sr <sup>*1</sup> | 1                      | 0             | 1     | 1                    |          | HID   | W=0   | Α     |     |         |

|                       |                        |               | Data  | (I <sup>2</sup> C Bu | s Comn   | nand) |       |       | Α   |         |

|                       |                        |               | Da    | ta (Byte             | e Count  | =4)   |       |       | Α   |         |

|                       |                        |               | Dat   | a (Rese              | erved;0x | (00)  |       |       | Α   |         |

|                       |                        |               | Data  | (Dev/C               | hannel   | Num)  |       |       | Α   |         |

|                       |                        |               | Data  | a (Page              | _Num []  | 7:0]) |       |       | Α   |         |

|                       |                        |               | Dat   | a (Reg_              | Num [7   | ':0]) |       |       | Α   |         |

| Sr                    | 1                      | 0             | 1     | 1                    |          | HID   |       | R=1   | A*2 |         |

|                       |                        |               | D     | ata (By              | te Coun  | it)   |       |       | Α   |         |

|                       |                        | Data (Status) |       |                      |          |       |       |       | Α   |         |

|                       |                        |               | Dat   | Α                    |          |       |       |       |     |         |

|                       | Data (Rd Data [23:16]) |               |       |                      |          |       |       |       |     |         |

|                       | Data (Rd Data [15:8])  |               |       |                      |          |       |       |       |     |         |

|                       |                        |               | Da    | ita (Rd I            | Data [7: | 0])   |       |       | Α   | Sr or P |

- \*1. In I<sup>2</sup>C mode, Start or Repeat Start operation followed by 7'h7E with W=0 is only allowed for the purpose of issuing CCCs that are allowed in I<sup>2</sup>C mode. Any other operation including another Repeat Start is considered as an illegal operation.

- \*2. If Target device NACKs during Repeat Start for any reason, the host may re-try Repeat Start again. The host can do the Repeat Start as many times it may desire.

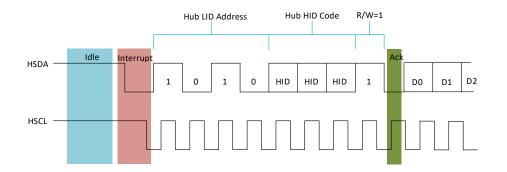

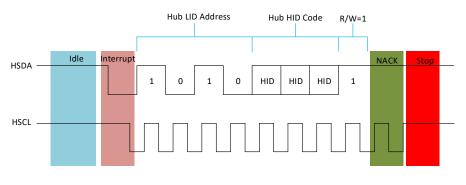

#### 4.8 I3C Basic Target Protocol - Host to SPD5 Hub Device

Rev.1.1 00

The SPD5 Hub device behaves as a Target device in the I3C Basic mode, with all operations synchronized by the serial clock. Read and Write operations are initiated by a START condition, generated by the Host. The START condition is followed by a 7-bit serial address (as described in Table 7), then a write or read bit (R/W) and terminated by an acknowledge bit (ACK). The SPD5 Hub device may NACK when it is busy performing internal write operation to EEPROM.

The Packet Error Code (PEC) function is disabled by default when the SPD5 Hub device is put in I3C Basic mode. The host may optionally enable this function through register MR18[7] or DEVCTRL CCC command. If PEC is enabled, the PEC field is appended at the end of all transactions and the host must complete the burst length as indicated in CMD field. In other words, the host must not interrupt the burst length pre-maturely for Write or Read operation.

The MemReg bit determines if the target of the transaction is an NVM location (MemReg = '1') or an internal register (MemReg = '0'). When MemReg = '0', there is no concept of 'Block Address'; Block Address bits are treated simply as Upper Address bits.

The 'T' bit in below table carries Parity information from the Host for each byte indicating Continuous ('1') or Stop (0') whether it is transmitting the last byte or not, prior to Repeated START. After Repeated START, 'T' bit carries information from the SPD5 Hub device.

The host may optionally allow the SPD5 Hub device to request IBI. For this case, the transactions to the SPD5 Hub device begin with the I3C Basic host issuing a START condition followed by 0xFC command. If the Hub device has a pending IBI, it transmits its 7-bit device select code followed by R=1. If no pending IBI, there is no action taken by the SPD5 Hub device.

Below tables show the I3C Basic bus write/read command data packet with optional IBI header for PEC disabled and PEC enabled cases respectively. PEC calculation does not include IBI header byte (7'h7E followed by W=0).

| Table 19 Write Command Data Packet - PEC Disabled |        |                          |       |       |           |          |       |      |   |                       |

|---------------------------------------------------|--------|--------------------------|-------|-------|-----------|----------|-------|------|---|-----------------------|

| Start                                             | Bit 7  | Bit 6                    | Bit 5 | Bit 4 | Bit 3     | Bit 0    | A/N/T | Stop |   |                       |

| S or Sr <sup>*1</sup>                             | 1      | 0                        | 1     | 0     | A*1,*2,*3 |          |       |      |   |                       |

|                                                   | MemReg | Blk Addr [0]             |       |       | Addres    | ss [5:0] |       |      | Т |                       |

|                                                   |        | CMD W=0 Blk Addr [4:1]*4 |       |       |           |          |       |      |   |                       |

|                                                   | Data   |                          |       |       |           |          |       |      |   |                       |

|                                                   |        |                          |       |       |           |          |       |      |   |                       |

|                                                   | Data   |                          |       |       |           |          |       |      |   | Sr <sup>∗₅</sup> or P |

Table 10 Write Command Date Backet BEC Disabled

#### 4.8.1 Write Operation – Data Packet

| Data |

|------|

|      |

#### Table 20 Write Command Data Packet - PEC Enabled

| Start                 | Bit 7  | Bit 6        | Bit 5                | Bit 4 | 4 Bit 3 Bit 2 Bit 1 Bit 0 |         |  |           | A/N/T | Stop                  |

|-----------------------|--------|--------------|----------------------|-------|---------------------------|---------|--|-----------|-------|-----------------------|

| S or Sr <sup>*1</sup> | 1      | 0            | 1                    | 0     |                           | HID     |  | A*1,*2,*3 |       |                       |

|                       | MemReg | Blk Addr [0] |                      |       | Addres                    | s [5:0] |  |           | Т     |                       |

|                       |        | CMD          | W=0 Blk Addr [4:1]*4 |       |                           |         |  |           |       |                       |

|                       | Data   |              |                      |       |                           |         |  |           | Т     |                       |

|                       |        |              |                      |       |                           |         |  |           | Т     |                       |

|                       | Data   |              |                      |       |                           |         |  | Т         |       |                       |

|                       | PEC    |              |                      |       |                           |         |  |           | Т     | Sr <sup>∗₅</sup> or P |

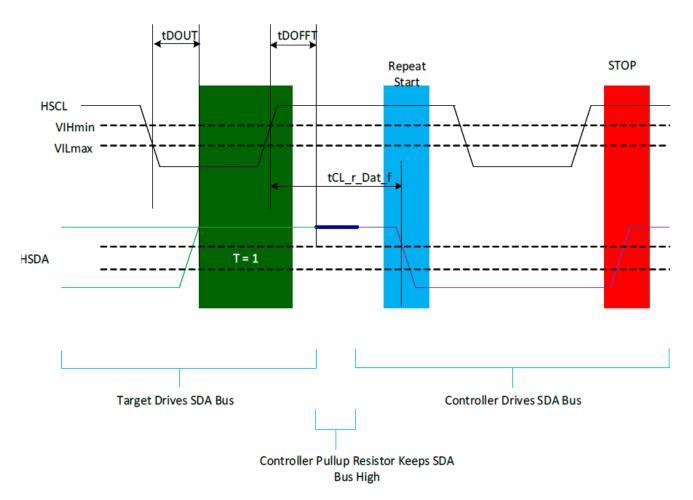

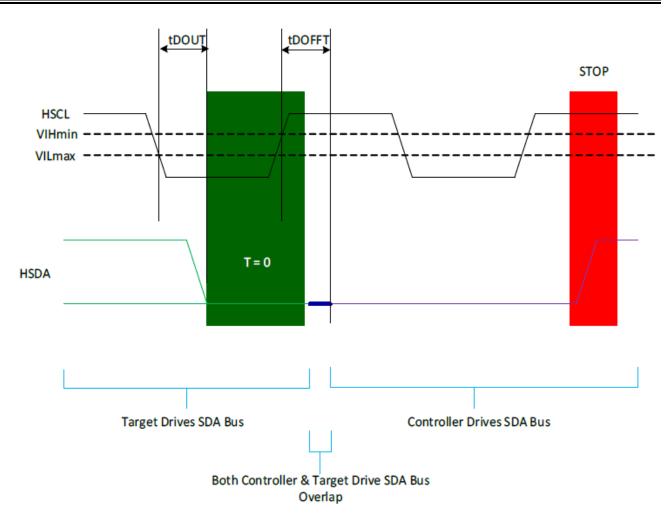

- \*1. See Figure 14 for how the transition occurs from Target Open Drain (ACK) to Host Push Pull Operation (MemReg bit).

- \*2. The SPD5 Hub NACKs if there is a parity error in a previous transaction when host performs consecutive transactions with Repeat Start.

- \*3. The SPD5 Hub device does not check for parity error in subsequent bytes when it determines 7-bit device select code issued by the host does not match with its own device code. The SPD5 Hub device ignores the entire packet until STOP or next Repeat Start operation.

- \*4. The memory size of SPD5 Hub device is limited to 1024 Bytes. SPD5 Hub device ignores Blk Addr [4] bit.

- \*5. Repeat Start or Repeat Start with 7'h7E.

## ABLIC Inc.

| Start         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         A/N/T         Stop           S         1         1         1         1         1         0         W=0 $A^{*1,*3}$ Sr         1         0         1         0         HID         W=0 $A^{*2,*3,*4}$ MemReg         Blk Addr [0]         Address [5:0]         T           CMD         W=0         Blk Addr [4:1]*5         T           Data | Table 21 White Command Data Packet with Ibi Header - PEC Disabled |        |              |                                     |     |        |         |                        |     |           |                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------|--------------|-------------------------------------|-----|--------|---------|------------------------|-----|-----------|-----------------------|

| Sr         1         0         1         0         HID         W=0         A*2.*3.*4           MemReg         Blk Addr [0]         Address [5:0]         T           CMD         W=0         Blk Addr [4:1]*5         T           Data         T         T                                                                                                                                                                                                                 | Start                                                             | Bit 7  | Bit 6        | Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |     |        |         |                        |     | A/N/T     | Stop                  |

| MemReg         Blk Addr [0]         Address [5:0]         T           CMD         W=0         Blk Addr [4:1]*5         T           Data         T         T                                                                                                                                                                                                                                                                                                                | S                                                                 | 1      | 1            | 1                                   | 1   | 1      | 1       | 0                      | W=0 |           |                       |