### X9315 Low Noise, Low Power, 32 Taps

#### Data Sheet

December 21, 2009

```

FN8179.2

```

R<sub>H</sub>/V<sub>H</sub>

R<sub>L</sub>/V<sub>L</sub> R<sub>W</sub>/V<sub>W</sub>

Resistor

Arrav

# Digitally Controlled Potentiometer (XDCP™)

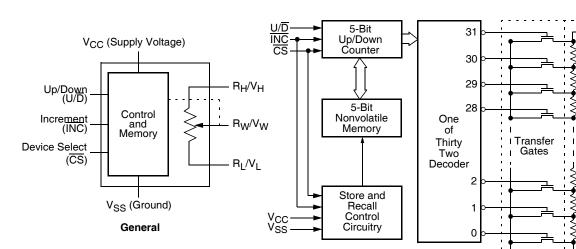

The Intersil X9315 is a digitally controlled potentiometer (XDCP). The device consists of a resistor array, wiper switches, a control section, and nonvolatile memory. The wiper position is controlled by a 3-wire interface.

The potentiometer is implemented by a resistor array composed of 31 resistive elements and a wiper switching network. Between each element and at either end are tap points accessible to the wiper terminal. The position of the wiper element is controlled by the  $\overline{CS}$ ,  $U/\overline{D}$ , and  $\overline{INC}$  inputs. The position of the wiper can be stored in nonvolatile memory and then be recalled upon a subsequent power-up operation.

The device can be used as a three-terminal potentiometer or as a two-terminal variable resistor in a wide variety of applications including:

- Control

- Parameter Adjustments

- Signal Processing

#### Features

- Solid-state potentiometer

- · 3-wire serial interface

- 32 wiper tap points

- Wiper position stored in nonvolatile memory and recalled on power-up

- 31 resistive elements

- Temperature compensated

- End to end resistance range ± 20%

- Terminal voltage, 0 to V<sub>CC</sub>

- Low power CMOS

- V<sub>CC</sub> = 2.7V or 5V

- Active current, 80/400µA max.

- Standby current, 5µA max.

- High reliability

- Endurance, 100,000 data changes per bit

- Register data retention, 100 years

- $R_{TOTAL}$  values =  $10k\Omega$ ,  $50k\Omega$ ,  $100k\Omega$

- Packages

- 8 Ld SOIC, MSOP and PDIP

- Pb-free available (RoHS compliant)

#### Detailed

#### CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc. XDCP is a trademark of Intersil Americas Inc. 2005, 2009. All Rights Reserved All other trademarks mentioned are the property of their respective owners.

# Block Diagram

1

# Ordering Information

| PART NUMBER                  | PART MARKING | V <sub>CC</sub> LIMITS<br>(V) | R <sub>TOTAL</sub><br>(kΩ) | TEMP RANGE<br>(°C) | PACKAGE             | PKG.<br>DWG. # |

|------------------------------|--------------|-------------------------------|----------------------------|--------------------|---------------------|----------------|

| X9315WMZ (Note 2)            | DDT          | 5 ±10%                        | 10                         | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315WMZT1 (Notes 1, 2)      | DDT          |                               |                            | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315WMIT2 (Note 1)          | AAX          |                               |                            | -40 to 85          | 8 Ld MSOP           | M8.118         |

| X9315WMIZ (Note 2)           | AKW          |                               |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315WMIZT1 (Notes 1, 2)     | AKW          |                               |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315WP                      | X9315WP      |                               |                            | 0 to 70            | 8 Ld PDIP           | MDP0031        |

| X9315WST1 (Note 1)           | X9315W       |                               |                            | 0 to 70            | 8 Ld SOIC           | M8.15E         |

| X9315WSZ (Note 2)            | X9315W Z     |                               |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315WSZT1 (Notes 1, 2)      | X9315W Z     |                               |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315WSI                     | X9315W I     |                               |                            | -40 to 85          | 8 Ld SOIC           | M8.15E         |

| X9315WSIT1 (Note 1)          | X9315W I     |                               |                            | -40 to 85          | 8 Ld SOIC           | M8.15E         |

| X9315WSIZ (Note 2)           | X9315W ZI    |                               |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315WSIZT1 (Notes 1, 2)     | X9315W ZI    |                               |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315UMZ (Note 2)            | DDS          |                               | 50                         | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315UMZT1 (Notes 1, 2)      | DDS          |                               |                            | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315UMI                     | AEB          |                               |                            | -40 to 85          | 8 Ld MSOP           | M8.118         |

| X9315UMIT1 (Notes 1, 2)      | AEB          |                               |                            | -40 to 85          | 8 Ld MSOP           | M8.118         |

| X9315UMIZ (Note 2)           | DDR          |                               |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315UMIZT1 (Notes 1, 2)     | DDR          |                               |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315UST2 (Note 1)           | X9315U       |                               |                            | 0 to 70            | 8 Ld SOIC           | M8.15E         |

| X9315USZ (Note 2)            | X9315U Z     |                               |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315USZT1 (Notes 1, 2)      | X9315U Z     |                               |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315USIZ (Note 2)           | X9315U ZI    |                               |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315USIZT1 (Notes 1, 2)     | X9315U ZI    | -                             |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315TMZ (Note 2)            | DDN          |                               | 100                        | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315TMZT1 (Notes 1, 2)      | DDN          |                               |                            | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315TMIZ (Note 2)           | DDL          |                               |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315TMIZT1 (Notes 1, 2)     | DDL          | -                             |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315TSZ (Note 2)            | X9315T Z     | -                             |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315TSZT1 (Notes 1, 2)      | X9315T Z     | -                             |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315TSIZ (Note 2)           | X9315T ZI    | -                             |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315TSIZT1 (Notes 1, 2)     | X9315T ZI    | -                             |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315WMZ-2.7 (Note 2)        | AOI          | 2.7 to 5.5                    | 10                         | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315WMZ-2.7T1 (Notes 1, 2)  | AOI          |                               |                            | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315WMI-2.7T2 (Note 1)      | AAV          |                               |                            | -40 to 85          | 8 Ld MSOP           | M8.118         |

| X9315WMIZ-2.7 (Note 2)       | АКХ          |                               |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315WMIZ-2.7T1 (Notes 1, 2) | АКХ          |                               |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315WS-2.7                  | X9315W F     |                               |                            | 0 to 70            | 8 Ld SOIC           | M8.15E         |

2

### Ordering Information (Continued)

| PART NUMBER                  | PART MARKING | V <sub>CC</sub> LIMITS<br>(V) | R <sub>TOTAL</sub><br>(kΩ) | TEMP RANGE<br>(°C) | PACKAGE             | PKG.<br>DWG. # |

|------------------------------|--------------|-------------------------------|----------------------------|--------------------|---------------------|----------------|

| X9315WS-2.7T1 (Note 1)       | X9315W F     | 2.7 to 5.5                    | 10                         | 0 to 70            | 8 Ld SOIC           | M8.15E         |

| X9315WSZ-2.7 (Note 2)        | X9315W ZF    |                               |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315WSZ-2.7T1 (Notes 1, 2)  | X9315W ZF    |                               |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315WSI-2.7T1 (Note 1)      | X9315W G     |                               |                            | -40 to 85          | 8 Ld SOIC           | M8.15E         |

| X9315WSIZ-2.7 (Note 2)       | X9315W ZG    |                               |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315WSIZ-2.7T1 (Notes 1, 2) | X9315W ZG    |                               |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315UMZ-2.7 (Note 2)        | AKU          |                               | 50                         | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315UMZ-2.7T1 (Notes 1, 2)  | AKU          |                               |                            | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315UMIZ-2.7 (Note 2)       | AJG          |                               |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315UMIZ-2.7T1 (Notes 1, 2) | AJG          |                               |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315US-2.7T2 (Note 1)       | X9315U F     |                               |                            | 0 to 70            | 8 Ld SOIC           | M8.15E         |

| X9315USZ-2.7 (Note 2)        | X9315U ZF    |                               |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315USZ-2.7T1 (Notes 1, 2)  | X9315U ZF    |                               |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315USI-2.7                 | X9315U G     |                               |                            | -40 to 85          | 8 Ld SOIC           | M8.15E         |

| X9315USIZ-2.7 (Note 2)       | X9315U ZG    |                               |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315USIZ-2.7T1 (Notes 1, 2) | X9315U ZG    |                               |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315TMZ-2.7 (Note 2)        | DDP          |                               | 100                        | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315TMZ-2.7T1 (Notes 1, 2)  | DDP          |                               |                            | 0 to 70            | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315TMI-2.7T1 (Note 1)      | ADY          |                               |                            | -40 to 85          | 8 Ld MSOP           | M8.118         |

| X9315TMIZ-2.7 (Note 2)       | DDM          |                               |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315TMIZ-2.7T1 (Notes 1, 2) | DDM          |                               |                            | -40 to 85          | 8 Ld MSOP (Pb-free) | M8.118         |

| X9315TSZ-2.7 (Note 2)        | X9315T ZF    |                               |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315TSZ-2.7T1 (Notes 1, 2)  | X9315T ZF    |                               |                            | 0 to 70            | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315TSIZ-2.7 (Note 2)       | X9315T ZG    |                               |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

| X9315TSIZ-2.7T1 (Notes 1, 2) | X9315T ZG    |                               |                            | -40 to 85          | 8 Ld SOIC (Pb-free) | M8.15          |

NOTES:

1. Please refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

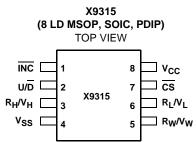

### Pin Configuration

### Pin Names

| SYMBOL                         | DESCRIPTION               |

|--------------------------------|---------------------------|

| R <sub>H</sub> /V <sub>H</sub> | High terminal             |

| R <sub>W</sub> /V <sub>W</sub> | Wiper terminal            |

| RL/VL                          | Low terminal              |

| V <sub>SS</sub>                | Ground                    |

| V <sub>CC</sub>                | Supply voltage            |

| U/D                            | Up/Down control input     |

| INC                            | Increment control input   |

| CS                             | Chip Select control input |

### **Pin Description**

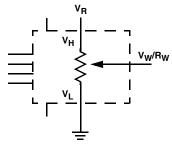

### $R_H/V_H$ and $R_L/V_L$

The high (R<sub>H</sub>/V<sub>H</sub>) and low (R<sub>L</sub>/V<sub>L</sub>) terminals of the X9315 are equivalent to the fixed terminals of a mechanical potentiometer. The minimum voltage is V<sub>SS</sub> and the maximum is V<sub>CC</sub>. The terminology of R<sub>L</sub>/V<sub>L</sub> and R<sub>H</sub>/V<sub>H</sub> references the relative position of the terminal in relation to wiper movement direction selected by the U/D input, and not the voltage potential on the terminal.

### $R_w/V_w$

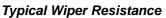

$R_W/V_w$  is the wiper terminal and is equivalent to the movable terminal of a mechanical potentiometer. The position of the wiper within the array is determined by the control inputs. The wiper terminal series resistance is typically 200 $\Omega$  at  $V_{CC} = 5V$ .

### Up/Down (U/D)

The  $U/\overline{D}$  input controls the direction of the wiper movement and whether the counter is incremented or decremented.

### Increment (INC)

The  $\overline{\text{INC}}$  input is negative-edge triggered. Toggling  $\overline{\text{INC}}$  will move the wiper and either increment or decrement the counter in the direction indicated by the logic level on the  $U/\overline{D}$  input.

### Chip Select (CS)

The device is selected when the  $\overline{CS}$  input is LOW. The current counter value is stored in nonvolatile memory when  $\overline{CS}$  is returned HIGH while the  $\overline{INC}$  input is also HIGH. After the store operation is complete the X9315 will be placed in the low power standby mode until the device is selected once again.

### **Principles of Operation**

There are three sections of the X9315: the input control, counter and decode section; the nonvolatile memory; and the resistor array. The input control section operates just like an up/down counter. The output of this counter is decoded to turn on a single electronic switch connecting a point on the resistor array to the wiper output. Under the proper conditions the contents of the counter can be stored in nonvolatile memory and retained for future use. The resistor array is comprised of 31 individual resistors connected in series. At either end of the array and between each resistor is an electronic switch that transfers the connection at that point to the wiper.

The wiper, when at either fixed terminal, acts like its mechanical equivalent and does not move beyond the last position. That is, the counter does not wrap around when clocked to either extreme.

The electronic switches on the device operate in a "make before break" mode when the wiper changes tap positions. If the wiper is moved several positions, multiple taps are connected to the wiper for  $t_{IW}$  (INC to  $V_W$  change). The  $R_{TOTAL}$  value for the device can temporarily be reduced by a significant amount if the wiper is moved several positions.

When the device is powered-down, the last wiper position stored will be maintained in the nonvolatile memory. When power is restored, the contents of the memory are recalled and the wiper is set to the value last stored.

### Instructions and Programming

The  $\overline{INC}$ ,  $U/\overline{D}$  and  $\overline{CS}$  inputs control the movement of the wiper along the resistor array. With  $\overline{CS}$  set LOW the device is selected and enabled to respond to the  $U/\overline{D}$  and  $\overline{INC}$  inputs. HIGH to LOW transitions on  $\overline{INC}$  will increment or decrement (depending on the state of the  $U/\overline{D}$  input) a five bit counter. The output of this counter is decoded to select one of thirty two wiper positions along the resistive array.

The value of the counter is stored in nonvolatile memory whenever  $\overline{\text{CS}}$  transitions HIGH while the  $\overline{\text{INC}}$  input is also HIGH.

The system may select the X9315, move the wiper and deselect the device without having to store the latest wiper position in nonvolatile memory. After the wiper movement is performed as described above and once the new position is reached, the system must keep INC LOW while taking CS HIGH. The new wiper position will be maintained until

changed by the system or until a power-up/down cycle recalled the previously stored data.

This procedure allows the system to always power-up to a preset value stored in nonvolatile memory; then during system operation minor adjustments could be made. The adjustments might be based on user preference, system parameter changes due to temperature drift, etc...

The state of  $U/\overline{D}$  may be changed while  $\overline{CS}$  remains LOW. This allows the host system to enable the device and then move the wiper up and down until the proper trim is attained.

### Mode Selection

| CS       | INC | U/D | MODE                                       |

|----------|-----|-----|--------------------------------------------|

| L        | ~   | Н   | Wiper up                                   |

| L        | ┥   | L   | Wiper down                                 |

| _        | Н   | Х   | Store wiper position to nonvolatile memory |

| Н        | Х   | Х   | Standby                                    |

|          | L   | Х   | No store, return to standby                |

| <b>`</b> | L   | Н   | Wiper Up (not recommended)                 |

| <b>~</b> | L   | L   | Wiper Down (not recommended)               |

### Power-up and Down Requirements

There are no restrictions on the power-up or power-down conditions of V<sub>CC</sub> and the voltages applied to the potentiometer pins provided that V<sub>CC</sub> is always more positive than or equal to V<sub>H</sub>, V<sub>L</sub>, and V<sub>W</sub>, i.e., V<sub>CC</sub>  $\ge$  V<sub>H</sub>, V<sub>L</sub>, V<sub>W</sub>. The V<sub>CC</sub> ramp rate spec is always in effect.

#### **Absolute Maximum Ratings**

| Temperature under bias                                                                                                                     | +135°C   |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Storage temperature65°C to                                                                                                                 | +150°C   |

| Voltage on CS, INC, U/D, VH, VL and                                                                                                        |          |

| V <sub>CC</sub> with respect to V <sub>SS</sub> 1                                                                                          | √ to +7V |

| $\Delta V =  V_H - V_L  \dots \dots$ | 5V       |

| I <sub>W</sub> (10 seconds)                                                                                                                | .±7.5mA  |

#### **Thermal Information**

| Thermal Resistance (Typical, Notes 3, 4) | $\theta_{JA}$ (°C/W) | $\theta_{\text{JC}}$ (°C/W) |

|------------------------------------------|----------------------|-----------------------------|

| 8 Ld SOIC                                | 105                  | 68                          |

| 8 Ld MSOP                                | 154                  | 58                          |

| 8 Ld PDIP                                | 85                   | 57                          |

| Pb-Free Reflow Profile                   |                      | ee link below               |

| http://www.intersil.com/pbfree/Pb-FreeR  | leflow.asp           |                             |

#### **Recommended Operating Conditions**

| Temperature (Commercial)                          | 0°C to +70°C  |

|---------------------------------------------------|---------------|

| Temperature (Industrial)                          | 40°C to +85°C |

| Supply Voltage (V <sub>CC</sub> ) (Note 8) Limits |               |

| X9315                                             | 5V ± 10%      |

| X9315-2.7                                         | 2.7V to 5.5V  |

| Max Wiper Current, I <sub>W</sub>                 | ±3.75mA       |

| Max Power Rating                                  | 10mW          |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 3.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 4. For  $\theta_{JC},$  the "case temp" location is taken at the package top center.

|                                                |                                            |                                                          | LIMITS          |                 |                 |               |

|------------------------------------------------|--------------------------------------------|----------------------------------------------------------|-----------------|-----------------|-----------------|---------------|

| SYMBOL                                         | PARAMETER                                  | TEST CONDITIONS/NOTES                                    | MIN<br>(Note 9) | TYP<br>(Note 8) | MAX<br>(Note 9) | UNIT          |

|                                                | End to end resistance tolerance            |                                                          | -20             |                 | +20             | %             |

| V <sub>VH</sub>                                | V <sub>H</sub> terminal voltage            |                                                          | 0               |                 | V <sub>CC</sub> | V             |

| V <sub>VL</sub>                                | V <sub>L</sub> terminal voltage            |                                                          | 0               |                 | V <sub>CC</sub> | V             |

| R <sub>W</sub>                                 | Wiper resistance                           | $I_W = [V(R_H) - V(R_L)]/R_{TOTAL}, V_{CC} = 5V$         |                 | 200             | 400             | Ω             |

| R <sub>W</sub>                                 | Wiper resistance                           | $I_{W} = [V(R_{H}) - V(R_{L})]/R_{TOTAL}, V_{CC} = 2.7V$ |                 | 400             | 1000            | Ω             |

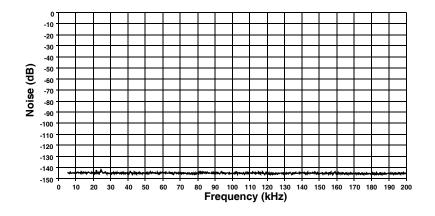

|                                                | Noise                                      | Ref: 1kHz                                                |                 | -120            |                 | dBV           |

|                                                | Resolution                                 |                                                          |                 | 3               |                 | %             |

|                                                | Absolute linearity (Note 5)                | V <sub>w(n)(actual)</sub> - V <sub>w(n)(expected)</sub>  |                 |                 | ±1              | MI<br>(Note 7 |

|                                                | Relative linearity (Note 6)                | V <sub>w(n + 1)</sub> - [V <sub>w(n) + Ml</sub> ]        |                 |                 | ±0.2            | MI<br>(Note 7 |

|                                                | R <sub>TOTAL</sub> temperature coefficient |                                                          |                 | ±300            |                 | ppm/°C        |

|                                                | Ratiometric temperature coefficient        |                                                          |                 | ±20             |                 | ppm/°C        |

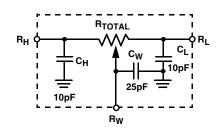

| C <sub>H</sub> /C <sub>L</sub> /C <sub>W</sub> | Potentiometer capacitances                 | See circuit #3 on page 7                                 |                 | 10/10/25        |                 | pF            |

#### Potentiometer Characteristics (Over recommended operating conditions unless otherwise stated.)

NOTES:

- 5. Absolute linearity is utilized to determine actual wiper voltage versus expected voltage = (V<sub>w(n)</sub>(actual) V<sub>w(n)</sub>(expected)) = ±1 MI Maximum.

- 6. Relative linearity is a measure of the error in step size between taps =  $R_{W(n+1)} [R_{w(n)} + MI] = \pm 0.2 MI$ .

- 7. 1 MI = Minimum Increment =  $R_{TOT}/31$ .

- 8. Typical values are for  $T_A = +25^{\circ}C$  and nominal supply voltage.

6

9. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| SYMBOL           | PARAMETER                                             | TEST CONDITIONS                                                                                                                    | MIN<br>(Note 9)       | TYP<br>(Note 8) | MAX<br>(Note 9)       | UNIT |  |

|------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|-----------------------|------|--|

| V <sub>CC</sub>  | Supply Voltage                                        | X9315                                                                                                                              | 4.5                   |                 | 5.5                   | V    |  |

|                  |                                                       | X9315-2.7                                                                                                                          | 2.7                   |                 | 5.5                   | V    |  |

| I <sub>CC1</sub> | V <sub>CC</sub> active current (Increment)            | $\overline{CS} = V_{IL}, U/\overline{D} = V_{IL} \text{ or } V_{IH} \text{ and } \overline{INC} = 0.4V$<br>@ max. t <sub>CYC</sub> |                       |                 | 80                    | μA   |  |

| I <sub>CC2</sub> | V <sub>CC</sub> active current (Store) (EEPROM Store) | $\overline{CS} = V_{IH}, U/\overline{D} = V_{IL} \text{ or } V_{IH} \text{ and } \overline{INC} = V_{IH} @$ max. t <sub>WR</sub>   |                       |                 | 400                   | μA   |  |

| I <sub>SB</sub>  | Standby supply current                                | $\overline{\text{CS}}$ = V_{CC} - 0.3V, U/\overline{\text{D}} and $\overline{\text{INC}}$ = V_{SS} or V_{CC} - 0.3V                |                       |                 | 5                     | μA   |  |

| ILI              | CS, INC, U/D input leakage current                    | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                      | -10                   |                 | +10                   | μA   |  |

| VIH              | CS, INC, U/D input HIGH voltage                       |                                                                                                                                    | V <sub>CC</sub> x 0.7 |                 | V <sub>CC</sub> + 0.5 | V    |  |

| $V_{IL}$         | CS, INC, U/D input LOW voltage                        |                                                                                                                                    | -0.5                  |                 | V <sub>CC</sub> x 0.1 | V    |  |

| C <sub>IN</sub>  | CS, INC, U/D input capacitance                        | $V_{CC} = 5V$ , $V_{IN} = V_{SS}$ , $T_A = +25^{\circ}C$ , $f = 1MHz$                                                              |                       | 10              |                       | pF   |  |

#### DC Electrical Specifications (Over recommended operating conditions unless otherwise specified.

#### **Endurance and Data Retention**

| PARAMETER         | MIN     | UNIT                 |

|-------------------|---------|----------------------|

| Minimum endurance | 100,000 | Data changes per bit |

| Data retention    | 100     | Years                |

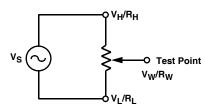

#### Test Circuit #1

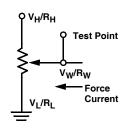

#### Test Circuit #2

#### **Circuit #3 SPICE Macro Model**

#### **AC Conditions of Test**

| Input pulse levels        | 0V to 3V |

|---------------------------|----------|

| Input rise and fall times | 10ns     |

| Input reference levels    | 1.5V     |

### AC Electrical Specifications (Over recommended operating conditions unless otherwise specified)

|                 |                        | LIMITS          |                 |                 |      |  |

|-----------------|------------------------|-----------------|-----------------|-----------------|------|--|

| SYMBOL          | PARAMETER              | MIN<br>(Note 9) | TYP<br>(Note 8) | MAX<br>(Note 9) | UNIT |  |

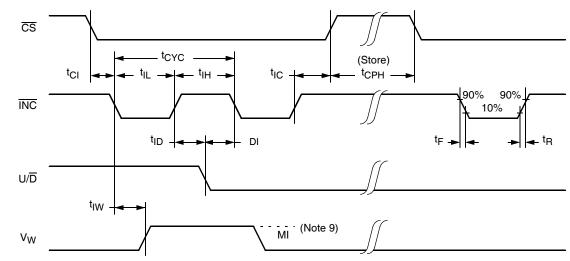

| t <sub>CI</sub> | CS to INC setup        | 100             |                 |                 | ns   |  |

| t <sub>ID</sub> | INC HIGH to U/D change | 100             |                 |                 | ns   |  |

| t <sub>DI</sub> | U/D to INC setup       | 2.9             |                 |                 | μs   |  |

| t <sub>IL</sub> | INC LOW period         | 1               |                 |                 | μs   |  |

| tн              | INC HIGH period        | 1               |                 |                 | μs   |  |

| SYMBOL                                      |                               | LIMITS          |                 |                 |      |  |

|---------------------------------------------|-------------------------------|-----------------|-----------------|-----------------|------|--|

|                                             | PARAMETER                     | MIN<br>(Note 9) | TYP<br>(Note 8) | MAX<br>(Note 9) | UNIT |  |

| <sup>t</sup> IC                             | INC Inactive to CS inactive   | 1               |                 |                 | μs   |  |

| t <sub>CPH</sub>                            | CS Deselect time (NO STORE)   | 100             |                 |                 | ns   |  |

| t <sub>CPH</sub>                            | CS Deselect time (STORE)      | 10              |                 |                 | ms   |  |

| t <sub>IW</sub>                             | INC to Vw change              |                 | 1               | 5               | μs   |  |

| <sup>t</sup> CYC                            | INC cycle time                | 4               |                 |                 | μs   |  |

| t <sub>R,</sub> t <sub>F</sub><br>(Note 10) | INC input rise and fall time  |                 |                 | 500             | μs   |  |

| t <sub>PU</sub><br>(Note 10)                | Power-up to wiper stable      |                 |                 | 5               | μs   |  |

| t <sub>R</sub> V <sub>CC</sub><br>(Note 10) | V <sub>CC</sub> power-up rate | 0.2             |                 | 50              | V/ms |  |

| twR                                         | Store cycle                   |                 | 5               | 10              | ms   |  |

#### AC Electrical Specifications (Over recommended operating conditions unless otherwise specified) (Continued)

NOTE:

10. This parameter is not 100% tested.

### AC Timing

#### NOTE:

11. MI in the A.C. timing diagram refers to the minimum incremental change in the  $V_W$  output due to a change in the wiper position.

### Symbol Table

# Performance Characteristics (Typical)

**Typical Noise**

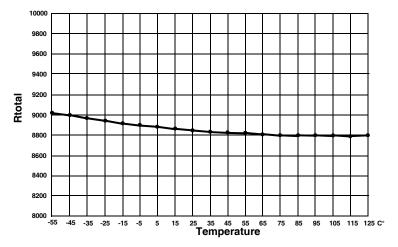

### Typical Rtotal vs. Temperature

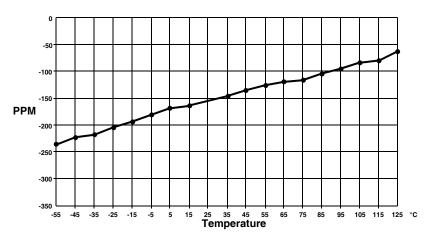

Typical Total Resistance Temperature Coefficient

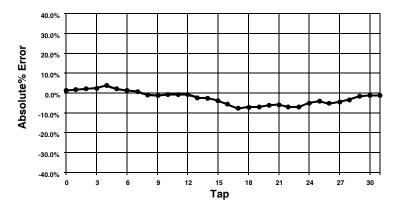

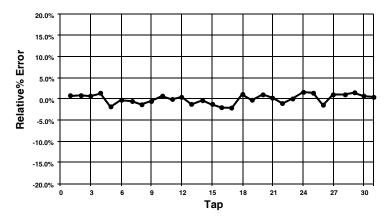

Typical Absolute% Error per Tap Position

Typical Relative% Error per Tap Position

### **Applications Information**

Electronic digitally controlled (XDCP) potentiometers provide three powerful application advantages; (1) the variability and reliability of a solid-state potentiometer, (2) the flexibility of computer-based digital controls, and (3) the retentivity of nonvolatile memory used for the storage of multiple potentiometer settings or data.

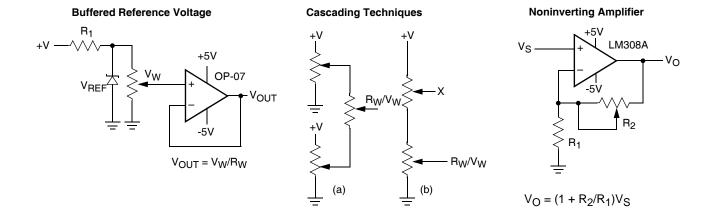

### **Basic Configurations of Electronic Potentiometers**

Three terminal potentiometer; variable voltage divider

### **Basic Circuits**

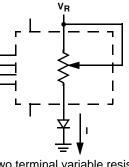

Two terminal variable resistor; variable current

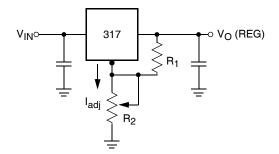

Voltage Regulator

$V_O (REG) = 1.25V (1 + R_2/R_1) + I_{adj} R_2$

**Comparator with Hysteresis**

$$\begin{split} V_{UL} &= \{R_1/(R_1 + R_2)\} \; V_O(max) \\ V_{LL} &= \{R_1/(R_1 + R_2)\} \; V_O(min) \end{split}$$

(for additional circuits see AN115)

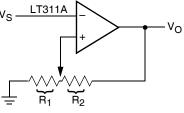

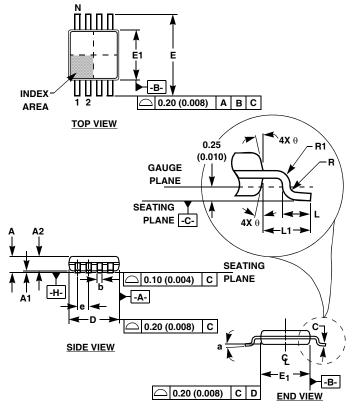

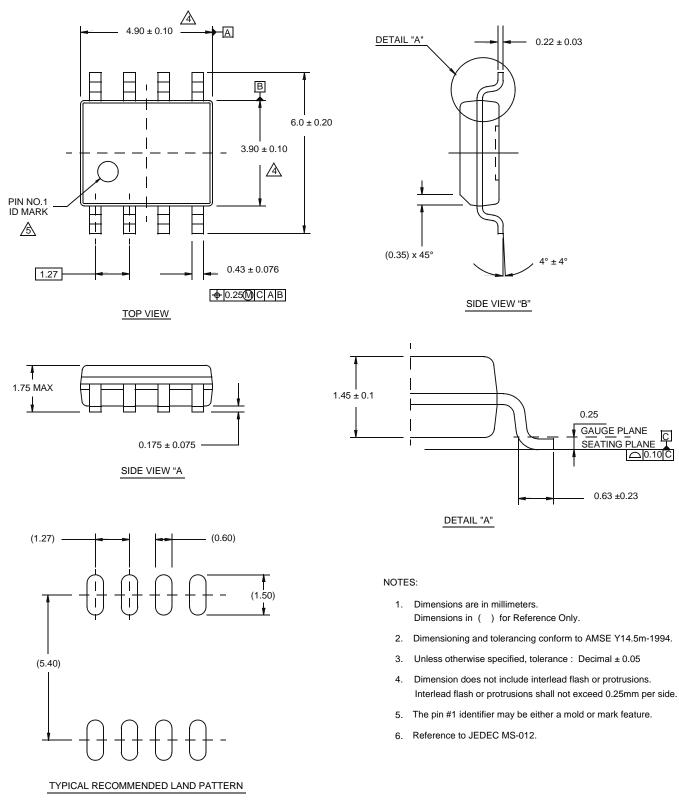

### Mini Small Outline Plastic Packages (MSOP)

#### NOTES:

- 1. These package dimensions are within allowable dimensions of JEDEC MO-187BA.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1994.

- 3. Dimension "D" does not include mold flash, protrusions or gate burrs and are measured at Datum Plane. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E1" does not include interlead flash or protrusions and are measured at Datum Plane. -H- Interlead flash and protrusions shall not exceed 0.15mm (0.006 inch) per side.

- 5. Formed leads shall be planar with respect to one another within 0.10mm (0.004) at seating Plane.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. Dimension "b" does not include dambar protrusion. Allowable dambar protrusion shall be 0.08mm (0.003 inch) total in excess of "b" dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm (0.0027 inch).

- 10. Datums -A and -B to be determined at Datum plane - H -

- 11. Controlling dimension: MILLIMETER. Converted inch dimensions are for reference only.

# M8.118 (JEDEC MO-187AA)

**8 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE**

| ,         | MAX             | MIN             |                                |                                                |

|-----------|-----------------|-----------------|--------------------------------|------------------------------------------------|

|           |                 | IVIIIN          | MAX                            | NOTES                                          |

|           | 0.043           | 0.94            | 1.10                           | -                                              |

| 2         | 0.006           | 0.05            | 0.15                           | -                                              |

| )         | 0.037           | 0.75            | 0.95                           | -                                              |

| )         | 0.014           | 0.25            | 0.36                           | 9                                              |

|           | 0.008           | 0.09            | 0.20                           | -                                              |

| ;         | 0.120           | 2.95            | 3.05                           | 3                                              |

| j         | 0.120           | 2.95            | 3.05                           | 4                                              |

| 0.026 BSC |                 | 0.65 BSC        |                                | -                                              |

| '         | 0.199           | 4.75            | 5.05                           | -                                              |

| j         | 0.028           | 0.40            | 0.70                           | 6                                              |

| 0.037 REF |                 | 0.95 REF        |                                | -                                              |

| 8         |                 | 8               |                                | 7                                              |

| ;         | -               | 0.07            | -                              | -                                              |

| 1         | -               | 0.07            | -                              | -                                              |

|           | 15 <sup>0</sup> | 5 <sup>0</sup>  | 15 <sup>0</sup>                | -                                              |

|           | 6 <sup>0</sup>  | 0 <sup>0</sup>  | 6 <sup>0</sup>                 | -                                              |

| 3         | 3               | 15 <sup>0</sup> | 15 <sup>°</sup> 5 <sup>°</sup> | 15 <sup>0</sup> 5 <sup>0</sup> 15 <sup>0</sup> |

## **Package Outline Drawing**

### M8.15E

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE Rev 0, 08/09

$0.22 \pm 0.03$

$4^{\circ} \pm 4^{\circ}$

0.25

GAUGE PLANE

0.63 ±0.23

0.10 C

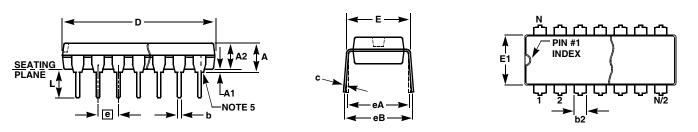

### Plastic Dual-In-Line Packages (PDIP)

#### MDP0031 PLASTIC DUAL-IN-LINE PACKAGE

| SYMBOL | PDIP8 | PDIP14 | PDIP16 | PDIP18 | PDIP20 | TOLERANCE     | NOTES |

|--------|-------|--------|--------|--------|--------|---------------|-------|

| А      | 0.210 | 0.210  | 0.210  | 0.210  | 0.210  | MAX           |       |

| A1     | 0.015 | 0.015  | 0.015  | 0.015  | 0.015  | MIN           |       |

| A2     | 0.130 | 0.130  | 0.130  | 0.130  | 0.130  | ±0.005        |       |

| b      | 0.018 | 0.018  | 0.018  | 0.018  | 0.018  | ±0.002        |       |

| b2     | 0.060 | 0.060  | 0.060  | 0.060  | 0.060  | +0.010/-0.015 |       |

| С      | 0.010 | 0.010  | 0.010  | 0.010  | 0.010  | +0.004/-0.002 |       |

| D      | 0.375 | 0.750  | 0.750  | 0.890  | 1.020  | ±0.010        | 1     |

| E      | 0.310 | 0.310  | 0.310  | 0.310  | 0.310  | +0.015/-0.010 |       |

| E1     | 0.250 | 0.250  | 0.250  | 0.250  | 0.250  | ±0.005        | 2     |

| е      | 0.100 | 0.100  | 0.100  | 0.100  | 0.100  | Basic         |       |

| eA     | 0.300 | 0.300  | 0.300  | 0.300  | 0.300  | Basic         |       |

| eB     | 0.345 | 0.345  | 0.345  | 0.345  | 0.345  | ±0.025        |       |

| L      | 0.125 | 0.125  | 0.125  | 0.125  | 0.125  | ±0.010        |       |

| Ν      | 8     | 14     | 16     | 18     | 20     | Reference     |       |

NOTES:

Rev. B 2/99

1. Plastic or metal protrusions of 0.010" maximum per side are not included.

2. Plastic interlead protrusions of 0.010" maximum per side are not included.

3. Dimensions E and eA are measured with the leads constrained perpendicular to the seating plane.

- 4. Dimension eB is measured with the lead tips unconstrained.

- 5. 8 and 16 lead packages have half end-leads as shown.

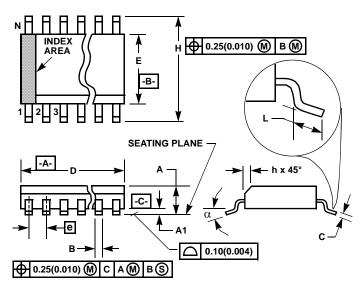

### Small Outline Plastic Packages (SOIC)

#### NOTES:

- 1. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

#### M8.15 (JEDEC MS-012-AA ISSUE C) 8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INC       | HES    | MILLIN   |      |       |

|--------|-----------|--------|----------|------|-------|

| SYMBOL | MIN       | MAX    | MIN      | MAX  | NOTES |

| А      | 0.0532    | 0.0688 | 1.35     | 1.75 | -     |

| A1     | 0.0040    | 0.0098 | 0.10     | 0.25 | -     |

| В      | 0.013     | 0.020  | 0.33     | 0.51 | 9     |

| С      | 0.0075    | 0.0098 | 0.19     | 0.25 | -     |

| D      | 0.1890    | 0.1968 | 4.80     | 5.00 | 3     |

| E      | 0.1497    | 0.1574 | 3.80     | 4.00 | 4     |

| е      | 0.050 BSC |        | 1.27 BSC |      | -     |

| Н      | 0.2284    | 0.2440 | 5.80     | 6.20 | -     |

| h      | 0.0099    | 0.0196 | 0.25     | 0.50 | 5     |

| L      | 0.016     | 0.050  | 0.40     | 1.27 | 6     |

| Ν      | 8         |        | 8        |      | 7     |

| α      | 0°        | 8°     | 0°       | 8°   | -     |

Rev. 1 6/05

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com