## **HA-4902/883**

January 1989

#### **Precision Quad Comparator**

#### Features

- This Circuit is Processed in Accordance to Mil-Std-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- Low Input Sensitivity ............... 0.5mV (Max)

0.05mV (Typ)

- Single or Dual-Voltage Supply Operation

- Selectable Output Logic Levels

- Active Pull-Up/Pull-Down Output Circuit No External Resistors Required

#### Applications

- Threshold Detector

- Zero-Crossing Detector

- Window Detector

- Analog Interfaces for Microprocessors

- . High Stability Oscillators

- Logic System Interface

#### Description

The HA-4902/883 is a monolithic, quad, precision comparator offering fast response time, low offset voltage. low offset current, and virtually no channel-to-channel crosstalk for applications requiring accurate, high speed, signal level detection. This comparator can sense signals at ground level while being operated from either single +5V supply (digital systems) or from dual supplies (analog networks) up to ±15V. The HA-4902/883 contains a unique current driven output stage which can be connected to logic system supplies (VLOGIC+ and VLOGIC-) to make the output levels directly compatible (no external components needed) with any standard logic or special system logic levels. In combination analog/digital systems, the design employed in the HA-4902/883 input and output stages prevents troublesome ground coupling of signals between analog and digital portions of the system.

This comparator's combination of features makes it an ideal component for signal detection and processing in data acquisition systems, test equipment, and microprocessor/analog signal interface network.

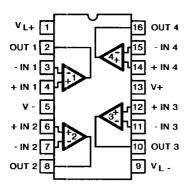

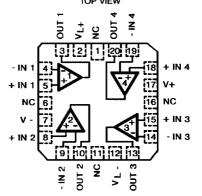

The HA-4902/883 is available in a 16 pin Ceramic DIP package and in a 20 pin Ceramic LCC package and is specified over the military, -55°C to +125°C, temperature range.

#### **Pinouts**

HA1-4902/883 (CERAMIC DIP) TOP VIEW

HA4-4902/883 (CERAMIC LCC) TOP VIEW

#### Thermal Information **Absolute Maximum Ratings** $\theta_{j\boldsymbol{a}}$ Thermal Resistance θјс Ceramic DIP Package ...... 76°C/W 17°C/W Peak Output Current ......±50mA Ceramic LCC Package ..... 76°C/W 19°C/W Output Short Circuit Current Duration . . . . . . . Indefinite Package Power Dissipation at +75°C (One Amplifier Shorted to GND) Junction Temperature ..... +175°C Ceramic LCC Package ......1.32W Storage Temperature Range. . . . . . . -65°C to +150°C Package Power Dissipation Derating Factor Above +75°C ESD Rating ......< 2000V Ceramic LCC Package ...... 13.1 mW/°C Lead Temperature (Soldering 10 sec) . . . . . . . . . . +275°C CAUTION: Absolute maximum ratings are limiting values, applied individually beyond which the serviceability of the circuit may be impaired. Functional operability under any of these conditions is not necessarily implied. **Recommended Operating Conditions**

####

Logic Supply Voltage (V<sub>L</sub>+) .....+5V

Device Tested at: Supply Voltage = ±15V, V<sub>L</sub> = 0V, Unless Otherwise Specified.

Operating Temperature Range ...... -55°C to +125°C

| D.C. PARAMETERS       | SYMBOL          | CONDITIONS                                                  | GROUP A<br>SUBGROUP | TEMPERATURE   | LIMITS |     | Į .   |

|-----------------------|-----------------|-------------------------------------------------------------|---------------------|---------------|--------|-----|-------|

|                       |                 |                                                             |                     |               | MIN    | MAX | UNITS |

| Input Offset Voltage  | VIO             | V <sub>CM</sub> = 0V, V <sub>OUT</sub> = 1.4V<br>See Note 3 | 1                   | +25°C         | -5     | 5   | mV    |

|                       |                 |                                                             | 2,3                 | +125°C, -55°C | -8     | 8   | mV    |

| Input Bias Current    | +l <sub>B</sub> | V <sub>CM</sub> = ov                                        | 1                   | +25°C         | -150   | 150 | nA    |

|                       |                 |                                                             | 2,3                 | +125°C, -55°C | -200   | 200 | nA    |

|                       | -i <sub>B</sub> | V <sub>CM</sub> = 0V                                        | 1                   | +25°C         | -150   | 150 | nA    |

|                       |                 |                                                             | 2,3                 | +125°C, -55°C | -200   | 200 | nA    |

| Input Offset Current  | Ol.             | V <sub>CM</sub> = 0V                                        | 1                   | +25°C         | -35    | 35  | nA    |

|                       |                 |                                                             | 2,3                 | +125°C, -55°C | -45    | 45  | nA    |

| Input Sensitivity     | INSEN           | See Note 3                                                  | 1                   | +25°C         | -0.5   | 0.5 | mV    |

|                       |                 |                                                             | 2,3                 | +125°C, -55°C | -0.6   | 0.6 | m۷    |

| Output Voltage Levels | VOL             | I <sub>SINK</sub> = 3mA                                     | 1                   | +25°C         | -      | 0.4 | ٧     |

|                       |                 |                                                             | 2, 3                | +125°C, -55°C | -      | 0.4 | ٧     |

|                       | νон             | ISOURCE = 3mA                                               | 1                   | +25°C         | 3.5    | -   | ٧     |

|                       |                 |                                                             | 2,3                 | +125°C, -55°C | 3.5    | -   | ٧     |

| Output Current        | ISINK           | V <sub>OUT</sub> ≤ 0.4V                                     | 1                   | +25°C         | 3      | -   | mA    |

|                       |                 |                                                             | 2,3                 | +125°C, -55°C | 3      | -   | mA    |

|                       | SOURCE          | V <sub>OUT</sub> ≥ 3.5V                                     | 1                   | +25°C         |        | -3  | mA    |

|                       |                 |                                                             | 2,3                 | +125°C, -55°C | 1      | -3  | mA    |

| Supply Current        | +Icc Vo         | V <sub>OUT</sub> = V <sub>OL</sub> , V <sub>OH</sub>        | 1                   | +25°C         | -      | 20  | mA    |

|                       |                 |                                                             | 2,3                 | +125°C, -55°C | -      | 20  | mA    |

|                       | -lcc            | V <sub>OUT</sub> = V <sub>OL</sub> , V <sub>OH</sub>        | 1                   | +25°C         | 1      | 8   | mA    |

|                       |                 |                                                             | 2, 3                | +125°C, -55°C | -      | 10  | mA    |

| Logic Current         | ΙL              | V <sub>OUT</sub> = V <sub>OL</sub> , V <sub>OH</sub>        | 1                   | +25°C         | -      | 6   | mA    |

|                       |                 |                                                             | 2, 3                | +125°C, -55°C | -      | 8   | mA    |

CAUTION: This device is sensitive to electrostatic discharge. Proper I.C. handling procedures should be followed.

#### TABLE 2. A.C. ELECTRICAL PERFORMANCE CHARACTERISTICS

Table 2 Intentionally Left Blank. See A.C. Specifications on Table 3.

#### TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

Device Characterized at: Supply Voltage = ±15V, V<sub>L</sub> = GND, Unless Otherwise Specified.

|               |                  |                                    |       |             | LIMITS |      |       |

|---------------|------------------|------------------------------------|-------|-------------|--------|------|-------|

| PARAMETERS    | SYMBOL           | CONDITIONS                         | NOTES | TEMPERATURE | MIN    | MAX  | UNITS |

| Response Time | t <sub>pd0</sub> | +100mV Input Step, 10mV Overdrive  | 1, 2  | +25°C       | -      | 200  | ns    |

|               | t <sub>pd1</sub> | -100mV Input Step, -10mV Overdrive | 1, 2  | +25°C       | ,      | 215  | ns    |

| Common Mode   | +CMR             |                                    | 1     | +25°C       | -      | 12.4 | V     |

| Flange        | -CMR             |                                    | 1     | +25°C       | -15    | -    | ٧     |

- NOTES: 1. Parameters listed in Table 3 are controlled via design or process parameters and are not directly tested at final production. These parameters are lab characterized upon initial design release, or upon design changes. These parameters are guaranteed by characterization based upon data from multiple production runs which reflect lot to lot and within lot variation.

- 2. F  $\approx$  100Hz, duty cycle  $\approx$  50%, inverting input driven, all unused inverting inputs tie to +5V.

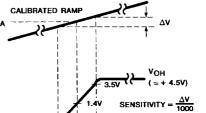

- 3. Refer to enlarged area of test waveform A. Offset voltage is measured when V<sub>OUT</sub> = 1.4V. Sensitivity is measured on the transition edge at 0.4V and 3.5V. Sensitivity is the change in differential input voltage required to change the output state. Sensitivity includes the effects of offset voltage, offset current, common mode rejection and voltage gain.

**TABLE 4. ELECTRICAL TEST REQUIREMENTS**

| MIL-STD-883 TEST REQUIREMENTS               | SUBGROUPS (SEE TABLES 1 & 2) |  |  |  |

|---------------------------------------------|------------------------------|--|--|--|

| Interim Electrical Parameters (Pre Burn-in) | 1                            |  |  |  |

| Final Electrical Test Parameters            | 1*,2,3                       |  |  |  |

| Group A Test Requirements                   | 1, 2, 3                      |  |  |  |

| Groups C & D Endpoints                      | 1                            |  |  |  |

<sup>\*</sup> PDA applies to Subgroup 1 only.

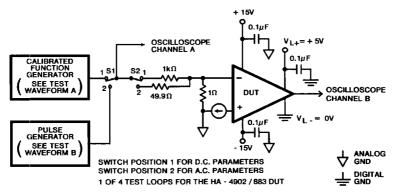

#### Test Circuit (Applies to Tables 1 and 3)

For Detailed Information, Refer to HA-4902/883 Test Tech Brief

#### Test Waveform A (Applies to Table 1)

# $V_{OH} = \frac{100}{100}$ $V_{OH} = \frac{100}{100}$ $V_{OL} = \frac{100}{100}$

## ENLARGED VIEW INPUT: CHANNEL A

OFFSET VOLTAGE

$(V_{1O}) = \frac{V_A}{1000}$

DUT OUTPUT: CHANNEL B

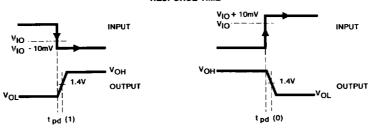

#### Test Waveform B (Applies to Table 3)

V<sub>OL</sub> (≈ 0V)

NOTE: Response time testing is done after V<sub>[O</sub> testing to acquire the actual device offset voltage. 10mV overdrive is then added (or subtracted depending on state) to this measured V<sub>[O</sub> value.

## **Burn-In Circuits** HA1-4902/883 CERAMIC DIP + 5V O D<sub>1</sub> C<sub>5</sub> 16 8 R<sub>3</sub> **§** ANALOG GND DIGITAL GND HA4-4902/883 CERAMIC LCC + 5V O ≺ fo $C_1$ R<sub>4</sub> $R_1$ -O V+ V - O $c^3$ 7 D3 10 11 12 13 ANALOG GND ,βR₂ **∮**R<sub>3</sub> DIGITAL GND NOTES: $R_1 = 5k\Omega$ , $\pm 5\%$

$C_1 = C_2 = C_3 = 0.01 \mu F/Socket (Min) or 0.1 \mu F/Row (Min)$

01 = 02 = 03 = 0.01 \( \text{pr/Socket} \) (Min) or 0.1 \( \text{pr/Now} \) (Min)

01 = 02 = 03 = IN4002 or Equivalent/Board

\[ \left( \text{V+}) - \left( \text{V-} \right) \] = 30V

$V_L = 0V$ ,  $V_L + = 5V$   $t_0 = 5V$  (Static Burn-In)

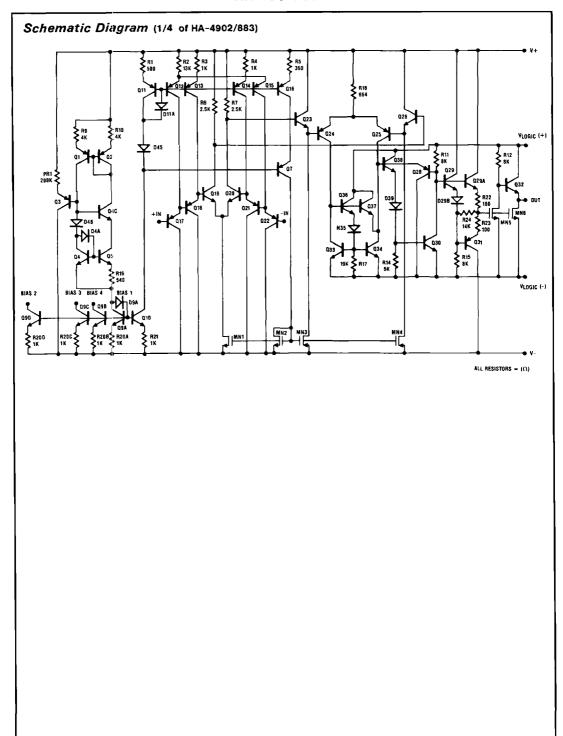

#### Die Characteristics

DIE DIMENSIONS:

95 x 105 x 19 mils (2420 x 2670 x 483 μm)

METALLIZATION:

Type: Aluminum Thickness: 16kÅ ± 2kÅ

WORST CASE CURRENT DENSITY:

0.4 x 10<sup>5</sup>A/cm<sup>2</sup>

SUBSTRATE POTENTIAL (Powered Up): V-

GLASSIVATION:

Type: Nitride Thickness: 7kÅ ± 0.7kÅ

**TRANSISTOR COUNT: 137**

PROCESS: Combination of Std. Linear and

MOS Dielectric Isolation

DIE ATTACH:

Material: Gold/Silicon Eutectic Alloy

Temperature: Ceramic DIP — 460°C (Max)

Ceramic LCC — 420°C (Max)

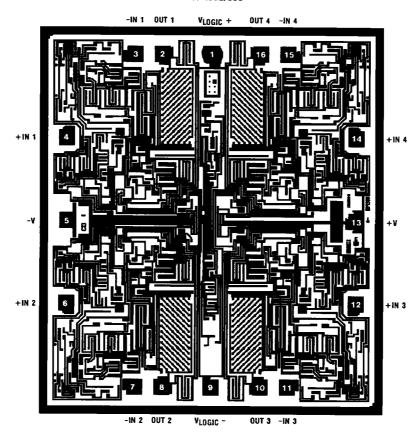

#### Metallization Mask Layout

HA-4902/883

NOTE: Bond Pad Numbers Correspond to 16 Pin Ceramic DIP Only.

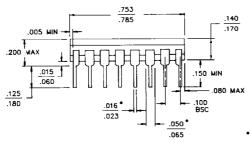

#### Packaging †

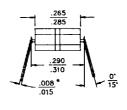

#### 16 PIN CERAMIC DIP

\* INCREASE MAX LIMIT BY .003 INCHES MEASURED AT CENTER OF FLAT FOR SOLDER FINISH

LEAD MATERIAL: Type B LEAD FINISH: Type A

PACKAGE MATERIAL: Ceramic, 90% Alumina

PACKAGE SEAL:

Material: Glass Frit

Temperature: 450°C ± 10°C Method: Furnace Seal

#### INTERNAL LEAD WIRE:

Material: Aluminum Diameter: 1.25 Mil

Bonding Method: Ultrasonic

COMPLIANT OUTLINE: 38510 D-2

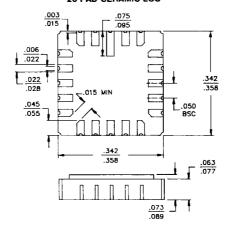

#### 20 PAD CERAMIC LCC

PAD MATERIAL: Type C PAD FINISH: Type A

FINISH DIMENSION: Type A

PACKAGE MATERIAL: Multilayer Ceramic, 90% Alumina

PACKAGE SEAL:

Material: Gold/Tin (80/20) Temperature: 320°C ± 10°C Method: Furnace Braze

#### INTERNAL LEAD WIRE:

Material: Aluminum Diameter: 1.25 Mil

Bonding Method: Ultrasonic COMPLIANT OUTLINE: 38510 C-2

NOTE: All Dimensions are Min Max Dimensions are in inches.

## **HA-4902**

#### **DESIGN INFORMATION**

#### **Precision Quad Comparator**

The information contained in this section has been developed through characterization by Harris Semiconductor and is for use as application and design aid only. These characteristics are not 100% tested and no product guarantee is implied.

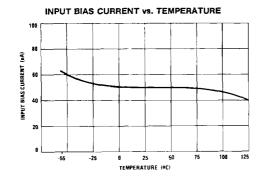

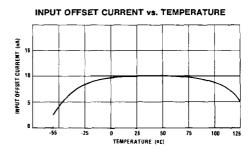

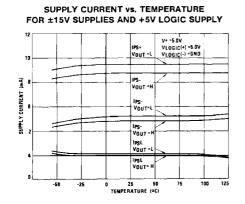

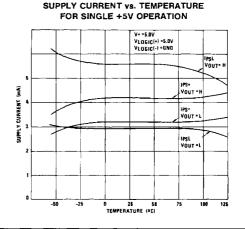

Typical Performance Curves Unless Otherwise Specified: TA = +25°C, VSUPPLY = ±15V, VLOGIC + = 5V, VLOGIC - = 0V

## INPUT BIAS CURRENT vs. COMMON MODE INPUT VOLTAGE (VDIFF = 0V)

#### **DESIGN INFORMATION** (Continued)

The information contained in this section has been developed through characterization by Harris Semiconductor and is for use as application and design aid only. These characteristics are not 100% tested and no product guarantee is implied.

Typical Performance Curves Unless Otherwise Specified: T<sub>A</sub> = +25°C, V<sub>SUPPLY</sub> = ±15V V<sub>LOGIC</sub> + = 5V, V<sub>LOGIC</sub> - = 0V

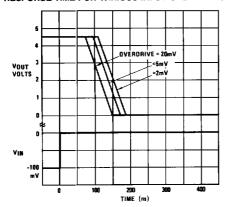

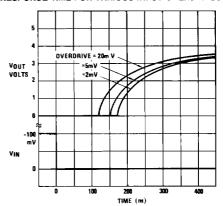

#### RESPONSE TIME FOR VARIOUS INPUT OVERDRIVES

#### RESPONSE TIME FOR VARIOUS INPUT OVERDRIVES

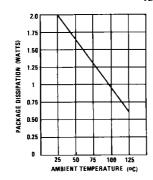

#### MAXIMUM PACKAGE DISSIPATION vs. TAMBIENT

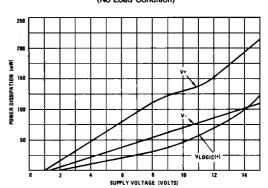

### MAXIMUM POWER DISSIPATION vs. SUPPLY VOLTAGE (No Load Condition)

NOTE: Total Power Dissipation (TPD) is the sum of individual dissipation contributions of V+, V- and V<sub>LOGIC</sub> shown in curves of Power Dissipation vs. Supply Voltages. The calculated TPD is then located on the graph of Maximum Allowable Package Dissipation vs. Ambient Temperature to determine ambient temperature operating limits imposed by the calculated TPD (See Performance Curves). For instance, the combination of ±15V, 5V, 0V (±V, V<sub>LOGIC</sub> +, V<sub>LOGIC</sub> -) gives a TPD of 350mW, the combination ±15V, 0V gives a TPD of 450mW.

#### **DESIGN INFORMATION (Continued)**

The information contained in this section has been developed through characterization by Harris Semiconductor and is for use as application and design aid only. These characteristics are not 100% tested and no product guarantee is implied.

#### TYPICAL PERFORMANCE CHARACTERISTICS

Device Characterized at: Supply Voltage = ±15V, V<sub>L</sub>+ = 5V, V<sub>L</sub>- = 0V, Unless Otherwise Specified.

| PARAMETERS           | CONDITIONS                             | TEMP  | TYPICAL | DESIGN<br>LIMIT | UNITS |

|----------------------|----------------------------------------|-------|---------|-----------------|-------|

| Offset Voltage       | Note 3                                 | Full  | 0.5     | Table 1         | mV    |

| Input Bias Current   |                                        | +25°C | 50      | Table 1         | nA    |

|                      |                                        | Full  | 90      | Table 1         | nA    |

| Input Offset Current |                                        | +25°C | 10      | Table 1         | nA    |

|                      |                                        | Full  | 20      | Table 1         | nA    |

| Input Sensitivity    | Note 3                                 | Full  | 50      | Table 1         | μ۷    |

| Output Level         | VOL; ISINK = 3mA                       | Full  | 0.15    | Table 1         | V     |

|                      | VOH; ISOURCE = 3mA                     | Full  | 4.3     | Table 1         | V     |

| Supply Current       | +ICC; VOUT = VOH                       | Full  | 10      | Table 1         | mA    |

|                      | +1CC; VOUT = VOL                       | Full  | 15      | Table 1         | mA    |

|                      | -ICC; VOUT = VOH                       | Full  | -6      | Table 1         | mA    |

|                      | -ICC; VOUT = VOL                       | Full  | -8      | Table 1         | mA    |

| Logic Current        | ار; V <sub>OUT</sub> = V <sub>OH</sub> | Full  | 2       | Table 1         | mA    |

|                      | IL; VOUT = VOL                         | Full  | 4       | Table 1         | mA    |

| Response Time        | t <sub>pd0</sub>                       | Full  | 150     | Table 3         | ns    |

|                      | tpd1                                   | Full  | 150     | Table 3         | ns    |

#### Applying The HA-4902 Comparator

#### **Supply Connections**

This device is exceptionally versatile in working with most available power supplies. The voltage applied to the V+ and V- terminals determines the allowable input signal range, while the voltage applied to the VL+ and VL- determines the output swing. In systems where dual analog supplies are available, these would be connected to V+ and V-, while the logic supply and return would be connected to VLOGIC + and VLOGIC -. The analog and logic supply commons can be connected together at one point in the system, since the comparator is immune to noise on the logic supply ground. A negative output swing may be obtained by connecting VL+ to ground and V<sub>I</sub> - to a negative supply. Bipolar output swings (15Vp-p, max.) may be obtained using dual supplies. In systems where only a single logic supply is available (+5V to +15V), V+ and VLOGIC + may be connected together to the positive supply while V- and VLOGIC - are grounded. If an input signal could swing negative with respect to the Vterminal, a resistor should be connected in series with the input to limit input current to < 5mA since the C-B junction of the input transistor would be forward biased.

#### **Unused Inputs**

Inputs of unused comparator sections should be tied to a differential voltage source to prevent output "chatter"

(VDIFF  $\geq$  VIO). All unused inverting inputs may be tied to +5V and non-inverting inputs tied to ground.

#### Crosstalk

Simultaneous high frequency operation of all other channels in the package will not affect the output logic state of a given channel, provided that its differential input voltage is sufficient to define a given logic state ( $\Delta V_{|N} \ge \pm V_{|O}$ ). Low level or high impedance input lines should be shielded from other signal sources to reduce crosstalls and interference

#### **Power Supply Decoupling**

Decouple all power supply lines with  $0.01\mu F$  ceramic capacitors to a ground line located near the package to reduce coupling between channels or from external sources.

#### Response Time

Fast rise time (< 200ns) input pulses of several volts amplitude may result in delay times somewhat longer than those illustrated for 100mV steps. Operating speed is optimized by limiting the maximum differential input voltage applied, with resistor-diode clamping networks.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Analog Comparators category:

Click to view products by Renesas manufacturer:

Other Similar products are found below:

633740E NCV2200SN2T1G NCV2200SQ2T2G SC339DR2G LM2901SNG LM339SNG AP393AM8G-13 TS393CD C3 LM393SNG

55122 5962-8757203IA MAX971ESA+T MAX961ESAT MAX944ESD+T MAX984CPE MAX9062EBSTG45 RT2902YDT

M38510/11201B2A NTE911 MAX984ESE+T 5962-8751601DA 5962-8751601CA MAX961EUA+T MAX9065EBS+TG45

NCV2202SN2T1G MAX919ESA+T MAX19005CCS+ LM339EDR2G NTE919 NTE922 TS883IQ2T LT6700HVCS6-3#TRMPBF

LT6700HVHS6-3#TRMPBF MAX978EEE+T MAX975ESA+T MAX9602EUG+T MAX997EUA+T MIC841NYC5-T5 LM393WDT

MCP6564T-E/STVAO MAX983ESA+T NCX2200GMAZ LTC1540CMS8#PBF MC10E1651FNG MCP6544-EP MCP6541UT-I/LT

MCP6542T-E/MS MCP6542T-I/SN MCP6547T-EMS MCP6549-E/P